一种半导体器件及其制造方法、电子装置与流程

本申请涉及半导体,具体而言涉及一种半导体器件及其制造方法、电子装置。

背景技术:

1、随着技术的进步,半导体器件正在向小尺寸方向发展。一方面,随着半导体器件的沟槽宽度变小,可在同一衬底上制造出更多的器件,这降低了生产成本;另一方面,半导体器件的沟槽宽度减小引起沟槽的间距(pitch)也减小,沟槽(trench)的密度变大,半导体器件的电流密度变大,使半导体器件的电流能力得到提升。然而,沟槽(trench)密度变大会引起半导体器件内部的寄生电容增大,这导致了半导体器件的导通损耗大、开关恢复能力差。

2、因此,有必要提出一种新的半导体器件及其制造方法,以至少部分解决上述技术问题。

技术实现思路

1、在

技术实现要素:

部分中引入了一系列简化形式的概念,这将在具体实施方式部分中进一步详细说明。本申请的发明内容部分并不意味着要试图限定出所要求保护的技术方案的关键特征和必要技术特征,更不意味着试图确定所要求保护的技术方案的保护范围。

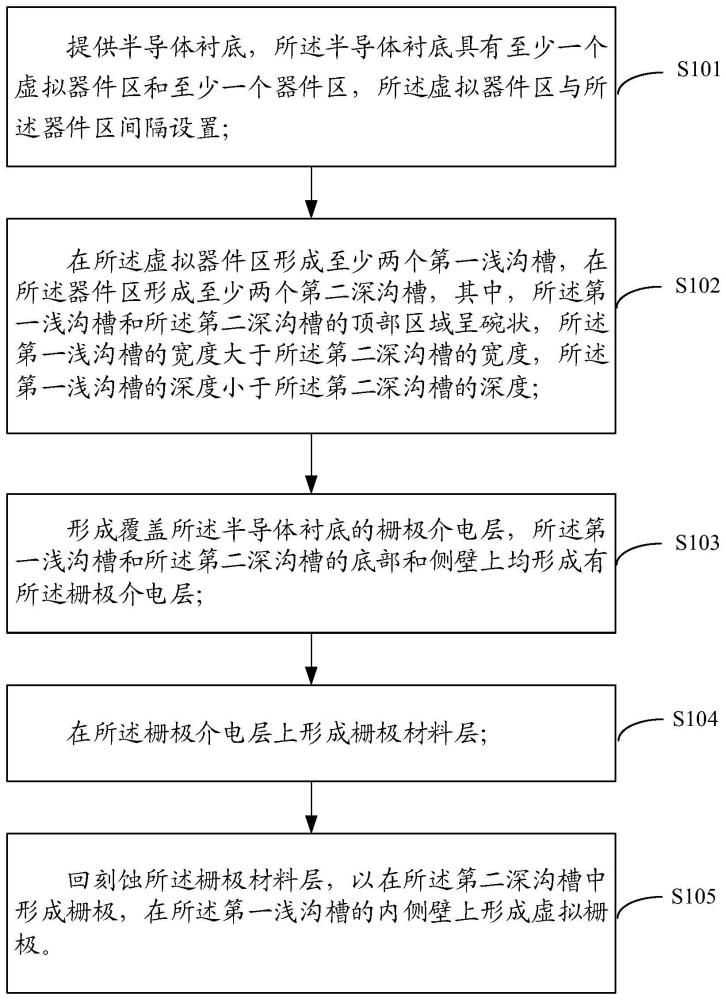

2、本申请提供了一种半导体器件的制造方法,包括以下步骤:提供半导体衬底,所述半导体衬底具有至少一个虚拟器件区和至少一个器件区,所述虚拟器件区与所述器件区间隔设置;在所述虚拟器件区形成至少两个第一浅沟槽,在所述器件区形成至少两个第二深沟槽,其中,所述第一浅沟槽和所述第二深沟槽的顶部区域呈碗状,所述第一浅沟槽的宽度大于所述第二深沟槽的宽度,所述第一浅沟槽的深度小于所述第二深沟槽的深度;形成覆盖所述半导体衬底的栅极介电层,所述第一浅沟槽和所述深沟槽的底部和内侧壁上均形成有所述栅极介电层;在所述栅极介电层上形成栅极材料层;回刻蚀所述栅极材料层,以在所述第二深沟槽中形成栅极,在所述第一浅沟槽的内侧壁上形成虚拟栅极。

3、示例性地,在所述虚拟器件区形成至少两个第一浅沟槽之后,在所述器件区形成至少两个第二深沟槽。

4、示例性地,在所述虚拟器件区形成至少两个第一浅沟槽,包括以下步骤:在所述半导体衬底上形成第一图案化的掩膜层,所述第一图案化的掩膜层包括第一图案窗口,所述第一图案窗口位于所述虚拟器件区;以所述第一图案化的掩膜层为掩膜,经由所述第一图案窗口,对所述半导体衬底进行各向同性刻蚀和各向异性刻蚀,以在所述虚拟器件区中形成至少两个所述第一浅沟槽。

5、示例性地,在所述器件区形成至少两个第二深沟槽,包括以下步骤:在所述半导体衬底上形成第二图案化的掩膜层,所述第二图案化的掩膜层包括第二图案窗口,所述第二图案窗口位于所述器件区,其中,所述第一图案窗口的宽度大于所述第二图案窗口的宽度;以所述第二图案化的掩膜层为掩膜,经由所述第二图案窗口,对所述半导体衬底进行各向同性刻蚀和各向异性刻蚀,以在所述器件区中形成至少两个第二深沟槽。

6、示例性地,回刻蚀所述栅极材料层,包括以下步骤:各向同性刻蚀所述第一浅沟槽的顶部区域中的所述栅极材料层,并且各向异性刻蚀所述第一浅沟槽的顶部区域以下的至少部分所述栅极材料层,使所述第一浅沟槽的至少部分底部露出,以在位于所述第一浅沟槽的内侧壁上形成所述虚拟栅极;各向同性刻蚀所述第二深沟槽的顶部区域中的所述栅极材料层,以在所述第二深沟槽的中形成所述栅极。

7、示例性地,在形成所述栅极以及所述虚拟栅极之后,还包括以下步骤:在所述器件区中相邻的所述第二深沟槽之间形成体区和源漏区;以及在所述虚拟器件区中相邻的所述第一浅沟槽之间形成体区。

8、示例性地,在形成所述体区以及所述源漏区之后,还包括以下步骤:在所述第一浅沟槽和所述第二深沟槽中形成层间介电层,其中,所述层间介电层表面与所述第一浅沟槽和所述第二深沟槽的顶部边缘平齐;刻蚀所述体区以及所述虚拟器件区与所述器件区之间的半导体衬底,以形成接触孔;填充所述接触孔以形成接触插塞;形成覆盖所述半导体衬底的金属互连层,其中,所述金属互连层与所述接触插塞电连接。

9、示例性地,在所述第一浅沟槽和所述第二深沟槽中形成层间介电层,包括以下步骤:在所述第一浅沟槽的顶部区域以及所述虚拟栅极之间填充所述层间介电层;以及在所述第二深沟槽的顶部区域填充所述层间介电层。

10、示例性地,在形成覆盖所述半导体衬底的金属互连层之后,还包括以下步骤:减薄所述半导体衬底背向所述金属互连层一侧的表面;以及在所述半导体衬底背向所述金属互连层一侧的表面上形成背面金属层。

11、本申请还提供了一种根据上述任一项的方法制造的半导体器件,包括:半导体衬底,所述半导体衬底中形成有至少一个虚拟器件区和至少一个器件区,所述虚拟器件区与所述器件区间隔设置,所述虚拟器件区包括至少两个第一浅沟槽,所述器件区包括至少两个第二深沟槽,其中,所述第一浅沟槽的宽度大于所述第二深沟槽的宽度,所述第一浅沟槽的深度小于所述第二深沟槽的深度,所述第一浅沟槽的顶部区域呈碗状,所述第二深沟槽的顶部区域呈碗状;栅极介电层,形成于所述第一浅沟槽和所述第二深沟槽的底部和内侧壁上;栅极,形成于所述第二深沟槽中;虚拟栅极,形成于所述第一浅沟槽的内侧壁上。本申请还提供一种电子装置,包括上述的半导体器件。

12、根据本申请提供的半导体器件的制造方法,分别在深宽比较大的第二深沟槽中形成栅极以及在深宽比较小的第一浅沟槽的内侧壁上形成虚拟栅极,与相关的深沟槽技术相比,该方法减小了虚拟器件区中沟槽的深度和密度,从而降低了器件内部的寄生电容和输入电容,进一步减少了器件的开关损耗和功耗,提高了器件的开关速度和恢复能力。

技术特征:

1.一种半导体器件的制造方法,其特征在于,包括以下步骤:

2.如权利要求1所述的方法,其特征在于,在所述虚拟器件区形成至少两个第一浅沟槽之后,在所述器件区形成至少两个第二深沟槽。

3.如权利要求2所述的方法,其特征在于,在所述虚拟器件区形成至少两个第一浅沟槽,包括以下步骤:

4.如权利要求3所述的方法,其特征在于,在所述器件区形成至少两个第二深沟槽,包括以下步骤:

5.如权利要求4所述的方法,其特征在于,回刻蚀所述栅极材料层,包括以下步骤:

6.如权利要求5所述的方法,其特征在于,在形成所述栅极以及所述虚拟栅极之后,还包括以下步骤:

7.如权利要求6所述的方法,其特征在于,在形成所述体区以及所述源漏区之后,还包括以下步骤:

8.如权利要求7所述的方法,其特征在于,在所述第一浅沟槽和所述第二深沟槽中形成层间介电层,包括以下步骤:

9.如权利要求8所述的方法,其特征在于,在形成覆盖所述半导体衬底的金属互连层之后,还包括以下步骤:

10.一种根据权利要求1至9任一项的方法制造的半导体器件,其特征在于,包括:

11.一种电子装置,其特征在于,包括如权利要求10所述的半导体器件。

技术总结

一种半导体器件及其制造方法、电子装置,该方法包括:提供半导体衬底,半导体衬底具有至少一个虚拟器件区和至少一个器件区,虚拟器件区与器件区间隔设置;在虚拟器件区形成至少两个第一浅沟槽,在器件区形成至少两个第二深沟槽,其中,所述第一浅沟槽和所述第二深沟槽的顶部区域呈碗状,第一浅沟槽的宽度大于第二深沟槽的宽度,第一浅沟槽的深度小于第二深沟槽的深度;形成覆盖半导体衬底的栅极介电层,第一浅沟槽和第二深沟槽的底部和侧壁上均形成有栅极介电层;在栅极介电层上形成栅极材料层;回刻蚀栅极材料层,以在第二深沟槽中形成栅极,在第一浅沟槽的内侧壁上形成虚拟栅极。该方法降低了器件内部的寄生电容,减少了器件的开关损耗和功耗。

技术研发人员:方田,汪旭东,王珏

受保护的技术使用者:绍兴中芯集成电路制造股份有限公司

技术研发日:

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!