一种隔离结构及其制作方法与流程

本发明属于半导体集成电路制造领域,涉及一种隔离结构及其制作方法。

背景技术:

1、功率ic(integrated circuit,简称集成电路)集成度提高是大势所趋,但是在提高集成电路集成度的过程中,集成电路中的器件与器件之间会产生互相干扰,且随着工作电压的增大,这种干扰会愈发严重,因此器件间隔离显得尤为重要。为了保证器件的集成度及器件之间的隔离效果,通常采用浅沟槽隔离结构来隔离集成电路中的器件,这种隔离结构中浅沟槽的深度通常不会超过1 μm,且需要占用大量面积,不能适应高集成度和高工作电压的工艺要求,在这种情况下,深沟槽隔离技术应运而生。

2、目前,市场上绝大多数深沟槽隔离结构中深沟槽的深度在20 μm以内,深宽比小于10,填充深沟槽的介质层中形成有较大的空隙,且深沟槽隔离结构通常是由单一的深沟槽填充介质层得到,介质层的填充效果较差,不能满足高集成度和超高压(大于100v)的工艺要求。

3、因此,急需寻找一种能够满足集成电路高集成度和超高压工艺要求的隔离结构。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种隔离结构及其制作方法,用于解决现有技术中深沟槽隔离结构不能满足高集成度和超高压工艺要求的问题。

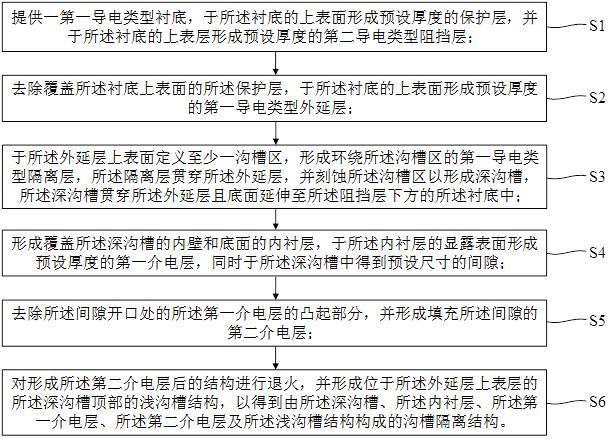

2、为实现上述目的及其他相关目的,本发明提供了一种隔离结构的制作方法,包括以下步骤:

3、提供一第一导电类型衬底,于所述衬底的上表面形成预设厚度的保护层,并于所述衬底的上表层形成预设厚度的第二导电类型阻挡层;

4、去除覆盖所述衬底上表面的所述保护层,于所述衬底的上表面形成预设厚度的第一导电类型外延层;

5、于所述外延层上表面定义至少一沟槽区,形成环绕所述沟槽区的第一导电类型隔离层,所述隔离层贯穿所述外延层,并刻蚀所述沟槽区以形成深沟槽,所述深沟槽贯穿所述外延层且底面延伸至所述阻挡层下方的所述衬底中;

6、形成覆盖所述深沟槽的内壁和底面的内衬层,于所述内衬层的显露表面形成预设厚度的第一介电层,同时于所述深沟槽中得到预设尺寸的间隙;

7、去除所述间隙开口处的所述第一介电层的凸起部分,并形成填充所述间隙的第二介电层;

8、对形成所述第二介电层后的结构进行退火,并形成位于所述外延层上表层的所述深沟槽顶部的浅沟槽结构,以得到由所述深沟槽、所述内衬层、所述第一介电层、所述第二介电层及所述浅沟槽结构构成的沟槽隔离结构。

9、可选地,形成所述阻挡层之后,形成所述外延层之前,还包括形成覆盖所述保护层上表面的牺牲层、对所述阻挡层进行退火及去除所述牺牲层的步骤。

10、可选地,形成所述隔离层的方法包括离子注入。

11、可选地,形成所述隔离层之后,形成所述深沟槽之前,还包括于所述衬底的上表面形成图案化的掩膜层的步骤。

12、可选地,形成所述深沟槽的方法包括博世刻蚀。

13、可选地,所述深沟槽的深度不小于20 μm。

14、可选地,所述深沟槽的深宽比不小于12。

15、可选地,形成所述第一介电层的方法包括高深宽比填充工艺;形成所述第二介电层的方法包括高深宽比填充工艺。

16、可选地,形成所述第二介电层之后,对形成所述第二介电层后的结构进行退火之前,还包括去除位于所述衬底上方的所述第一介电层与所述第二介电层的步骤。

17、可选地,所述浅沟槽结构包括浅沟槽及填充所述浅沟槽的填充层,所述浅沟槽位于所述外延层上表层的所述深沟槽的顶部,所述浅沟槽的开口尺寸不小于所述深沟槽的开口尺寸。

18、本发明还提供了一种隔离结构,包括:

19、第一导电类型衬底;

20、第二导电类型阻挡层,位于所述衬底的上表层;

21、第一导电类型外延层,堆叠于所述衬底的上表面;

22、沟槽隔离结构,包括至少一深沟槽、内衬层、第一介电层、第二介电层及浅沟槽结构,所述深沟槽贯穿所述外延层和所述阻挡层且底面延伸至所述阻挡层下方的所述衬底中,所述内衬层覆盖所述深沟槽的内壁及底面,所述第一介电层覆盖所述内衬层的显露表面,所述第二介电层填充所述深沟槽,且所述第一介电层包裹所述第二介电层的侧壁及底面,所述浅沟槽结构位于所述外延层上表层的所述深沟槽的顶部;

23、隔离层,环绕所述外延层中的所述深沟槽的侧壁且贯穿所述外延层。

24、如上所述,本发明的隔离结构及其制作方法通过对隔离结构的改进,于所述衬底的上表层形成所述阻挡层,于所述衬底的上表面形成预设厚度的所述外延层,再于所述外延层中形成贯穿所述外延层且环绕所述深沟槽侧壁的隔离层及底面延伸至所述衬底中的所述深沟槽,依次于所述深沟槽中形成材质均为氧化硅的所述内衬层、所述第一介电层及所述第二介电层,避免了氧化硅和其他填充性好但耐压性能不足的介电材料结合导致形成的填充所述深沟槽的填充层的耐压性能差,提升了隔离结构的耐压性能;通过所述深沟槽与所述外延层中环绕所述深沟槽的所述隔离层的结合,进一步提升了隔离结构的耐压性能;此外,通过于所述深沟槽的顶部形成位于所述外延层上表层的所述浅沟槽结构,提升了隔离结构顶部靠近高压源部分的耐压性能且对隔离结构的排布密度无影响,具有高度产业利用价值。

技术特征:

1.一种隔离结构的制作方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的隔离结构的制作方法,其特征在于:形成所述阻挡层之后,形成所述外延层之前,还包括形成覆盖所述保护层上表面的牺牲层、对所述阻挡层进行退火及去除所述牺牲层的步骤。

3.根据权利要求1所述的隔离结构的制作方法,其特征在于:形成所述隔离层的方法包括离子注入。

4.根据权利要求1所述的隔离结构的制作方法,其特征在于:形成所述隔离层之后,形成所述深沟槽之前,还包括于所述衬底的上表面形成图案化的掩膜层的步骤。

5.根据权利要求1所述的隔离结构的制作方法,其特征在于:形成所述深沟槽的方法包括博世刻蚀。

6.根据权利要求1所述的隔离结构的制作方法,其特征在于:所述深沟槽的深度不小于20 μm。

7.根据权利要求1所述的隔离结构的制作方法,其特征在于:所述深沟槽的深宽比不小于12。

8.根据权利要求1所述的隔离结构的制作方法,其特征在于:形成所述第一介电层的方法包括高深宽比填充工艺;形成所述第二介电层的方法包括高深宽比填充工艺。

9.根据权利要求1所述的隔离结构的制作方法,其特征在于:形成所述第二介电层之后,对形成所述第二介电层后的结构进行退火之前,还包括去除位于所述衬底上方的所述第一介电层与所述第二介电层的步骤。

10.根据权利要求1所述的隔离结构的制作方法,其特征在于:所述浅沟槽结构包括浅沟槽及填充所述浅沟槽的填充层,所述浅沟槽位于所述外延层上表层的所述深沟槽的顶部,所述浅沟槽的开口尺寸不小于所述深沟槽的开口尺寸。

11.一种隔离结构,其特征在于,包括:

技术总结

本申请提供一种隔离结构及其制作方法,该隔离结构包括衬底、阻挡层、外延层、沟槽隔离结构及隔离层,阻挡层位于衬底的上表层,沟槽隔离结构包括至少一深沟槽、内衬层、浅沟槽结构、第一介电层及第二介电层,深沟槽贯穿外延层和阻挡层且底面延伸至阻挡层下方的衬底中,内衬层覆盖深沟槽的内壁及底面,第一介电层覆盖内衬层的显露表面,第二介电层填充深沟槽,且第一介电层包裹第二介电层的侧壁及底面,浅沟槽结构位于外延层上表层的深沟槽的顶部;隔离层环绕外延层中的深沟槽的侧壁且贯穿外延层。本申请通过浅沟槽和深沟槽的结合及深沟槽与环绕深沟槽的隔离层的结合,提升了隔离结构的耐压能力且不影响隔离结构的排布密度。

技术研发人员:穆睿祥,杜宁乐,张日林,刘芳妹,廖纯贤,余勤旭

受保护的技术使用者:粤芯半导体技术股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!