JFET区源极接触的抑制栅源电压过冲的埋沟U槽SiCVDMOSFET结构的制作方法

本发明涉及sic vdmosfet结构改进,具体涉及jfet区源极接触的抑制栅源电压过冲的埋沟u槽sic vdmosfet结构。

背景技术:

1、sic mosfet器件具有高频低损耗的显著优势,在电动汽车、光伏逆变器和充电桩等领域有十分广泛的应用。然而,sic mosfet极快的开关速度使得器件在开通和关断过程中极易产生栅源电压过冲的问题,导致sic mos栅氧承受极高的电压应力,长期使用过程中易出现栅氧性能退化甚至栅极损坏的现象。为了抑制开关过程中栅源电压过冲的问题,通常采用增大栅极驱动电阻以降低开关速度和在栅源电极之间外接稳压二极管等方法。增大栅极驱动电阻虽然有效缓解了开关过程中的电压过冲问题,但较长的开关时间不仅增大了开关损耗,而且无法充分发挥出sic mosfet高速开关的性能优势。同样地,在栅源电极之间外接稳压二极管会增大栅源之间的电容,降低sic mosfet的开关速度。此外,由于外接稳压二极管通常为型号固定的商用器件,其稳压性能、寄生电容等通常无法直接和sic mosfet形成最佳匹配,严重限制了sic mosfet器件性能的充分发挥。图1和图2中展示了两种常用的抑制sic mosfet快速开关过程中出现电压过冲的方法。因此,现有也有将抑制栅源电压过冲而实现稳压的sic mosfet对自身结构进行改进,这一改进必然会影响到sic mosfet最直接性能标的“元胞尺寸”矛盾问题,由于加入的结构必然会增大单个重复元胞的尺寸,降低电流密度,因此基于上述一些列问题,目前对sic mosfet具有既能实现自身最佳匹配的抑制栅源电压过冲且单个重复元胞尺寸减小成为目前亟需解决的问题,此外,考虑到器件的性能方面,传统的vdmosfet器件,其体二极管主要由pn结组成,其开启电压相对较大。传统vdmosfet的crss也较大,这是由于栅极(g极)与漏极(d极)的正对面积较大。crss较大,直接导致器件的ciss、coss等参数较大,从而增加器件的开关损耗,故本专利提供了一种针对sic mosfet器件全方位的性能解决方案。

技术实现思路

1、有鉴于此,本发明的目的在于提供jfet区源极接触的抑制栅源电压过冲的埋沟u槽sic vdmosfet结构,通过在单个重复元胞内部利用天然的结构构建栅极和源极之间的单片集成n/p+2/polysi背靠背的钳位二极管,其一为n/p+2二极管,其二为p+2/polysi异质结二极管,以解决目前栅源电极在开关过程中因剧烈振荡而出现的过电压应力,并通过引入埋沟u槽使单个重复元胞的n型半导体区和p型半导体区的欧姆接触由横向变为纵向且同时将引入的n/p+2/polysi背靠背钳位二极管由横向变为纵向,同时还将横向的栅极合并省略用绝缘层,从而实现三合一多方位解决引入n/p+2/polysi背靠背钳位二极管带来尺寸增大问题,实现既能抑制开关栅源电压过冲和大幅度减少了单个重复元胞尺寸节省了源区面积,具有更大的电流密度,还通过将vdmosfet的jfet区顶端多晶硅栅分裂,降低g极与d极的正对面积,大幅降低碳化硅vdmosfet的crss,进一步大幅度将器件的开关损耗,在jfet区顶端采用肖特基接触,可以大幅度降低碳化硅mosfet器件的体二极管的开启电压,从而降低体二极管正向压降。

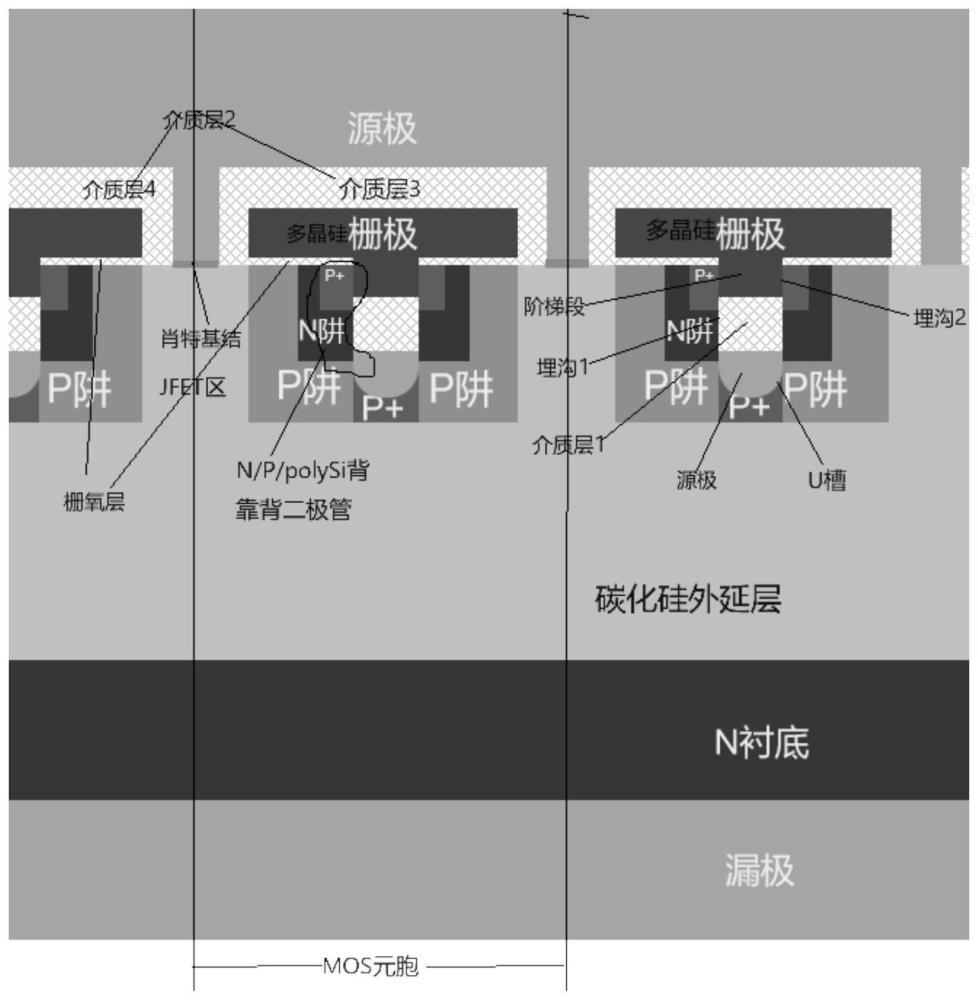

2、为解决以上技术问题,本发明提供jfet区源极接触的抑制栅源电压过冲的埋沟u槽sic vdmosfet结构,包括碳化硅外延层,所述碳化硅外延层顶部通过离子注入形成为呈井状p型半导体区的p阱,所述p阱等距排布在所述碳化硅外延层上,相邻所述p阱之间形成为jfet区,所述p阱顶部中部通过离子注入形成为呈井状n型半导体区的n阱,所述n阱顶部通过与所述p阱相同的极高浓度的离子注入形成为呈井状p型半导体区的p+2,所述p+2中部开凿有埋沟2,所述n阱上开凿有与所述埋沟2连通的埋沟1,所述埋沟1下部连通有u槽,所述u槽贯穿所述n阱并深入至所述p阱内,所述碳化硅外延层上淀积有连续一体的多晶硅栅极,使得sic vdmosfet结构的元胞之间的栅极合并省略侧面的横向介质层,所述多晶硅栅下端具有淀积入所述埋沟2内与所述p+2的欧姆接触的阶梯段,使得形成栅极侧的p+2/polysi异质结二极管,所述u槽内淀积有金属的源极,所述埋沟1内淀积有隔绝所述多晶硅栅极和所述源极的介质层1,所述源极与所述n阱和所述p阱同时接触,以形成源区的欧姆短接,还形成源极侧的n/p+2结二极管,使得sic vdmosfet结构中形成具有栅源之间纵向的n/p+2/polysi背靠背二极管;所述多晶硅栅极位于所述jfet区上的位置被打断以形成两段的所述多晶硅栅极,所述源极通过两段的所述多晶硅栅极与所述jfet区直接接触以形成肖特基结。

3、在一些实施例中优选地方案,相邻所述jfet区之间的形成有mos元胞,所述mos元胞为定义名称,为单位范围内重复的结构,其中,所述mos元胞包括局部的所述jfet区。

4、在一些实施例中优选地方案,所述多晶硅栅极下方具有栅氧层,所述栅氧层位于所述碳化硅外延层上除所述埋沟2以外的所有位置,所述多晶硅栅极上方淀积有介质层2,其中,所述介质层2与所述介质层1均为sio2,所述栅氧层也被所述肖特基结打断形成分别位于两段的所述多晶硅栅极下方,所述介质层也被打断并分别形成分别包裹两段的所述多晶硅栅极的介质层3和介质层4。

5、在一些实施例中优选地方案,所述埋沟2仅位于所述p+2内,所述埋沟1同时位于所述p+2和所述n阱内,所述u槽同时位于所述n阱和所述p阱内。

6、在一些实施例中优选地方案,所述埋沟1、埋沟2和所述u槽的横截面的宽度相同或不同。

7、在一些实施例中优选地方案,所述埋沟1、埋沟2和所述u槽至少或近似具有一条纵向的中心线。

8、在一些实施例中优选地方案,所述p阱内还通过相同极高浓度的离子注入形成为p型半导体区的p+1;所述p阱注入的离子为al离子或b离子,所述p+2和所述p+1注入为极高浓度的al离子或b离子;所述n阱为注入极高浓度的p离子或n离子。

9、在一些实施例中优选地方案,还包括位于所述碳化硅外延层下方的n衬底,所述n衬底下方具有漏极,所述多晶硅栅极的介质层2上方淀积有源极。

10、与现有技术相比,本发明的优点如下:

11、1、本发明的结构利用在单个重复元胞内部利用天然的结构构建栅极和源极之间的单片集成n/p+2/polysi背靠背的钳位二极管,其一为n/p+2二极管,其二为p+2/polysi异质结二极管,可以简洁高效实现在栅源电极之间集成背靠背的钳位二极管,以解决目前栅源电极在开关过程中因剧烈振荡而出现的过电压应力,并通过引入埋沟u槽使单个重复元胞的n型半导体区和p型半导体区的欧姆接触由横向变为纵向且同时将引入的n/p+2/polysi背靠背钳位二极管由横向变为纵向,同时还将横向的栅极合并省略用绝缘层,从而实现三合一多方位解决引入n/p+2/polysi背靠背钳位二极管带来尺寸增大问题,实现既能抑制开关栅源电压过冲和大幅度减少了单个重复元胞尺寸节省了源区面积,具有更大的电流密度,此外,在同一元胞结构中在jfet区引入肖特基接触端,在体二极管接正向电压时,肖特基接触形成的肖特基结会率先开启,体二极管导通,在电压持续增加时,pn结二极管开启,电阻进一步降低。原有pn结部分可以作为现有体二极管的浪涌注入部分。此种结构相当于将原有结构的体二极管从pn结二极管变成了具有抗浪涌电流功能的肖特基二极管,大幅度提升了器件的体二极管特性,将jfet区的多晶硅栅分开,减少了栅极覆盖面积,直接降低了器件的crss,进一步降低了器件的ciss、coss、qg、eon、eoff等一系列电学参数值,使器件性能更加优异,从而从各个方面保护器件,全方位提升器件的实用性。

12、2、在单片集成n/p+2/polysi结构时,仅需在sic mosfet芯片版图设计中,将部分元胞结构中的栅极多晶硅直接和p接触形成异质结二极管,并将p旁边的n阱上的欧姆接触和源极金属短接,既可在版图局部形成n/p+2/polysi结构,实际实现方法简便可行。

13、3、可同时实现sic mosfet栅源电极之间正向和反向过电压保护。

14、4、通过结构或工艺优化,易于实现sic mosfet与集成n/p+2/polysi结构性能的最佳匹配。

15、5、本发明的单片集成结构工艺实现和sic mosfet完全兼容,实现成本低,性能提升高。

16、6、本发明的结构将片上集成n/p+2/polysi结构集成进p-well中,大幅度减少了单个重复元胞尺寸,节省了源区面积,具有更大的电流密度,另外,通过引入埋沟u槽,实现第一将新引入的n/p+2/polysi结构由横向转为纵向布置,第二将n阱和p阱的与源区的同时欧姆接触横向转为纵向,第三n/p+2/polysi结构与n阱和p阱的与源区的同时欧姆接触横向转为纵向特殊结构又构造了多晶硅栅极必然的合并,从而三方面幅度减小了单个重复元胞尺寸。

- 还没有人留言评论。精彩留言会获得点赞!