肖特基二极管与MOSFET的集成的制作方法

本发明涉及一种器件,该器件包括在掩埋栅格材料结构上集成的功率mosfet和续流肖特基二极管,以实现最佳的电压阻断性能。

背景技术:

1、一些碳化硅(sic)功率mosfet能够商购获得,并且有许多专利出版物公开了sic功率mosfet架构。这些架构包括p-n体二极管,其能够用作反向并联续流二极管。然而,开关频率受限于该体二极管的速度,因为这是一个慢少数载流子器件。p-n体二极管还具有高阈值电压的缺点,导致高导电和开关损耗。与~1v的sic肖特基整流器相比,sic p-n体二极管具有~3v的高势垒,前者与si整流器相当。

2、为了加速sic mosfet的切换,诸如肖特基二极管或jbs二极管的快速整流器应当用作反向并联二极管。

3、使用外部快速整流器是实现有效的反向并联续流二极管的最简单方法。然而,快速整流器的额定电流需要高于mosfet p-n体二极管的额定电流,以确保主电流路径通过快速整流器,用于负漏极电流。该解决方案具有三个主要缺点。第一个缺点是大区域的外部快速整流器。该外部二极管会引入较大的寄生输出电容并限制开关频率。第二个缺点是需要引线键合,这会降低连接的可靠性并增加寄生电感。第三个缺点是系统成本高。

4、us 6,979,863公开了一种具有集成的jbs二极管的vdmosfet。这种设计的主要好处在于两个器件都集成在同一芯片上。然而,由于这些器件只能并联集成,并且不能共享相同的单位单元和漂移层区域,所以限制了集成。如us 6,979,863中所公开的,例如在附图中,jbs二极管的最小尺寸接近10μm。因此,mosfet和jbs二极管在导通时不会共享漂移区,并且输出寄生电容方面的增益很低。此外,mosfet和jbs二极管工艺的共享工艺步骤受到限制。因此,该解决方案不会导致相当大的成本降低。

5、us 5,693,569公开了这样一种设计,该设计包括通过刻蚀沉积有肖特基金属的额外沟槽来将sic沟槽mosfet和肖特基二极管集成在一起。该特征在us 5,693,569的图1至图3中以20表示。与美国专利6,979,863中的vdmosfet方案相比,该设计具有更高的集成密度。然而,应当使栅极沟槽屏蔽于高电场,以避免器件早期损坏。类似的双沟槽设计现今已在商业上用于沟槽mosfet,但是二极管沟槽包括p-n结而不是肖特基接触件,以使栅极沟槽屏蔽于高电场。该p-n结还用作体二极管。

6、在现有技术中,存在具有结合在mosfet中的肖特基区域的已知的器件,例如参见w.sung等人,“developing one-chip integration of 1.2kv sic mosfet and jbs diode(jbsfet)”,ieee transactions on industrial electronics,第64卷,第10期,2017年10月,以及w.sung等人,monolithically integrated 4h-sic mosfet and jbs diode(jbsfet)using a single ohmic/schottky process scheme,ieee electron deviceletter,第37卷,第12期,2016年12月。然而,在一个实施例中,jbs二极管和mosfet被放置在器件芯片区域的不同部分上,因此不共享相同的漂移层区域。在另一个实施例中,jbs二极管和mosfet不与掩埋栅格结合。

7、总之,本领域需要提供一种改进的器件。

技术实现思路

1、本发明的一个目的是消除现有技术中的至少一些缺点,并且提供一种改进的续流肖特基二极管,该续流肖特基二极管其在掩埋栅格材料结构的顶部上与mosfet集成。

2、本发明的实施例提供了用于将肖特基二极管和dmosfet或沟槽mosfet单片集成在掩埋栅格材料结构上的方法和技术方案。

3、经过广泛研究,已经发现可以通过如下来获得优点:通过利用掩埋栅格(bg)作为结势垒,以通过单独的层来屏蔽阻断时的电场,而将功率mosfet和肖特基二极管集成。

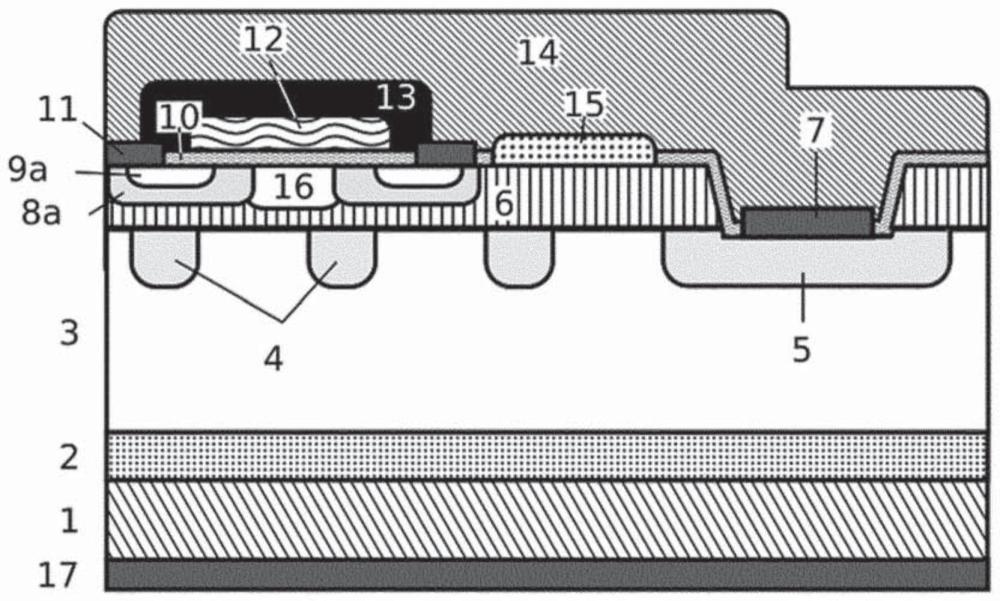

4、在第一方面中,提供了一种器件,其包括以下部分:

5、n型衬底(1),

6、n型漂移外延层,其在所述n型衬底(1)上,

7、n型外延再生层,其在所述n型漂移外延层(3)上,

8、p型栅格层(4),其包括在所述n型漂移外延层(3)中的栅格,并且与所述n型外延再生层(6)接触,

9、p型馈电层(5),其在n型漂移外延层(3)中,并且与所述n型外延再生层(6)接触,所述栅格层(4)与所述p型馈电层(5)连接,欧姆接触件(7),其至少部分地被应用在所述p型馈电层(5)上,p阱区(8a,8b),

10、n+源极区(9a,9b),

11、栅极氧化物(10),

12、源极欧姆接触件(11),

13、所述欧姆接触件(7)经由金属化层(14)连接至所述源极欧姆接触件(11),所述p阱区(8a,8b)被布置为使得其与所述n型外延再生层(6)、所述n+源极区(9a,9b)、所述栅极氧化物(10)和所述源极欧姆接触件(11)接触,

14、所述n+源区(9a,9b)被布置为使得其与所述p阱区(8a,8b)、所述栅极氧化层(10)和所述源极欧姆接触件(11)接触,

15、栅极接触件(12),

16、隔离层(13),其用于使栅极接触件(12)与金属化层(14)区域隔离,

17、所述栅极氧化物(10)与所述p阱区(8a,8b)、所述n+源极区(9a,9b)、所述栅极接触件(12)和所述隔离层(13)接触,

18、所述栅极氧化物(10)选择性地与所述n型外延再生层(6)和源极欧姆接触件(11)接触,

19、肖特基接触件(15)

20、所述金属化层(14)至少部分地被应用在所述器件上并且与所述肖特基接触件(15)接触,而所述肖特基接触件(15)与所述n型外延再生层(6)接触,

21、漏极欧姆接触件和金属化件(17)。

22、在所附权利要求中限定了其他方面和实施例,在此通过引用将其具体地并入本文中。

23、该设计的一个优点在于,整个表面区域可用于mosfet和肖特基二极管结构,而无需牺牲用于特殊结构的区域,以降低与其他材料的表面或界面处的电场。mosfet和肖特基二极管可以彼此非常接近地放置在同一单位单元中,因此共享同一漂移层。续流肖特基二极管可以与所述mosfet集成在几乎与单独mosfet芯片相同的区域上。与利用两个单独的芯片相比,在某些实施例中,总区域因此可以减少几乎50%。

24、另一个优点在于,最高的电场出现在接近bg区域的结的漂移层(3)中,因此漂移层(3)不受肖特基二极管或mosfet设计规则的限制。因此,根据这种用于pin整流器的穿通设计,可以减小厚度并增加漂移层(3)的掺杂浓度。这将导致器件的更高的电导率和更低的导通电阻,而不会影响电压阻断性能。除了掩埋栅格,不需要其他措施来处理接近肖特基接触件(15)或栅极氧化物(10)的高电场,从而可以自由设计和放置器件的各个部分。

25、另一个优点在于,与当前的可用设计(例如美国专利6,979,863中公开的设计,其中p通道(p阱)是屏蔽区域的一部分)不同,共享的漂移层和单独的bg屏蔽块使mosfet和肖特基二极管器件在器件尺寸、mosfet与肖特基二极管区域之比、p沟道(p阱)和jfet沟道的掺杂浓度和厚度、以及mosfet和肖特基二极管单元的布置方面具有更大的自由度,而无论其栅格如何对齐。

26、另一个优点是,由于电容要低得多而集成器件能够以比具有两个器件的标准配置更高的频率操作,并且避免了分开的芯片之间的连接中的寄生电感。

27、当电流在mosfet与肖特基二极管之间切换时,与两芯片解决方案相比,集成芯片的加热更加均匀。

28、另一个优点在于,由于将肖特基二极管的正向压降更低,与利用mosfet体二极管作为续流二极管相比,损耗更低。另外,避免了双极性退化。

29、与其他集成解决方案相比,单位单元中的肖特基二极管的大小不受泄漏电流的限制,因此可以根据应用规范进行设计。通过p型馈电层(5)的设计,可以进一步限定p型栅格层(4)中的pn二极管在高电流下的激活点。p型栅格层(4)也可以称为掩埋栅格或bg。p型馈电层(5)也可以仅称为“馈电件”。

30、bg确保在阻断模式下mosfet和肖特基二极管的雪崩耐量。

31、另一个优点在于,没有或很少有额外的光刻步骤来集成mosfet和肖特基二极管。因此,与两芯片解决方案相比,成本更低。

- 还没有人留言评论。精彩留言会获得点赞!