封装结构及其形成方法与流程

本发明涉及集成电路制造,尤其涉及一种封装结构及其形成方法。

背景技术:

1、qfn(quad flat no-leads package,方形扁平无引脚封装)是一种常用的封装方式。qfn封装方式具有电和热性能良好、体积小、重量轻、开发成本低等优点,适合应用在手机、数码相机、pda以及其他便携小型电子设备的高密度印刷电路板上。qfn封装结构包括基岛和环绕基岛的外周设置的一圈管脚。但是,这种qfn封装结构由于受限于切割的影响,管脚数量少而且排列较为稀疏,从而限制了qfn封装结构集成度的进一步提高。而且,由于管脚数量较少且排列较为稀疏,在连接所述管脚与芯片时需要打线的长度较长且难度较大,并导致qfn封装结构内部电路复杂,从而降低了qfn封装结构的产率。另外,qfn封装结构通过pcb(printed circuit board,印刷电路板)散热,散热量有限,易导致热量在qfn封装结构内部的聚集,从而易对所述qfn封装结构造成损伤,最终导致qfn封装结构性能的下降。

2、因此,如何简化封装结构的制造工艺,提高封装结构的产品良率,是当前亟待解决的技术问题。

技术实现思路

1、本发明提供一种封装结构及其形成方法,用于简化封装结构的制造工艺,提高封装结构的产品良率。

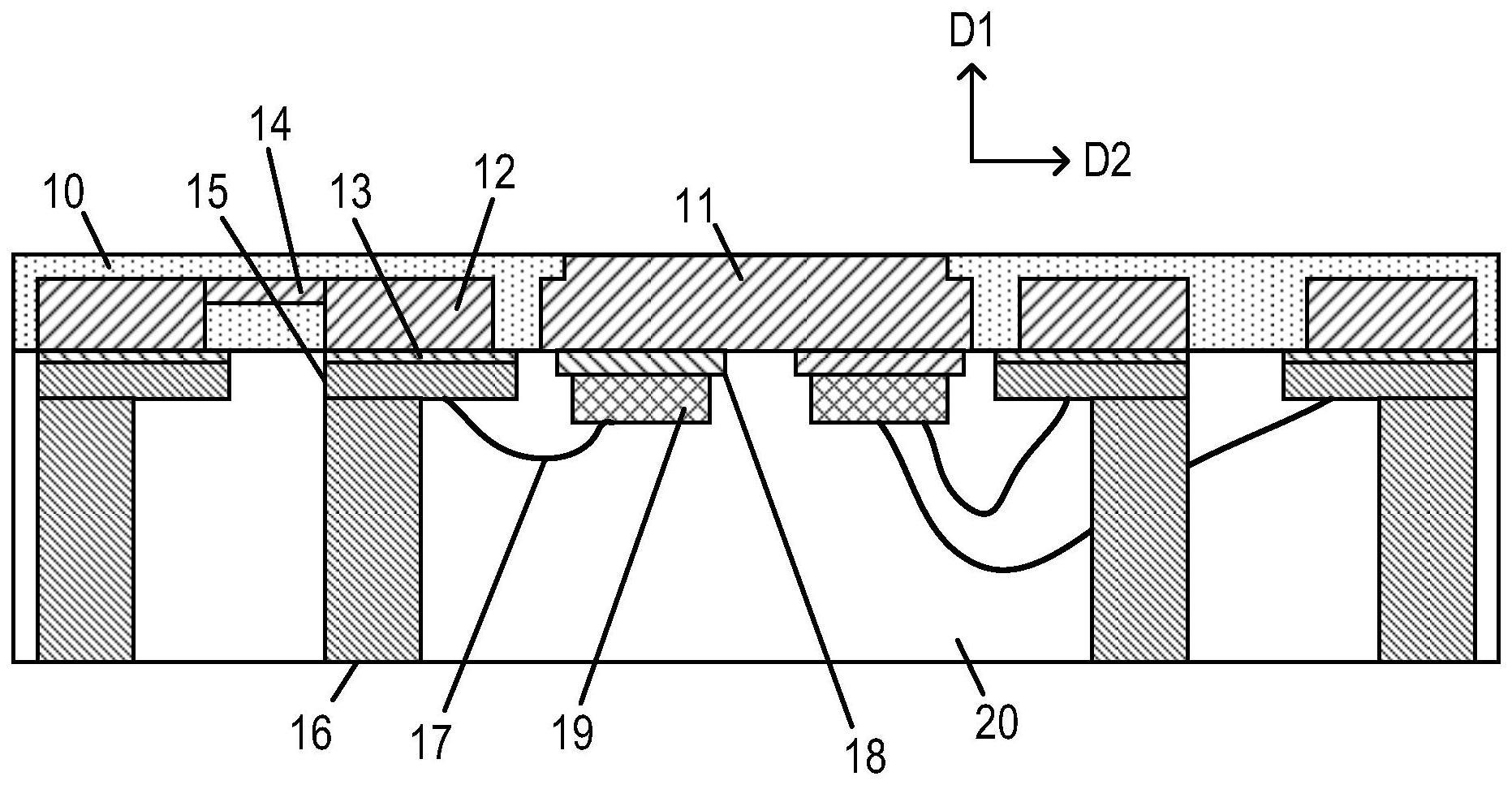

2、根据一些实施例,本发明提供了一种封装结构,包括:

3、框架,包括第一塑封层和沿第一方向贯穿所述第一塑封层的基岛,所述框架包括沿所述第一方向相对分布的上表面和下表面;

4、芯片,位于所述框架的所述下表面上且与所述基岛电连接;

5、管脚结构,位于所述框架的下表面上,所述管脚结构包括至少一个管脚圈,每个所述管脚圈包括围绕所述芯片的外周分布的多个管脚,所述管脚与所述芯片电连接;

6、第二塑封层,覆盖于所述框架的所述下表面上,且所述第二塑封层覆盖所述芯片和所述管脚结构。

7、在一些实施例中,当所述管脚结构为多个管脚圈时,多个所述管脚圈依次嵌套。

8、在一些实施例中,所述框架内还包括:

9、连接结构,包括依次嵌套的多个连接圈,多个所述连接圈与多个所述管脚圈一一对应,每个所述连接圈包括围绕所述基岛的外周分布的多个连接岛,每个所述连接圈中的多个所述连接岛和与其对应的所述管脚圈中的多个所述管脚一一对应连接。

10、在一些实施例中,所述连接结构中还包括连接件,所述连接件位于相邻的两个所述连接圈之间,用于电连接相邻的两个所述连接圈中的所述连接岛。

11、在一些实施例中,所述管脚包括:

12、焊接部,位于所述框架的下表面上,且与所述连接岛焊接;

13、引出部,位于所述焊接部背离所述框架的一侧,所述引出部与所述焊接部电连接,且所述焊接部至少沿第二方向的宽度大于所述引出部沿所述第二方向的宽度,所述第二方向与所述第一方向相交。

14、在一些实施例中,还包括:

15、连接线,位于所述第二塑封层内,所述连接线的一端与所述芯片电连接、另一端与所述焊接部沿所述第二方向突出于所述引出部的部分电连接。

16、在一些实施例中,对于任意相邻的两圈所述管脚圈,其中一个所述管脚圈中的所述管脚与另一个所述管脚圈中的所述管脚错开设置。

17、在一些实施例中,还包括:

18、切割道,所述切割道沿所述第一方向连续贯穿所述框架和所述第二塑封层,且所述切割道的边缘与所述管脚结构中位于最外圈的所述管脚圈中的所述管脚之间具有间隙。

19、在一些实施例中,还包括:

20、散热结构,位于所述框架的所述上表面上,且所述散热结构在所述框架的所述上表面上的投影至少覆盖部分的所述基岛。

21、根据另一些实施例,本发明还提供了一种封装结构的形成方法,包括如下步骤:

22、形成框架,所述框架包括第一塑封层和沿第一方向贯穿所述第一塑封层的基岛,所述框架包括沿所述第一方向相对分布的上表面和下表面;

23、于所述框架的下表面上连接管脚结构和芯片,所述芯片与所述基岛电连接,所述管脚结构包括至少一个管脚圈,每个所述管脚圈包括围绕所述芯片的外周分布的多个管脚,所述管脚与所述芯片电连接;

24、于所述框架的下表面上形成第二塑封层,所述第二塑封层覆盖所述芯片和所述管脚结构。

25、在一些实施例中,当所述管脚结构为多个管脚圈时,多个所述管脚圈依次嵌套。

26、在一些实施例中,形成框架的具体步骤包括:

27、形成基岛和连接结构,所述连接结构包括依次嵌套的多个连接圈,每个所述连接圈包括围绕所述基岛的外周分布的多个连接岛;

28、形成塑封所述基岛和所述连接结构的所述第一塑封层,形成包括所述基岛、所述连接结构和所述第一塑封层的所述框架,所述连接岛和所述基岛均暴露于所述框架的下表面。

29、在一些实施例中,于所述框架的下表面上连接管脚结构和芯片的具体步骤包括:

30、于所述框架的下表面连接与多个所述连接圈一一对应的多个所述管脚圈,每个所述管脚圈中包括和与其对应的所述连接圈中的多个所述连接岛一一对应连接的多个所述管脚;

31、于所述框架的下表面上连接所述基岛和所述芯片。

32、在一些实施例中,于所述框架的下表面连接与多个所述连接圈一一对应的多个所述管脚圈的具体步骤包括:

33、采用冲切工艺形成与所述连接结构中的多个所述连接岛一一对应的多个所述管脚,所述管脚包括相互电连接的焊接部和引出部,所述焊接部至少沿第二方向的宽度大于所述引出部沿所述第二方向的宽度,所述第二方向与所述第一方向相交;

34、将多个管脚的所述焊接部一一焊接于多个所述连接岛上,使得所述引出部与所述连接岛沿所述第一方向位于所述焊接部的相对两侧。

35、在一些实施例中,于所述框架的下表面上连接管脚结构和芯片之后,还包括如下步骤:

36、形成连接线,所述连接线的一端与所述芯片电连接、另一端与所述焊接部沿所述第二方向突出于所述引出部的部分电连接。

37、在一些实施例中,所述框架中包括沿第二方向间隔排布的多个所述基岛,且所述第一塑封层连续塑封多个所述基岛,多个所述芯片分别与多个所述基岛连接,多个相互独立所述管脚结构一一设置于多个所述芯片的外周,以一个所述基岛、与所述基岛连接的所述芯片和围绕所述芯片外周分布的一个所述管脚结构作为一个封装单元;

38、于相邻所述封装单元之间定义切割道,所述切割道的边缘和与其相邻的所述封装单元中位于最外圈的所述管脚圈中的所述管脚之间具有间隙;

39、沿所述切割道切割,形成多个独立的所述封装单元,每个独立的所述封装单元作为一个封装结构。

40、在一些实施例中,还包括如下步骤:

41、形成散热结构于所述框架的上表面上,所述散热结构在所述框架的所述上表面上的投影至少覆盖部分的所述基岛。

42、本发明提供的封装结构及其形成方法,于芯片外周设置了至少一个管脚圈,且每个所述管脚圈包括围绕所述芯片的外周分布的多个管脚,所述管脚与所述芯片电连接,从而增加了所述封装结构中管脚的数量和密集度,一方面,有助于降低所述芯片与所述管脚的连接难度,例如芯片与管脚之间连接线的长度,从而简化封装结构的制造工艺,提高封装结构的制造良率;另一方面,管脚数量增加,能够实现更多的输入/输出,并有助于提高所述封装结构的集成度。而且,本发明中基岛贯穿框架中的第一塑封层,所述芯片和所述管脚结构均位于所述框架的下表面,从而能够在所述框架的上表面对所述基岛进行散热,减少了所述基岛内部的热量聚集,从而改善了所述封装结构的散热性能。

- 还没有人留言评论。精彩留言会获得点赞!