接触沟槽形成方法和半导体器件与流程

本申请实施例涉及半导体,具体涉及一种接触沟槽形成方法和半导体器件。

背景技术:

1、在半导体器件中,前后段一般通过接触孔进行连接,而部分器件如功率场效应管(powermos)和整合驱动型场效芯片(drmos),其前后段的主要连接结构为接触沟槽。

2、然而,目前在制备高深宽比的接触沟槽的过程中,所形成的接触沟槽底部的关键尺寸较小,无法满足实际需求。

技术实现思路

1、本申请实施例提供了一种接触沟槽形成方法和半导体器件,可以增大接触沟槽底部的关键尺寸。

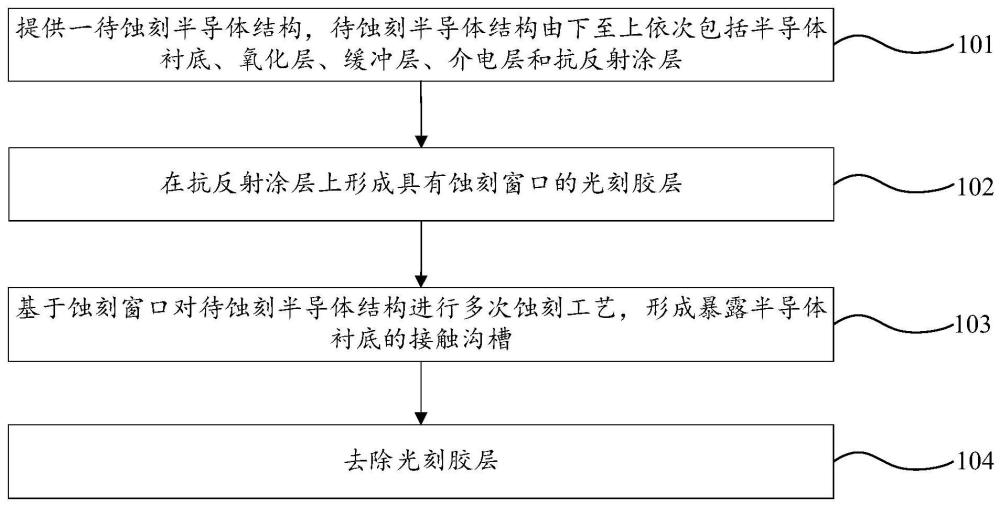

2、第一方面,本申请实施例提供了一种接触沟槽形成方法,包括:

3、提供一待蚀刻半导体结构,所述待蚀刻半导体结构由下至上依次包括半导体衬底、氧化层、缓冲层、介电层和抗反射涂层;

4、在所述抗反射涂层上形成具有蚀刻窗口的光刻胶层;

5、基于所述蚀刻窗口对所述待蚀刻半导体结构进行多次蚀刻工艺,形成暴露所述半导体衬底的接触沟槽;

6、去除所述光刻胶层。

7、在本申请实施例提供的接触沟槽形成方法中,所述基于所述蚀刻窗口对所述待蚀刻半导体结构进行多次蚀刻工艺,形成暴露所述半导体衬底的接触沟槽,包括:

8、基于所述蚀刻窗口对所述抗反射涂层进行第一蚀刻处理,形成贯穿所述抗反射涂层的第一子接触沟槽;

9、基于所述第一子接触沟槽对所述介电层进行第二蚀刻处理,以形成贯穿所述介电层的第二子接触沟槽;

10、基于所述第二子接触沟槽对所述缓冲层进行第三蚀刻处理,以形成贯穿所述缓冲层的第三子接触沟槽;

11、基于所述第三子接触沟槽对所述氧化层进行第四蚀刻处理,以形成贯穿所述氧化层的第四子接触沟槽;

12、基于所述第四子接触沟槽对所述半导体衬底进行第五蚀刻处理,以形成深入所述半导体衬底的接触沟槽。

13、在本申请实施例提供的接触沟槽形成方法中,所述第一蚀刻处理、所述第二蚀刻处理、所述第三蚀刻处理、所述第四蚀刻处理和所述第五蚀刻处理的蚀刻参数均不相同。

14、在本申请实施例提供的接触沟槽形成方法中,所述第二蚀刻处理的蚀刻参数包括反应腔压力、高频射频功率、低频射频功率、第一反应气体流量、第二反应气体流量和第三反应气体流量;

15、其中,所述反应腔压力为20mt~40mt、所述高频射频功率为1000w~2000w、所述低射频功率为1500w~3000w、所述第一反应气体流量为20sccm~30sccm、所述第二反应气体流量为25sccm~35sccm、所述第三反应气体流量为1100sccm~1200sccm。

16、在本申请实施例提供的接触沟槽形成方法中,所述第一反应气体为c4f6,所述第二反应气体为o2,所述第三反应气体为ar。

17、在本申请实施例提供的接触沟槽形成方法中,在所述在所述抗反射涂层上形成具有蚀刻窗口的光刻胶层之后,所述基于所述蚀刻窗口对所述待蚀刻半导体结构进行多次蚀刻工艺,形成暴露所述半导体衬底的接触沟槽之前,还包括:

18、在所述光刻胶层表面以及所述蚀刻窗口的侧壁形成保护层。

19、在本申请实施例提供的接触沟槽形成方法中,所述第二蚀刻处理为过蚀刻处理。

20、在本申请实施例提供的接触沟槽形成方法中,所述第三蚀刻处理为过蚀刻处理。

21、在本申请实施例提供的接触沟槽形成方法中,所述第四蚀刻处理为过蚀刻处理。

22、第二方面,本申实施例提供了一种半导体器件,所述半导体器件采用上述的接触沟槽形成方法形成。

23、综上所述,本申请实施例提供的接触沟槽形成方法包括:提供一待蚀刻半导体结构,所述待蚀刻半导体结构由下至上依次包括半导体衬底、氧化层、缓冲层、介电层和抗反射涂层;在所述抗反射涂层上形成具有蚀刻窗口的光刻胶层;基于所述蚀刻窗口对所述待蚀刻半导体结构进行多次蚀刻工艺,形成暴露所述半导体衬底的接触沟槽;去除所述光刻胶层。本方案通过将待蚀刻半导体结构的蚀刻工艺分为多次,可以减少接触沟槽内部发生轮廓改变,降低接触沟槽的宽度变化。也即,本方案可以增加接触沟槽底部的关键尺寸。

技术特征:

1.一种接触沟槽形成方法,其特征在于,包括:

2.如权利要求1所述的接触沟槽形成方法,其特征在于,所述基于所述蚀刻窗口对所述待蚀刻半导体结构进行多次蚀刻工艺,形成暴露所述半导体衬底的接触沟槽,包括:

3.如权利要求2所述的接触沟槽形成方法,其特征在于,所述第一蚀刻处理、所述第二蚀刻处理、所述第三蚀刻处理、所述第四蚀刻处理和所述第五蚀刻处理的蚀刻参数均不相同。

4.如权利要求1~3任一项所述的接触沟槽形成方法,其特征在于,所述第二蚀刻处理的蚀刻参数包括反应腔压力、高频射频功率、低频射频功率、第一反应气体流量、第二反应气体流量和第三反应气体流量;

5.如权利要求4所述的接触沟槽形成方法,其特征在于,所述第一反应气体为c4f6,所述第二反应气体为o2,所述第三反应气体为ar。

6.如权利要求1所述的接触沟槽形成方法,其特征在于,在所述在所述抗反射涂层上形成具有蚀刻窗口的光刻胶层之后,所述基于所述蚀刻窗口对所述待蚀刻半导体结构进行多次蚀刻工艺,形成暴露所述半导体衬底的接触沟槽之前,还包括:

7.如权利要求2所述的接触沟槽形成方法,其特征在于,所述第二蚀刻处理为过蚀刻处理。

8.如权利要求2所述的接触沟槽形成方法,其特征在于,所述第三蚀刻处理为过蚀刻处理。

9.如权利要求2所述的接触沟槽形成方法,其特征在于,所述第四蚀刻处理为过蚀刻处理。

10.一种半导体器件,其特征在于,所述半导体器件采用如权利要求1~9任一项所述的接触沟槽形成方法形成。

技术总结

本申请实施例公开了一种接触沟槽形成方法和半导体器件,该半导体器件的制造方法包括提供一待蚀刻半导体结构,待蚀刻半导体结构由下至上依次包括半导体衬底、氧化层、缓冲层、介电层和抗反射涂层;在抗反射涂层上形成具有蚀刻窗口的光刻胶层;基于蚀刻窗口对待蚀刻半导体结构进行多次蚀刻工艺,形成暴露半导体衬底的接触沟槽;去除光刻胶层。本方案可以增加接触沟槽底部的关键尺寸。

技术研发人员:陈峰,陈勇树,李志宏,阮杰平

受保护的技术使用者:粤芯半导体技术股份有限公司

技术研发日:

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!