一种晶圆级超薄四边无引脚芯片封装方法及芯片封装结构与流程

本发明涉及半导体封装,更具体涉及一种晶圆级超薄四边无引脚芯片封装方法及芯片封装结构。

背景技术:

1、随着科技的进步和市场对更小型、更高性能的电子产品的需求增加,芯片封装小型化成为必然趋势。小型化的芯片封装可以实现更高的集成度,减小电子产品的尺寸和重量,提高产品的便携性和可用性。小型化的封装可以提供更好的散热性能,帮助芯片在紧凑的空间中更有效地散热,降低温度,提高稳定性和可靠性。并且小型化的芯片封装有助于实现高集成度,将更多的功能和组件集成到一个小尺寸的芯片中。这样可以减少电路板的复杂度,提高系统性能,并降低产品成本。

2、wlcsp封装是一种新兴的将晶圆级和芯片尺寸封装合为一体的封装技术,是芯片还在晶圆上时就对芯片进行直接封装,最后再将晶圆切成单个芯片。 与传统封装相比,晶圆级封装具有尺寸小,高传输速度,高密度连接,生产周期短,生产效率高,工艺成本低的优点。

3、目前的wlcsp封装主要由背面保护层(硅片或涂胶层)、芯片厚度、重布线金属层、凸点下金属层和植球5层结构组成,其中背面保护层为可选项,因此产品最小封装厚度可以达到为200um,其中芯片厚度100um,重布线金属层20um,凸点下金属层5um,植球75um。

4、而近年来随着电子产品的不断升级换代,智能手机、5g、ai等新兴市场对封装技术提出的更高的要求,wlcsp封装作为一种新兴的技术也在不断进行优化和改良,以顺应电子产品日益轻薄短小、低成本的发展需求。

5、因此,如何对现有wlcsp封装进行工艺和结构优化是一直以来亟需攻克的难题。

技术实现思路

1、为了解决上述问题,本发明提供了一种晶圆级超薄四边无引脚芯片封装方法及芯片封装结构,可以实现最小的封装尺寸和封装厚度,最小可达到128um厚度的封装结构。

2、根据本发明的一个方面,提供了一种晶圆级超薄四边无引脚芯片封装方法,该方法包括如下步骤:

3、s1、提供载体晶圆,将相同或者不同的来料晶圆切割成单颗芯片,并将芯片正面倒装在载体晶圆上;并在芯片背面设置塑封层,形成重构晶圆;

4、重构晶圆上来自相同或者不同来料晶圆上的单颗芯片可以根据实际设计调整芯片之间的间距,这比来料晶圆上的芯片间距相对更大,也具有更多的设计空间,因此,重构晶圆方便构造单位面积更大,输入输出(i/o)更多的芯片封装成品。

5、s2、在重构晶圆的塑封层表面设置支撑晶圆后,解键合载体晶圆;

6、s3、倒置重构晶圆,分别在单颗芯片正面形成与芯片压区相连的至少一层再钝化层、至少一层再布线金属层、绝缘层和矩形金属柱,实现芯片的互联;顶层所述绝缘层覆盖顶层再布线金属层。

7、矩形金属柱的上表面高于顶层绝缘层的上表面;矩形金属柱比顶层绝缘层设置的高,方便后续将芯片焊接到基板上。绝缘层厚度范围在0-40um,芯片需要与pcb、基板、框架等结构封装在一起,如果矩形金属柱低于绝缘层,rdl会有产生裂纹的风险,且绝缘层会与pcb等封装结构紧密相连,会有焊接不良的风险存在;因此,矩形金属柱的上表面需要高于顶层绝缘层的上表面,以此来增加焊接面积,提高焊接性能,有利于芯片与其余封装结构的传输效率并且会降低空洞的出现。

8、与矩形金属柱连接的顶层再布线金属层的尺寸均大于对应单颗芯片的尺寸;所述矩形金属柱对称或不对称分布于顶层再布线金属层的四周边缘,且所述矩形金属柱部分或完全覆盖重构晶圆的切割道;所述矩形金属柱部分或完全覆盖位于切割道上方的顶层绝缘层;

9、所述矩形金属柱包括凸点下金属层,并在凸点下金属层上镀锡,形成镀锡层,镀锡层的厚度为8-20um;

10、s4、沿切割道切割重构晶圆,形成四边无引脚的单颗芯片封装结构,所述芯片封装结构侧壁有部分裸露的矩形金属柱。

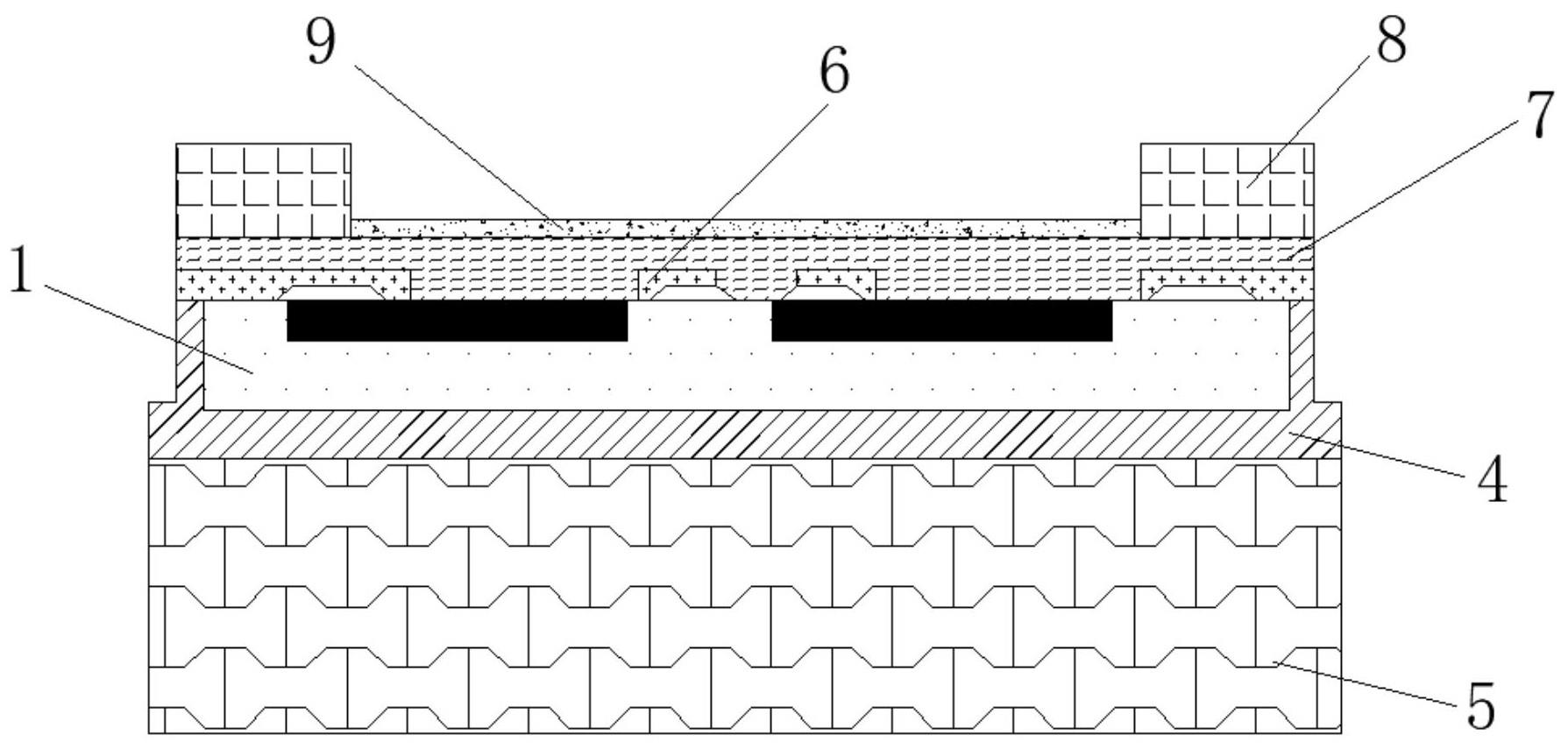

11、在一些实施方式中,步骤s1中,先在载体晶圆贴覆临时键合膜后,再将芯片逐个倒装在载体晶圆上。

12、在一些实施方式中,步骤s1中,塑封层为采用塑封料进行注塑工艺形成或者采用abf膜进行层压方式形成。

13、在一些实施方式中,步骤s3中,镀锡过程中电镀液的整平剂浓度为30%-80%。通过电镀液的整平剂浓度的调整,使得矩形金属柱的平整度更平。

14、在一些实施方式中,步骤s3中,在重构晶圆的芯片上方涂覆光刻胶,用掩膜版进行光刻或激光工艺,开出图形开口,形成再钝化层;

15、再次涂上光阻层,用掩膜版进行光刻或激光工艺,开出金属层图形开口;在金属层图形开口内电镀,形成再布线金属层;

16、或者,采用相同方法增加多层再钝化层和再布线金属层,实现多层再布线金属层互连结构。

17、在一些实施方式中,步骤s4中,在切割前,在芯片边缘处设置定位突起。该定位突起可以是任意图形,定位突起的设置不仅有利于后续芯片与基板的焊接,还有利于划片时区分芯片的边界。

18、在一些实施方式中,芯片封装结构侧壁呈阶梯结构。使得单颗芯片封装结构的侧壁便于侧面爬锡,可直观地通过侧面爬锡高度来判断产品与pcb的焊接效果,保证其封装质量,减少焊接缺陷,提高产品的可靠性与稳定性。

19、另一方面,本发明还公开采用上述方法制备而成的芯片封装结构,该芯片封装结构包括自下而上设置的支撑晶圆、塑封层、芯片、再钝化层、再布线金属层和矩形金属柱,再布线金属层的尺寸大于芯片的尺寸;矩形金属柱对称或不对称分布于再布线金属层的四周边缘,且矩形金属柱部分或完全覆盖支撑晶圆的切割道。

20、与现有技术相比,本发明的有益效果是:

21、本发明采用了一种晶圆级超薄四边无引脚芯片封装方法,通过优化矩形金属柱的结构和分布位置,实现了整个芯片封装结构厚度的优化;

22、矩形金属柱的结构是在凸点下金属层电镀适量厚度的锡(8um-20um),使得整个封装体厚度可以达到128um,封装结构高度相对传统的wlcsp封装优化了36%。镀锡层8um-20um厚度为最适宜的镀锡厚度,低于8um会导致易焊性不良,高于20um后不会有更优的焊接效果,因此出于成本及易焊性考虑,最佳的镀锡厚度为8-20um;保证晶圆级测试时,探针与芯片金属压区接触的稳定性;也保证了芯片封装结构后续与基板焊接时,焊接牢度更高,同时不会产生空洞等质量问题。

23、矩形金属柱的分布位置也不同于传统的wlcsp封装中植球的分布,传统的wlcsp封装中植球位置为芯片的中间,且为阵列式分布,当芯片往基板上安装的时候二者的结合情况无法直接观测,进而对技术人员判断芯片封装的可靠性造成技术障碍,而且存在金属球高度不一致影响芯片和基板的结合强度的问题。为解决该技术问题,本发明中矩形金属柱的分布位置参考类qfn的结构设计,将矩形金属柱对称地分布在芯片四周(包括切割道的部分)位置,便于封装;根据实际需要,矩形金属柱也可以不对称地分布在芯片四周;芯片封装结构侧壁有部分裸露的矩形金属柱,可直观地通过侧面爬锡高度来判断产品与pcb的焊接效果,保证其封装质量,减少焊接缺陷,提高产品的可靠性与稳定性。

24、本发明可根据芯片上的再布线金属层提高芯片间互联密度和解决高密度异质集成,实现芯片尺寸小、轻薄化、高引脚、高速度等电子封装的发展趋势。

- 还没有人留言评论。精彩留言会获得点赞!