薄膜晶体管的制作方法

本发明的实施方式涉及半导体基板及显示装置。

背景技术:

1、作为显示装置,例如已知电泳显示装置。在电泳显示装置中,在开关元件中使用薄膜晶体管。通过增大薄膜晶体管的沟道宽度,从而能够增加流经薄膜晶体管的电流量。

技术实现思路

1、本实施方式提供能利用多个电流路进行驱动的半导体基板和显示装置。

2、一实施方式的半导体基板具备:

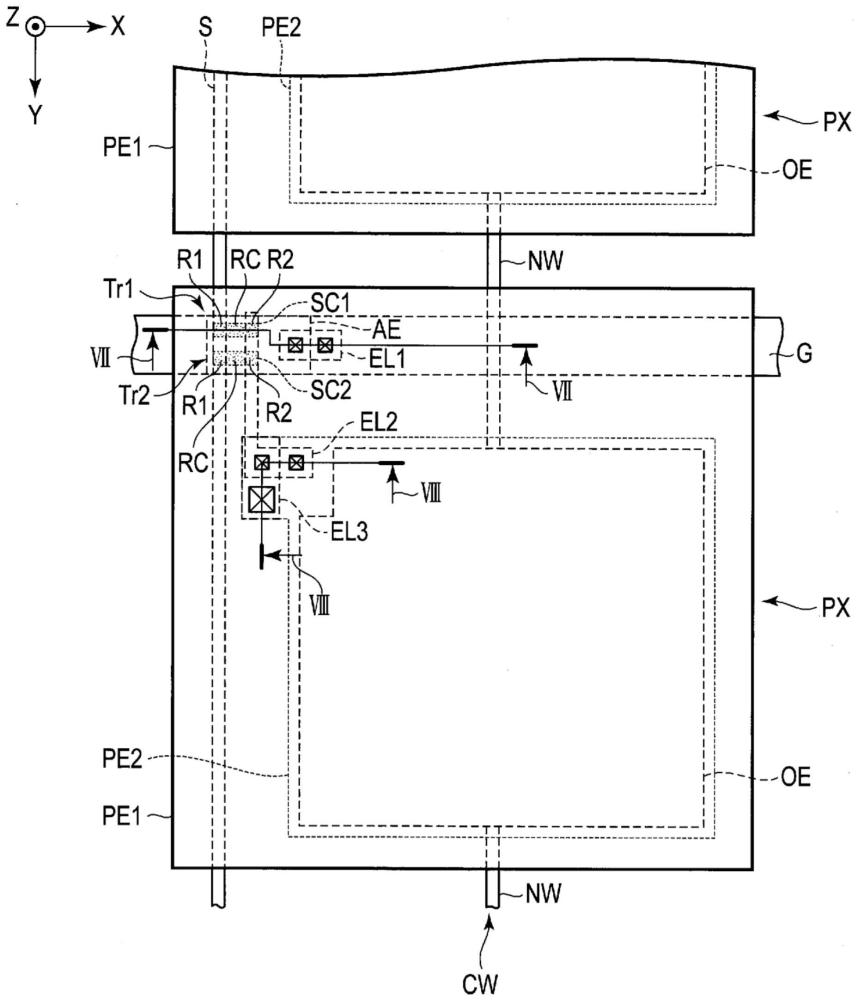

3、第一基材;栅极线,位于所述第一基材的上方;源极线,位于所述第一基材的上方;绝缘膜,位于所述栅极线的上方,并位于所述源极线的下方;第一像素电极,位于所述第一基材、所述栅极线以及所述源极线的上方;以及第一晶体管和第二晶体管,位于所述第一基材的上方,并在所述源极线与所述第一像素电极之间并联地电连接,所述第一晶体管的第一半导体层和所述第二晶体管的第二半导体层分别具有与所述源极线电连接的第一区域、与所述第一像素电极电连接的第二区域、以及所述第一区域与所述第二区域之间的沟道区域,所述第一半导体层和所述第二半导体层与第一表面接触,所述第一表面是所述绝缘膜的所述源极线侧的面,所述第一半导体层和所述第二半导体层各自的所述沟道区域的整体与所述栅极线重叠。

4、另外,一实施方式的显示装置具备:

5、半导体基板,其具备:第一基材;栅极线,位于所述第一基材的上方;源极线,位于所述第一基材的上方;绝缘膜,位于所述栅极线的上方,并位于所述源极线的下方;第一像素电极,位于所述第一基材、所述栅极线以及所述源极线的上方;以及第一晶体管和第二晶体管,位于所述第一基材的上方,并在所述源极线与所述第一像素电极之间并联地电连接;对置基板,其具备与所述第一像素电极相对的第二基材、和位于所述第二基材与所述第一像素电极之间并与所述第一像素电极相对的对置电极;以及显示功能层,位于所述第一像素电极与所述对置电极之间,在所述第一像素电极与所述对置电极之间施加的电压施加于所述显示功能层,所述第一晶体管的第一半导体层和所述第二晶体管的第二半导体层分别具有与所述源极线电连接的第一区域、与所述第一像素电极电连接的第二区域、以及所述第一区域与所述第二区域之间的沟道区域,所述第一半导体层和所述第二半导体层与第一表面接触,所述第一表面是所述绝缘膜的所述源极线侧的面,所述第一半导体层和所述第二半导体层各自的所述沟道区域的整体与所述栅极线重叠。

6、本技术包括如下技术方案:

7、(1)半导体基板,具备:

8、第一基材;

9、栅极线,其位于所述第一基材的上方;

10、源极线,其位于所述第一基材的上方;

11、绝缘膜,其位于所述栅极线的上方,并位于所述源极线的下方;

12、第一像素电极,其位于所述第一基材、所述栅极线以及所述源极线的上方;以及

13、第一晶体管和第二晶体管,位于所述第一基材的上方,并在所述源极线与所述第一像素电极之间并联地电连接,

14、所述第一晶体管的第一半导体层和所述第二晶体管的第二半导体层分别具有与所述源极线电连接的第一区域、与所述第一像素电极电连接的第二区域、以及所述第一区域与所述第二区域之间的沟道区域,

15、所述第一半导体层和所述第二半导体层与第一表面接触,所述第一表面是所述绝缘膜的所述源极线侧的面,

16、所述第一半导体层和所述第二半导体层各自的所述沟道区域的整体与所述栅极线重叠。

17、(2)上述(1)所述的半导体基板,其中,

18、所述第一半导体层和所述第二半导体层分别在所述栅极线延伸的方向上具有长轴,

19、所述第一半导体层和所述第二半导体层的整体与所述栅极线重叠。

20、(3)上述(2)所述的半导体基板,其中,

21、所述栅极线的宽度大于所述第一半导体层的短轴的长度与所述第二半导体层的短轴的长度之和。

22、(4)上述(3)所述的半导体基板,其中,

23、所述第一半导体层和所述第二半导体层在所述栅极线的宽度方向上排列。

24、(5)上述(1)所述的半导体基板,其还具备:

25、第二像素电极,其位于所述第一基材与所述第一像素电极之间,并与所述第一像素电极电连接;和

26、电容电极,其位于所述第一像素电极与所述第二像素电极之间,并分别与所述第一像素电极和所述第二像素电极静电电容耦合,

27、其中,在俯视时,所述电容电极的整体位于所述第一像素电极的内侧且位于所述第二像素电极的内侧。

28、(6)上述(5)所述的半导体基板,其还具备:

29、其他电容电极,位于与所述电容电极一起夹着所述栅极线的位置;和

30、连接布线,其将所述电容电极与所述其他电容电极连接,

31、其中,所述源极线与所述栅极线交叉,

32、所述连接布线与所述栅极线交叉,不与所述源极线交叉。

33、(7)上述(6)所述的半导体基板,其中,

34、所述栅极线和所述第二像素电极用相同材料形成,并位于同一层,

35、所述源极线、所述电容电极、所述其他电容电极以及所述连接布线用相同材料形成,并位于同一层,

36、所述电容电极、所述其他电容电极以及所述连接布线一体地形成。

37、(8)上述(5)所述的半导体基板,其还具备:

38、其他电容电极,位于与所述电容电极一起夹着所述源极线的位置;和

39、连接布线,其将所述电容电极与所述其他电容电极连接,

40、其中,所述源极线与所述栅极线交叉,

41、所述连接布线与所述源极线交叉,不与所述栅极线交叉。

42、(9)上述(1)所述的半导体基板,其还具备第二像素电极和电容电极,所述第二像素电极位于所述第一基材与所述第一像素电极之间,

43、其中,所述源极线与所述栅极线交叉,并位于第一域与第二域的边界线上,

44、所述第一半导体层的所述第二区域和所述沟道区域位于所述第一域,

45、所述第二半导体层的所述第二区域和所述沟道区域位于所述第二域,

46、所述第二像素电极具有:

47、第一区段,位于所述第一域并与所述第一像素电极电连接;和

48、第二区段,位于所述第二域并与所述第一像素电极电连接,

49、所述电容电极具有:

50、第一电容电极,在所述第一域中位于所述第一像素电极与所述第一区段之间,并分别与所述第一像素电极和所述第一区段静电电容耦合;

51、第二电容电极,在所述第二域中位于所述第一像素电极与所述第二区段之间,并分别与所述第一像素电极和所述第二区段静电电容耦合;以及

52、交叉电极,与所述源极线交叉,并将所述第一电容电极与所述第二电容电极电连接。

53、(10)上述(9)所述的半导体基板,其还具备:

54、其他电容电极,与所述第一电容电极相邻;

55、第三电容电极,位于与所述第二电容电极相邻、并与所述其他电容电极一起夹着所述电容电极的位置;

56、连接布线,将所述第一电容电极与所述其他电容电极连接;以及

57、其他连接布线,将所述第二电容电极与所述第三电容电极连接,

58、其中,所述连接布线和所述其他连接布线分别不与所述栅极线交叉,且不与所述源极线交叉。

59、(11)上述(1)所述的半导体基板,其中,

60、将所述第一半导体层和所述第二半导体层各自的所述沟道区域中的沟道长度和沟道宽度分别设为l和w时,

61、w/l≤0.75。

62、(12)上述(11)所述的半导体基板,其中,

63、所述第一半导体层和所述第二半导体层分别用氧化物半导体形成。

64、(13)上述(1)所述的半导体基板,其还具备辅助栅电极,所述辅助栅电极与所述栅极线电连接并与所述栅极线一起夹着所述第一半导体层和所述第二半导体层,

65、其中,在俯视时,所述辅助栅电极至少与所述第一半导体层和所述第二半导体层双方的所述沟道区域的整体重叠。

66、(14)显示装置,其具备:

67、半导体基板,其具备:第一基材;栅极线,其位于所述第一基材的上方;源极线,其位于所述第一基材的上方;绝缘膜,其位于所述栅极线的上方,并位于所述源极线的下方;第一像素电极,其位于所述第一基材、所述栅极线以及所述源极线的上方;以及第一晶体管和第二晶体管,位于所述第一基材的上方,并在所述源极线与所述第一像素电极之间并联地电连接;

68、对置基板,其具备与所述第一像素电极相对的第二基材、和位于所述第二基材与所述第一像素电极之间并与所述第一像素电极相对的对置电极;以及

69、显示功能层,其位于所述第一像素电极与所述对置电极之间,在所述第一像素电极与所述对置电极之间施加的电压施加于所述显示功能层,

70、所述第一晶体管的第一半导体层和所述第二晶体管的第二半导体层分别具有与所述源极线电连接的第一区域、与所述第一像素电极电连接的第二区域、以及所述第一区域与所述第二区域之间的沟道区域,

71、所述第一半导体层和所述第二半导体层与第一表面接触,所述第一表面是所述绝缘膜的所述源极线侧的面,

72、所述第一半导体层和所述第二半导体层各自的所述沟道区域的整体与所述栅极线重叠。

73、(15)上述(14)所述的显示装置,其中,

74、所述显示功能层是电泳层。

- 还没有人留言评论。精彩留言会获得点赞!