一种超薄模块封装结构及其方法与流程

本发明申请属于半导体封装,尤其涉及一种超薄模块封装结构及其方法。

背景技术:

1、芯片封装的意义重大,获得一颗ic芯片要经过从设计到制造漫长的流程,然而一颗芯片相当小且薄,如果不在外施加保护,会被轻易的刮伤损坏,此外,因为芯片的尺寸微小,如果不用一个较大尺寸的外壳,将不易安置在电路板上,所以需要使用到封装技术,封装有着安放、固定、密封、保护芯片和增强电热性能的作用,而且还是沟通芯片内部世界与外部电路的桥梁,芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印制电路板上的导线与其他器件建立连接,因此,封装对集成电路起着重要的作用。

2、对于模块类的芯片封装,是在芯片上集成其他器件,这种整合器件的超薄封装常用于消费类电子,一般这种消费类电子整体的厚度要求为1mm以下,但由于存在器件公差,器件公差很难控制,超薄封装时,器件最大公差时,器件顶部往往达不到安全的塑封料覆盖,容易导致封装体打标无安全厚度,造成废料,塑封料覆盖不足使得封装体上表面强度不足,容易出现封装体顶面冒锡或者顶部封装料鼓包,导致产品不合格,所以在器件公差下覆盖安全打标厚度的包封料并同时达到超薄封装要求,成为亟待解决的问题。

3、故,设计一种超薄模块封装结构及其方法,来解决上述技术问题。

技术实现思路

1、为解决上述现有技术中如何在器件公差下覆盖安全打标厚度的包封料并同时达到超薄封装要求的问题,本发明申请提供了一种超薄模块封装结构及其方法。

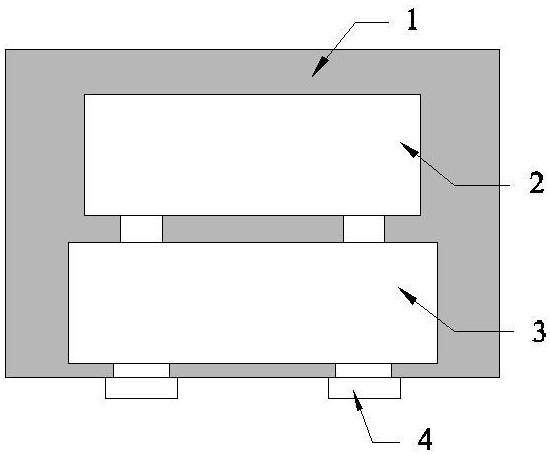

2、为实现上述目的,本发明申请提出的一种超薄模块封装结构,包括封装体,所述封装体内部包封有器件和基材,所述器件堆叠在基材上方并与基材电性连接,所述器件上表面至封装体顶面的高度≥产品顶面包封料安全覆盖高度,以同时保证打标质量和超薄封装的要求。

3、进一步,所述基材是内部包封芯片或线路的包封结构,器件通过焊接方式堆叠在基材上方,器件通过焊接部位与基材电性连接。

4、进一步,所述封装体底面暴露有外管脚,该外管脚与基材电性连接。

5、进一步,所述产品顶面包封料安全覆盖高度是器件到产品顶部满足安全打标的包封料厚度。

6、进一步,所述产品顶面包封料安全覆盖高度≥80μm。

7、一种超薄模块封装方法,包括以下步骤:

8、器件堆叠步骤:将器件堆叠在基材上,并实现器件与基材的电性连接;

9、整体包封步骤:将堆叠后的器件和基材整体一体包封并固化,成为封装体;

10、研磨步骤:研磨顶部的包封料,研磨后的封装体整体高度=最终产品的设计高度-产品顶面包封料安全覆盖高度;

11、筛选步骤:扫描筛选研磨后的封装体顶面,暴露器件的封装体判定为不合格品,不暴露器件的封装体判定为合格品,合格品进行续流;

12、再次包封步骤:继续将研磨后的封装体顶面包封,包封厚度为产品顶面包封料安全覆盖高度,整体达到最终产品的需求高度。

13、进一步的,所述器件堆叠步骤中,基材是内部包封芯片或线路的包封结构,器件通过焊接方式堆叠在基材上方,器件通过焊接部位与基材电性连接。

14、进一步的,所述整体包封步骤中,封装体底面暴露有外管脚,该外管脚与基材电性连接。

15、进一步的,所述研磨步骤中,产品顶面包封料安全覆盖高度是器件到产品顶部满足安全打标的包封料厚度。

16、进一步的,所述研磨步骤中,产品顶面包封料安全覆盖高度≥80μm。

17、本发明申请:通过初次包封后研磨产品顶面包封料安全覆盖高度,并筛选及时剔除研磨后暴露器件的不合格品,减小器件公差造成不良品的概率,控制整体良率,再包封产品顶面包封料安全覆盖高度,在满足打标质量的要求下,包封料覆盖厚度足够,包封料的压力足够,不容易出现冒锡或鼓包的情况,同时可以实现超薄封装。

技术特征:

1.一种超薄模块封装结构,包括封装体,所述封装体内部包封有器件和基材,所述器件堆叠在基材上方并与基材电性连接,其特征在于,所述器件上表面至封装体顶面的高度≥产品顶面包封料安全覆盖高度,以同时保证打标质量和超薄封装的要求。

2.根据权利要求1所述的超薄模块封装结构,其特征在于,所述基材是内部包封芯片或线路的包封结构,器件通过焊接方式堆叠在基材上方,器件通过焊接部位与基材电性连接。

3.根据权利要求2所述的超薄模块封装结构,其特征在于,所述封装体底面暴露有外管脚,该外管脚与基材电性连接。

4.根据权利要求1所述的超薄模块封装结构,其特征在于,所述产品顶面包封料安全覆盖高度是器件到产品顶部满足安全打标的包封料厚度。

5.根据权利要求4所述的超薄模块封装结构,其特征在于,所述产品顶面包封料安全覆盖高度≥80μm。

6.一种超薄模块封装方法,其特征在于,包括以下步骤:

7.根据权利要求6所述的超薄模块封装方法,其特征在于,所述器件堆叠步骤中,基材是内部包封芯片或线路的包封结构,器件通过焊接方式堆叠在基材上方,器件通过焊接部位与基材电性连接。

8.根据权利要求7所述的超薄模块封装方法,其特征在于,所述整体包封步骤中,封装体底面暴露有外管脚,该外管脚与基材电性连接。

9.根据权利要求6所述的超薄模块封装方法,其特征在于,所述研磨步骤中,产品顶面包封料安全覆盖高度是器件到产品顶部满足安全打标的包封料厚度。

10.根据权利要求9所述的超薄模块封装方法,其特征在于,所述研磨步骤中,产品顶面包封料安全覆盖高度≥80μm。

技术总结

本发明申请公开了一种超薄模块封装结构及其方法,包括封装体,所述封装体内部包封有器件和基材,所述器件堆叠在基材上方并与基材电性连接,所述器件上表面至封装体顶面的高度≥产品顶面包封料安全覆盖高度,以同时保证打标质量和超薄封装的要求,所述基材是内部包封芯片或线路的包封结构,器件通过焊接方式堆叠在基材上方,器件通过焊接部位与基材电性连接,所述封装体底面暴露有外管脚,该外管脚与基材电性连接,所述产品顶面包封料安全覆盖高度是器件到产品顶部满足安全打标的包封料厚度,本申请在满足打标质量的要求下,包封料覆盖厚度足够,包封料的压力足够,不容易出现冒锡或鼓包的情况,同时可以实现超薄封装。

技术研发人员:张光耀

受保护的技术使用者:合肥矽迈微电子科技有限公司

技术研发日:

技术公布日:2024/1/25

- 还没有人留言评论。精彩留言会获得点赞!