晶圆键合方法及半导体结构与流程

本公开涉及集成电路制造,特别是涉及一种晶圆键合方法及半导体结构。

背景技术:

1、对于晶圆键合工艺,顶部晶圆一定要先减薄到指定厚度。然后进行背面图形化工艺, 即通过光刻和刻蚀工艺, 在顶部晶圆背面加工出指定的图形和结构需要用到对准标记来进行晶圆。

2、目前现有的对准标记是在芯片的键合覆盖区域内,执行形成键合层工艺后,原硅片上的对准标记和图形都会被覆盖,光刻机无法识别现有的对准标记,从而停止光刻工艺,并中止产品流片。

技术实现思路

1、基于此,有必要针对上述背景技术中的问题,提供一种晶圆键合方法及半导体结构,避免对准标记被覆盖导致无法晶圆曝光的问题,提高生产效率。

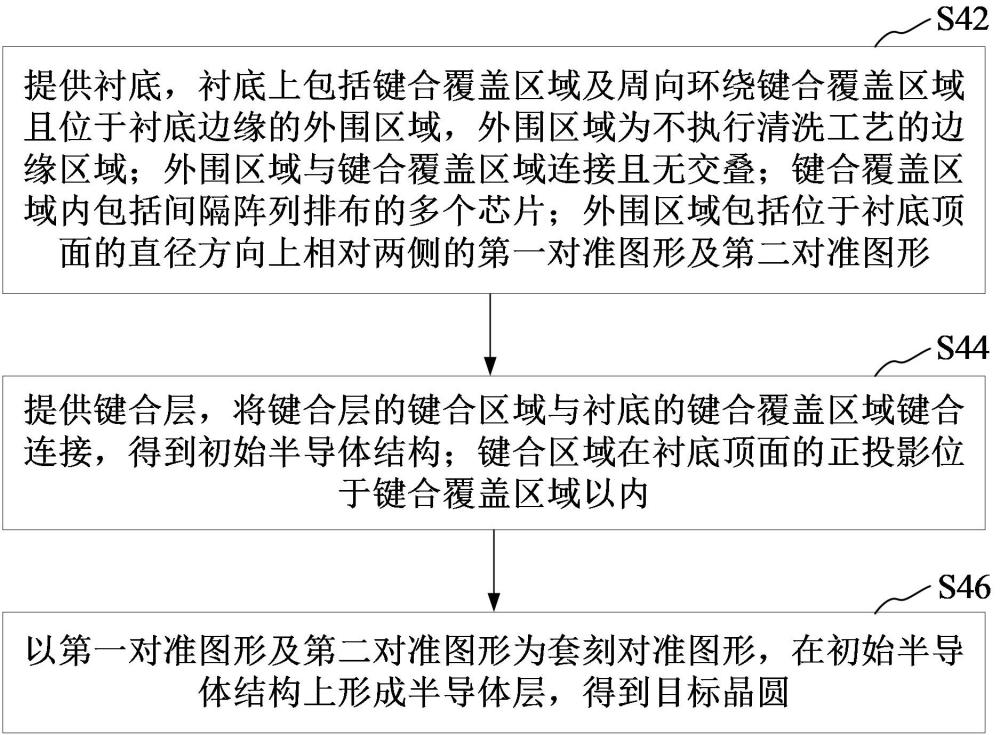

2、为实现上述目的及其他相关目的,本公开的一方面提供一种晶圆键合方法,包括提供衬底,衬底上包括键合覆盖区域及周向环绕键合覆盖区域且位于衬底边缘的外围区域,外围区域为不执行清洗工艺的边缘区域;外围区域与键合覆盖区域连接且无交叠;键合覆盖区域内包括间隔阵列排布的多个芯片;外围区域包括位于衬底顶面的直径方向上相对两侧的第一对准图形及第二对准图形;提供键合层,将键合层的键合区域与衬底的键合覆盖区域键合连接,得到初始半导体结构;键合区域在衬底顶面的正投影位于键合覆盖区域以内;以第一对准图形及第二对准图形为套刻对准图形,在初始半导体结构上形成半导体层,得到目标晶圆。

3、上述实施例中的晶圆键合方法,通过提供衬底,衬底上包括键合覆盖区域及周向环绕键合覆盖区域且位于衬底边缘的外围区域,外围区域为不执行清洗工艺的边缘区域;外围区域与键合覆盖区域连接且无交叠;键合覆盖区域内包括间隔阵列排布的多个芯片;外围区域包括位于衬底顶面的直径方向上相对两侧的第一对准图形及第二对准图形;将键合覆盖区域和含有对准图形的区域区分,避免在执行键合工艺后对准图形被覆盖,从而避免出现套刻无法对准的情况;通过提供键合层,将键合层的键合区域与衬底的键合覆盖区域键合连接,得到初始半导体结构;键合区域在衬底顶面的正投影位于键合覆盖区域以内;保证晶圆键合完整;以第一对准图形及第二对准图形为套刻对准图形,在初始半导体结构上形成半导体层,得到目标晶圆,对准图形正常显现,未被键合层覆盖,保证键合工艺正常进行,提高生产效率。目前相关的晶圆键合方法,将对准标记置于芯片的键合覆盖区域内,执行键合层覆盖后,原硅片上的对准标记和图形都会被覆盖,光刻机无法识别现有的对准标记,从而停止光刻工艺,并中止产品流片。本公开实施例提供的晶圆键合方法,通过在衬底上设置键合覆盖区域及周向环绕键合覆盖区域且位于衬底边缘的外围区域,设置外围区域为不执行清洗工艺的边缘区域,键合覆盖区域内包括间隔阵列排布的多个芯片,避免在执行键合工艺后对准图形被覆盖;通过将键合层的键合区域与衬底的键合覆盖区域键合连接,得到初始半导体结构;根据第一对准图形及第二对准图形为套刻对准图形,在初始半导体结构上形成半导体层,得到目标晶圆,对准图形正常显现,避免被键合层覆盖,降低对准难度,提高对准精度,保证键合工艺正常进行,提高生产效率。

4、在其中一些实施例中,提供衬底包括提供初始衬底,初始衬底上包括键合覆盖区域及周向环绕键合覆盖区域且位于初始衬底边缘的外围区域,外围区域为不执行清洗工艺的边缘区域;外围区域与键合覆盖区域连接且无交叠;键合覆盖区域内包括间隔阵列排布的多个芯片;于初始衬底的顶面形成对准图形材料层;图形化处理对准图形材料层,以于初始衬底的外围区域形成第一对准图形及第二对准图形,得到衬底。

5、在其中一些实施例中,图形化处理对准图形材料层,包括在对准图形材料层的顶面形成图形化光刻胶材料层,图形化光刻胶材料层内具有用于限定第一对准图形及第二对准图形的开口图形;以图形化光刻胶材料层为掩膜版刻蚀对准图形材料层,保留于初始衬底顶面的图形化光刻胶材料层用于构成第一对准图形及第二对准图形。

6、在其中一些实施例中,形成第一对准图形及第二对准图形之后,还包括去除剩余的图形化光刻胶材料层。

7、在其中一些实施例中,第一对准图形与第二对准图形的排布方向与衬底的切口的开口方向的夹角为[40度,70度];其中,切口的开口方向平行于贯穿切口的对称中心点与衬底顶面的对称中心点的直线。

8、在其中一些实施例中,半导体层包括栅介质层;形成半导体层包括在初始半导体结构的顶面形成栅介质材料层;于栅介质材料层的顶面形成第一掩膜层;以第一对准图形及第二对准图形为套刻对准图形,图形化第一掩膜层,得到第一图形化掩膜层;以第一图形化掩膜层为掩膜版刻蚀栅介质材料层,得到栅介质层。

9、在其中一些实施例中,半导体层包括位于栅介质层顶面的栅导电层;形成半导体层包括在栅介质层上形成导电材料层;于导电材料层的顶面形成第二掩膜层;以第一对准图形及第二对准图形为套刻对准图形,图形化第二掩膜层,得到第二图形化掩膜层;以第二图形化掩膜层为掩膜版刻蚀导电材料层,得到栅导电层。

10、在其中一些实施例中,半导体层包括位于栅导电层顶面的保护盖层;形成半导体层包括在栅导电层上形成第一保护层;于第一保护层的顶面形成第三掩膜层;以第一对准图形及第二对准图形为套刻对准图形,图形化第三掩膜层,得到第三图形化掩膜层;以第三图形化掩膜层为掩膜版刻蚀第一保护层,得到保护盖层。

11、在其中一些事实例中,形成目标晶圆包括在保护盖层上形成第四掩膜层;以第一对准图形及第二对准图形为套刻对准图形,图形化第四掩膜层,得到第四图形化掩膜层;第四图形化掩膜层具有用于限定源区/漏区的开口图形;以第四图形化掩膜层为掩膜版对初始半导体结构执行离子注入掺杂工艺,以于初始半导体结构内形成源区/漏区。

12、本公开的另一方面提供一种半导体结构,其采用本公开实施例中任一项晶圆键合方法制备而成。

13、上述实施例中的半导体结构,通过设置初始衬底上包括键合覆盖区域及周向环绕键合覆盖区域且位于初始衬底边缘的外围区域,外围区域为不执行清洗工艺的边缘区域;外围区域与键合覆盖区域连接且无交叠;键合覆盖区域内包括间隔阵列排布的多个芯片;在初始衬底的顶面形成对准图形材料层;图形化处理对准图形材料层,以于初始衬底的外围区域形成第一对准图形及第二对准图形,得到衬底,设置第一对准图形与第二对准图形的排布方向与衬底的切口的开口方向的夹角为[40度,70度],将键合覆盖区域和含有对准图形的区域区分,避免在执行键合工艺后对准图形被覆盖,从而避免出现套刻无法对准的情况;在所得衬底上依次形成栅介质层、栅导电层、保护盖层以及源区/漏区,得到半导体结构。目前采用相关晶圆键合方法制备成的半导体结构,目前相关的晶圆键合方法,将对准标记置于芯片的键合覆盖区域内,执行键合层覆盖后,原硅片上的对准标记和图形都会被覆盖,光刻机无法识别现有的对准标记,从而停止光刻工艺,并中止产品流片。采用本公开实施例中的的晶圆键合方法制备而成的半导体结构,通过设置初始衬底上包括键合覆盖区域及周向环绕键合覆盖区域且位于初始衬底边缘的外围区域,设置外围区域为不执行清洗工艺的边缘区域;在初始衬底的顶面形成对准图形材料层;图形化处理对准图形材料层,以于初始衬底的外围区域形成第一对准图形及第二对准图形,得到衬底,避免在执行键合工艺后对准图形被覆盖;设置第一对准图形与第二对准图形的排布方向,在所得衬底上依次形成栅介质层、栅导电层、保护盖层以及源区/漏区,得到半导体层,衬底与半导体层构成半导体结构。将晶圆键合覆盖区域和含有对准图形的区域区分,避免在执行键合工艺后对准图形被覆盖,从而避免出现套刻无法对准的情况;对准图形正常显现,避免被键合层覆盖,降低对准难度,提高对准精度,保证了键合工艺正常进行,提高生产效率。

- 还没有人留言评论。精彩留言会获得点赞!