一种电子芯片及其制备方法与流程

本技术涉及微电子,尤其是涉及一种电子芯片及其制备方法。

背景技术:

1、引线键合是实现电子芯片与外围电路互连的传统技术,键合点与键合引线承载着电子芯片内部电路与外围电路的功率传输与信号运输,二者的质量与可靠性对电子芯片的功能和寿命起着决定性的作用。键合引线一般使用纯度较高的金线,金线具有接触电阻低、延展性好、抗氧化性好与耐腐蚀性强等优良性能,是一种极好的键合材料。不过电子芯片的芯片焊盘通常并不是金质的,例如大多数电子芯片采用铝焊盘。由于键合引线与芯片焊盘异质,二者在晶格常数和热膨胀系数上存在较大差异,经长期使用后容易在二者的交界处形成柯肯达尔(kirkendall)空洞和机械强度极差的金属间化合物(intermetalliccompound,imc),且随着温度和时间的增加,空洞和金属间化合物会不断增加。伴随金属间化合物的产生,键合点接触电阻变大,降低了接触区域的电学性能,导致器件参数漂移,甚至开路而失效,影响产品的长期可靠性。

技术实现思路

1、为了阻止电子芯片的芯片焊盘同键合引线在键合处生成金属间化合物,维护电子芯片的长期可靠性,本技术提供了一种电子芯片及其制备方法。

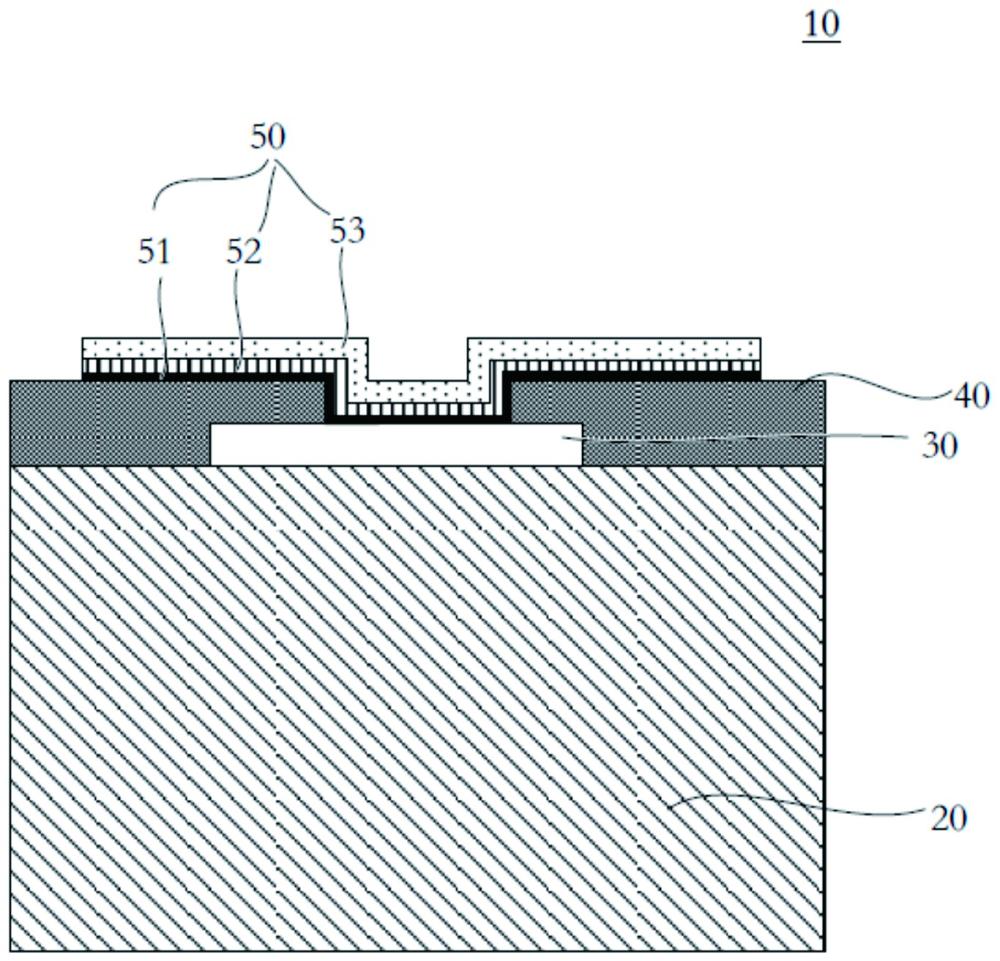

2、第一方面,本技术提供一种电子芯片,所述电子芯片包括:

3、裸芯半导体;

4、设于所述裸芯半导体表面的钝化层;

5、与所述裸芯半导体电连接且至少部分区域外露于所述钝化层的芯片焊盘;以及

6、设于所述芯片焊盘远离所述裸芯半导体一侧且导电的键合加固件;在沿着远离所述裸芯半导体的方向上,所述键合加固件包括依次层叠的粘附层、阻挡层以及键合层,所述粘附层附着于所述芯片焊盘上,所述键合层被配置为同外部的键合引线键合,所述阻挡层被配置为阻止所述阻挡层两侧层结构中的金属原子向着对侧扩散。

7、通过采用上述技术方案,电子芯片中在芯片焊盘远离裸芯半导体的一侧设置了导电的键合加固件,从靠近芯片焊盘的一侧到远离芯片焊盘的一侧,键合加固件中依次层叠有粘附层、阻挡层以及键合层。其中,粘附层附着于芯片焊盘上,可以确保键合加固件同芯片焊盘之间可靠连接;键合层用于同键合引线键合,键合层与键合引线具备很好地附着力,并且不会生成imc;阻挡层可以阻止两侧的金属间发生原子扩散,因此可以阻止两侧金属间生成金属间化合物。因此,具有该键合加固件的电子芯片在经历了引线键合工艺后,键合点处不易产生金属间化合物与柯肯达尔空洞,有利于维护电子芯片的性能稳定性,提升了应用该电子芯片的电子产品的可靠性,延长了电子产品的使用寿命。

8、可选地,所述键合加固件还包括设置于所述粘附层与所述阻挡层之间的加固层,所述加固层的硬度大于所述芯片焊盘的硬度。

9、通过采用上述技术方案,在键合加固件的粘附层与阻挡层之间还设置有硬度比较大的加固层,加固层可以赋予键合加固件较大的硬度,从而改善相关技术中因为芯片焊盘硬度不足,可承受的键合压力小而导致的键合工艺窗口小的问题,同时加固层的设置也降低了键合引线在较大键合压力下击穿键合加固件与芯片焊盘,引起电子芯片短路的风险。

10、可选地,所述键合加固件至少部分覆盖于所述钝化层上,且所述键合加固件与所述钝化层之间还设置有应力缓冲层;所述芯片焊盘为al(铝)焊盘,所述粘附层中包括ti(钛),所述加固层包括cu(铜)与ni(镍)中的至少一种,所述阻挡层中包括ni与cr(铬)中的至少一种,所述键合层包括au(金)、ag(银)以及pd(钯)中的至少一种。

11、通过采用上述技术方案,键合层包括au、ag、pd中的至少一种,阻挡层中包括ni与cr中的至少一种,加固层中包括cu与ni中的至少一种,粘附层中包括ti。au与ag均具有良好的键合性能,能与键合引线可靠键合,并长期维持可靠的结合力,同时au与ag又不容易与键合引线间发生扩散产生金属间化合物。ni与cr不易扩散,能够阻止两侧的金属原子扩散,可极大地减少柯肯达尔空洞与金属间化合物。cu与ni具有较大的硬度,确保了键合加固件的强度,能够防止键合引线在高键合压力下击穿键合加固件,避免了芯片焊盘在键合过程中受损。粘附层包含ti,ti能够增强加固层与芯片焊盘之间的结合力,也能阻止加固层的金属原子与芯片焊盘中的al原子向着彼此扩散,减少了金属间化合物的产生。

12、可选地,所述加固层朝向所述阻挡层的表面设有多个第一微结构,所述阻挡层朝向所述加固层的表面设有多个与所述第一微结构配合的第二微结构,所述第一微结构与所述第二微结构中的一个为凹陷微结构,另一个为嵌入所述凹陷微结构中的凸起微结构。

13、通过采用上述技术方案,在加固层与阻挡层的界面上设置有凹陷微结构以及与凹陷微结构配合的凸起微结构,可以增强加固层与阻挡层之间的结合力,提升键盘加固结构的可靠性。

14、可选地,所述芯片焊盘外露于所述钝化层的区域为未钝化区域,所述未钝化区域中设有若干深度小于所述芯片焊盘之厚度的凹槽,至少部分所述凹槽同所述未钝化区域边缘的距离小于所述凹槽同所述区域中心的距离;各所述凹槽绕所述未钝化区域的区域中心均匀分布,且每个所述凹槽的槽内空间均与外部空间连通。

15、通过采用上述技术方案,在芯片焊盘的未钝化区域中设置了若干凹槽,这些凹槽中至少部分同未钝化区域的边缘的距离小于该凹槽同区域中心的距离,因此至少部分凹槽分布于未钝化区域的边缘区域。在引线键合过程中虽然键合压力还是会通过键合加固件传导到芯片焊盘,使得芯片焊盘受延展性的影响而发生延展变形,但这些凹槽可以在一定程度上吸收芯片焊盘的延展变形量,缓解芯片焊盘因延展变形而对四周钝化层造成的挤压,降低脆性钝化层因为挤压而破裂的风险,避免钝化层对裸芯半导体的保护作用失效,使得钝化层可以继续对裸芯半导体进行电气绝缘与水汽防护,维护电子芯片的电气可靠性。同时,因为凹槽并没有贯穿芯片焊盘,因此芯片焊盘的下部依旧可以利用全部区域承载电流,这样可以降低凹槽设置对芯片焊盘电流承载能力的影响。

16、可选地,所述凹槽靠近所述区域中心一侧的侧壁为近中心侧壁,所述近中心侧壁在平行于所述未钝化区域的投影面上的正投影图形包括交替设置的外凸齿与内凹口,所述外凸齿相对于所述内凹口向着远离所述区域中心的方向外凸,所述内凹口相对于所述外凸齿向着靠近所述区域中心的方向内凹。

17、通过采用上述技术方案,在凹槽的近中心侧壁上交替设置外凸齿与内凹口,因为外凸齿的“外凸”以及内凹口的“内凹”是站在芯片焊盘的实体部分的角度而言的,而站在凹槽空间的角度而言,内凹口意味着凹槽空间在内凹口对应的位置处会向着区域中心外凸,外凸齿意味着凹槽空间在外凸齿对应的位置处会向着未钝化区域的边缘内凹,通过内凹口的间隔设置,可以提升凹槽对芯片焊盘延展变形量的吸收能力,进一步减小芯片焊盘在键合压力下延展变形对钝化层的影响。

18、可选地,所述凹槽为环绕所述区域中心设置的环形槽;沿着远离所述区域中心的方向,所述内凹口的开口尺寸逐渐增大。

19、通过采用上述技术方案,凹槽为环绕区域中心设置的环形槽,因此利用该环形槽能够在未钝化区域的各个径向方向上对芯片焊盘的延展变形量进行吸收,减少传导至芯片焊盘边缘的延展变形量,降低引线键合过程中键合压力对钝化层的影响。

20、可选地,所述凹槽为设置于所述未钝化区域中的扩散状凹槽,所述扩散状凹槽的槽口轮廓包括第一线段以及与所述第一线段相邻的第二线段,所述第一线段与所述第二线段相交于第一点形成角度不超过90°的夹角,所述第一点为所述槽口轮廓上距离所述区域中心最近的一点。

21、通过采用上述技术方案,在未钝化区域中设置有多个扩散状凹槽,扩散状凹槽的槽口轮廓以第一点为顶点所形成的夹角背向未钝化区域的区域中心,所以沿着远离区域中心的方向,该夹角的敞口逐渐增大。芯片焊盘在引线键合过程中承受的键合压力会使得芯片焊盘从中心向边缘挤压延展,区域中心的延展量会向外叠加,导致从区域中心到未钝化区域的边缘延展量逐渐增大。因此扩散状凹槽的形状与未钝化区域上各处的延展变形量更契合,能够更有效地利用有限的凹槽空间吸收更大的延展变形量,在保护钝化层的基础上降低凹槽设置芯片焊盘电流承载能力的影响。

22、第二方面,本技术提供一种电子芯片制备方法,电子芯片制备方法包括:

23、提供裸芯半导体;

24、在所述裸芯半导体上设置芯片焊盘;

25、设置包覆所述裸芯半导体与所述芯片焊盘的钝化层,并对所述钝化层进行图案化处理,以使所述芯片焊盘至少部分区域外露于所述钝化层;

26、在所述芯片焊盘外露于所述钝化层的未钝化区域中设置键合加固件;所述键合加固件包括依次层叠的粘附层、阻挡层以及键合层,所述粘附层附着于所述芯片焊盘上,所述键合层被配置为同外部的键合引线键合,所述阻挡层被配置为阻止所述阻挡层两侧层结构中的金属原子向着对侧扩散。

27、通过采用上述技术方案,制备电子芯片的过程中在芯片焊盘远离裸芯半导体的一侧设置了导电的键合加固件,从靠近芯片焊盘的一侧到远离芯片焊盘的一侧,键合加固件中依次层叠有粘附层、阻挡层以及键合层。其中,粘附层附着于芯片焊盘上,可以确保键合加固件同芯片焊盘之间可靠连接;键合层用于同键合引线键合;阻挡层可以阻止两侧的金属间发生原子扩散,因此可以阻止两侧金属间生成金属间化合物。因此,具有该键合加固件的电子芯片在经历了引线键合工艺后,键合点处不易产生金属间化合物与柯肯达尔空洞,有利于维护电子芯片的性能稳定性,提升了应用该电子芯片的电子产品的可靠性,延长了电子产品的使用寿命。

28、可选地,所述在所述裸芯半导体上设置芯片焊盘包括:

29、在所述裸芯半导体上沉积金属形成芯片焊盘层;

30、对所述芯片焊盘层进行图案化处理形成若干凹槽,所述凹槽的深度小于所述芯片焊盘层的厚度;

31、在所述凹槽中填充牺牲材料形成牺牲层,所述牺牲层远离所述凹槽之槽底的一面与所述芯片焊盘层的表面齐平;

32、所述在所述芯片焊盘外露于所述钝化层的未钝化区域中设置键合加固件包括:

33、在所述未钝化区域中设置所述粘附层;

34、在所述粘附层上设置加固层,所述加固层的硬度大于所述芯片焊盘的厚度;

35、在所述加固层上设置所述阻挡层;

36、在所述阻挡层上设置所述键合层;

37、所述在所述芯片焊盘外露于所述钝化层的未钝化区域中设置键合加固件之后,还包括:去除所述凹槽中的所述牺牲层。

38、通过采用上述技术方案,在裸芯半导体上设置芯片焊盘的过程中,先在裸芯半导体层上设置芯片焊盘层,然后通过对芯片焊盘层进行图案化处理形成若干深度小于芯片焊盘层厚度的凹槽,随后用牺牲材料填充凹槽形成牺牲层,在设置了键合加固件后再去除牺牲层,使得凹槽至少部分外露。在引线键合过程中虽然键合压力还是会通过键合加固件传导到芯片焊盘,使得芯片焊盘受延展性的影响而发生延展变形,但因为这些凹槽可以在一定程度上吸收芯片焊盘的延展变形量,这样可以缓解芯片焊盘因延展变形而对四周钝化层造成的挤压,降低钝化层因为挤压而破裂的风险,避免钝化层对裸芯半导体的保护作用失效,使得钝化层可以继续对裸芯半导体进行电气绝缘与水汽防护,维护电子芯片的电气可靠性。同时,因为凹槽并没有贯穿芯片焊盘,因此芯片焊盘的下部依旧可以利用全部区域承载电流,这样可以降低凹槽设置对芯片焊盘电流承载能力的影响。

39、综上所述,本技术至少包括以下有益技术效果:通过在芯片焊盘上设置键合加固件,引线键合过程中将键合引线键合到键合加固件上,键合点处不易产生金属间化合物与柯肯达尔空洞,有利于维护电子芯片的性能稳定性,提升了应用该电子芯片的电子产品的可靠性,延长了电子产品的使用寿命。

- 还没有人留言评论。精彩留言会获得点赞!