一种高深宽比硬掩膜去除方法与流程

本发明涉及半导体,特别是涉及一种高深宽比硬掩膜去除方法。

背景技术:

1、lv_sj通过多道高能imp形成p柱,根据ds仿真结果显示,3400k的能量需要5.6um的hm去阻挡,且pre ppl imp film(ppl薄膜预注入)的厚度直接影响后续imp的注入深度,从而直接影响器件的bv,为保证bv达到目标值,预imp注入前的厚度需保证在500a-600a左右(sin200-300a)。但是在后续hm teos湿法去除时,遇到了因工艺过程时间长,剩余的sin会不够挡或酸液有足够时间从划片道进入沟槽,破坏沟槽里栅氧结构等一系列问题。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种高深宽比硬掩膜去除方法,用于解决现有技术中湿法刻蚀中硬掩膜变薄导致酸液破坏栅氧结构的问题。

2、为实现上述目的及其他相关目的,本发明提供一种高深宽比硬掩膜去除方法,

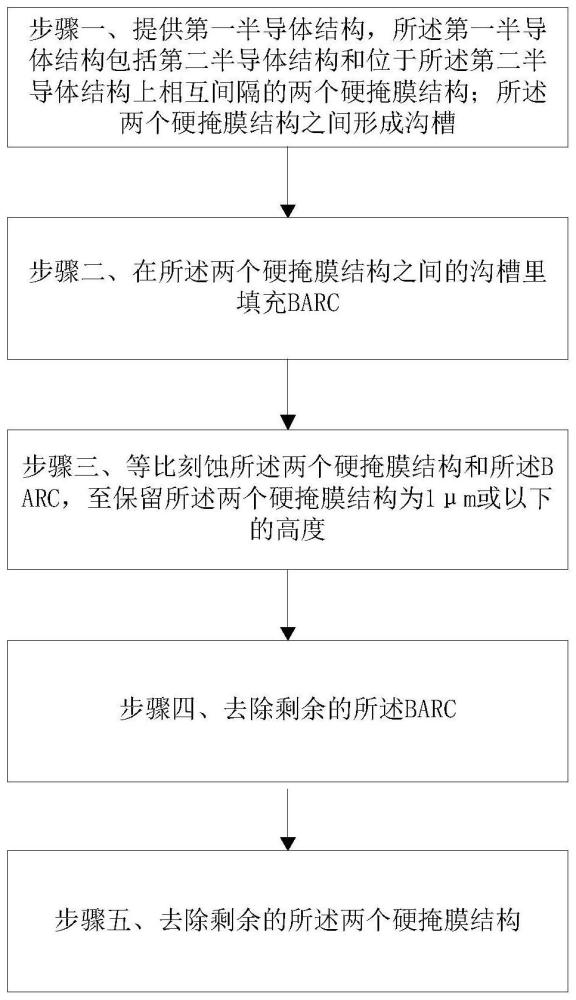

3、步骤一、提供第一半导体结构,所述第一半导体结构包括第二半导体结构和位于所述第二半导体结构上相互间隔的两个硬掩膜结构;所述两个硬掩膜结构之间形成沟槽;

4、步骤二、在所述两个硬掩膜结构之间的沟槽里填充barc;

5、步骤三、等比刻蚀所述两个硬掩膜结构和所述barc,至保留所述两个硬掩膜结构为1μm或以下的高度;

6、步骤四、去除剩余的所述barc;

7、步骤五、去除剩余的所述两个硬掩膜结构。

8、优选地,步骤一中的所述两个硬掩膜结构为teos结构。

9、优选地,步骤一中的所述两个硬掩膜结构为ppl硬掩膜层刻蚀后形成的结构。

10、优选地,步骤一中的所述两个硬掩膜结构为高深宽边的结构。

11、优选地,步骤一中的所述第二半导体结构包含有被所述两个硬掩膜结构分别覆盖的栅氧结构以及覆盖于所述栅氧结构上的sin层。

12、优选地,步骤一中的所述栅氧结构为位于所述第二半导体结构的沟槽内壁的栅氧层。

13、优选地,步骤三中保留所述两个硬掩膜结构的高度为大于0。

14、优选地,步骤三中等比刻蚀所述两个硬掩膜结构和所述barc的刻蚀方法为干法刻蚀和湿法刻蚀。

15、如上所述,本发明的高深宽比硬掩膜去除方法,具有以下有益效果:本发明是在硬掩膜结构的沟槽里填充barc,通过刻蚀调节硬掩膜结构和barc的选择比,将其减薄至1um或者更薄,去除barc后再去除硬掩膜结构。由于硬掩膜结构变薄,湿法刻蚀的时间减少,酸液没有足够的时间进入栅氧结构的沟槽里,栅氧结构不会被破坏。

技术特征:

1.一种高深宽比硬掩膜去除方法,其特征在于,至少包括:

2.根据权利要求1所述的高深宽比硬掩膜去除方法,其特征在于:步骤一中的所述两个硬掩膜结构为teos结构。

3.根据权利要求1所述的高深宽比硬掩膜去除方法,其特征在于:步骤一中的所述两个硬掩膜结构为ppl硬掩膜层刻蚀后形成的结构。

4.根据权利要求1所述的高深宽比硬掩膜去除方法,其特征在于:步骤一中的所述两个硬掩膜结构为高深宽边的结构。

5.根据权利要求1所述的高深宽比硬掩膜去除方法,其特征在于:步骤一中的所述第二半导体结构包含有被所述两个硬掩膜结构分别覆盖的栅氧结构以及覆盖于所述栅氧结构上的sin层。

6.根据权利要求1所述的高深宽比硬掩膜去除方法,其特征在于:步骤一中的所述栅氧结构为位于所述第二半导体结构的沟槽内壁的栅氧层。

7.根据权利要求1所述的高深宽比硬掩膜去除方法,其特征在于:步骤三中保留所述两个硬掩膜结构的高度为大于0。

8.根据权利要求1所述的高深宽比硬掩膜去除方法,其特征在于:步骤三中等比刻蚀所述两个硬掩膜结构和所述barc的刻蚀方法为干法刻蚀和湿法刻蚀。

技术总结

本发明提供一种高深宽比硬掩膜去除方法,提供第一半导体结构,第一半导体结构包括第二半导体结构和位于第二半导体结构上相互间隔的两个硬掩膜结构;两个硬掩膜结构之间形成沟槽;在两个硬掩膜结构之间的沟槽里填充BARC;等比刻蚀两个硬掩膜结构和BARC,至保留两个硬掩膜结构为1μm或以下的高度;去除剩余的BARC;去除剩余的两个硬掩膜结构。本发明是在硬掩膜结构的沟槽里填充BARC,通过刻蚀调节硬掩膜结构和BARC的选择比,将其减薄至1um或者更薄,去除BARC后再去除硬掩膜结构。由于硬掩膜结构变薄,湿法刻蚀的时间减少,酸液没有足够的时间进入栅氧结构的沟槽里,栅氧结构不会被破坏。

技术研发人员:徐进,陈思彤,赵鑫栋,许铭源

受保护的技术使用者:华虹半导体(无锡)有限公司

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!