晶体管器件的制作方法

背景技术:

1、低频或者1/f噪声(也被称为闪烁噪声)是场效应晶体管(诸如mosfet器件)中的主要噪声源。尽管不希望被理论所束缚,但是1/f噪声可能是由载流子(诸如电子或者空穴)引起的,所述载流子被暂时性地俘获在栅极电介质和/或栅极电介质和晶体管的沟道之间的界面中。载流子到陷阱或者缺陷中心(诸如硅悬空键)中、到栅极电介质中以及回到沟道中的随机迁移,可能引起通过晶体管的电流波动,这表现为1/f噪声。

2、朝向更小并且更快的半导体器件的推进已经增加了对降低1/f噪声的需要。在放大电路中,可以通过如下来部分地减少1/f噪声的影响:在初始级中使用具有大的器件面积的晶体管,从而在放大电路的后续级中1/f噪声不被与信号相同程度地放大。然而,这种方法可能无法防止在其中使用更小晶体管的电路中的更靠后放大级处引入1/f噪声。此外,这样的器件能够被缩减到的尺寸可能受针对一个或者多个大的前级晶体管的必要性限制。

3、美国专利8 076 228b2公开了一种具有降噪剂的低噪声晶体管,降噪剂被引入到栅极电极中并且然后被移动到栅极电介质中。然而,进一步的低噪声晶体管器件是合期望的。

技术实现思路

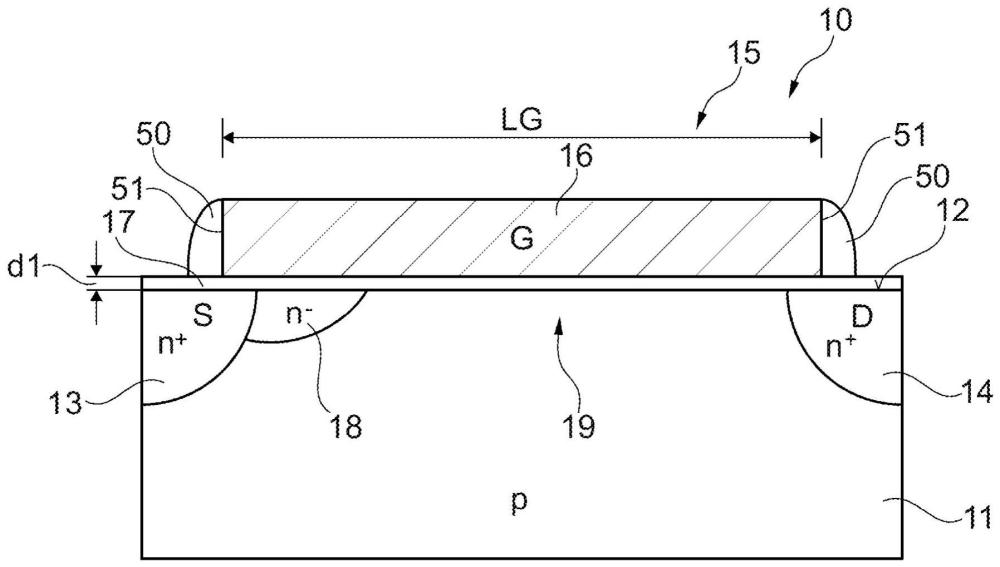

1、根据本发明的实施例,提供了一种晶体管器件,晶体管器件包括:具有第一掺杂剂类型的掺杂浓度的半导体衬底;被形成在半导体衬底的第一表面中的与第一掺杂剂类型相反的第二掺杂剂类型的高掺杂的源极区;被形成在半导体衬底的第一表面中的第二掺杂剂类型的高掺杂的漏极区;被布置在第一表面上并且包括被形成在第一表面上的栅极电极的栅极结构;以及被形成在第一表面中并且在栅极电极下方从高掺杂的源极区延伸的第二掺杂剂类型的第一轻掺杂区。半导体衬底提供在第一轻掺杂区和高掺杂的漏极区之间延伸的沟道区,其中沟道区具有n×10x的第一掺杂剂类型的平均掺杂水平,该平均掺杂水平沿着平行于第一表面的横向方向变化小于0.5×n×10x。

2、x处于13至16的范围内,从而沟道区的第一掺杂剂类型的平均掺杂水平处于1013至1016的范围内。第一导电类型的该平均掺杂水平在沟道区中在平行于第一表面的横向方向上在第一轻掺杂区和高掺杂的漏极区之间变化小于0.5×n×10x。

3、在该晶体管器件中,高掺杂的漏极区仅与半导体衬底形成结,而高掺杂的源极区与第一轻掺杂区接触或者重叠。第一轻掺杂区也可以被称为ldd区(low doped diffusionregion,低掺杂的扩散区)。晶体管器件在高掺杂的漏极区和沟道区之间具有突变结,因为轻掺杂区仅被布置在高掺杂的源极区和沟道区之间。晶体管器件可以被认为是非对称器件。在一些实施例中,晶体管器件是非对称cmos器件。

4、由于沟道区具有n×10x的第一掺杂剂类型的平均掺杂水平,该平均掺杂水平沿着平行于第一表面横向方向并且在第一轻掺杂区和高掺杂的漏极区之间变化小于0.5×n×10x,因此晶体管器件不具有分级的沟道区,并且该沟道区从第一轻掺杂区到高掺杂的漏极区具有实质上相同的掺杂水平。更进一步地,晶体管器件不具有晕环注入。

5、提供了一种晶体管器件,其具有降低的cgg(在栅极处看到的总电容)和cgd(栅极漏极电容),以便降低输入相关噪声电平、闪烁噪声电平,并且提供由更高gm/id(跨导dc漏极电流比)所要求的白噪声改进。这是通过省略器件的漏极侧上的低掺杂的扩散区(ldd)来实现的,从而突变结被形成在高掺杂的漏极区和半导体衬底之间。晶体管器件适合于在其中操作电压vds<供给电压vdd(或者技术节点的标称供给电压)的应用中使用。例如,应用的示例是模拟麦克风应用、源极跟随器模式操作、在低于供给电压vdd下操作的vco(电压控制运算器)以及在饱和模式(vgs-vt)<vds下在阈值附近(例如vg~vt)操作的器件。

6、在一些实施例中,栅极电极与第一轻掺杂区重叠。

7、在一些实施例中,栅极结构进一步包括被布置在栅极电极和半导体衬底的第一表面之间的栅极绝缘层,栅极绝缘层具有第一厚度d1。栅极绝缘层也可以被称为栅极电介质层。栅极绝缘层可以由氧化物形成,例如氧化硅。栅极电极是导电的,并且可以由例如多晶硅形成。

8、栅极绝缘层与半导体衬底的第一表面直接接触以及与栅极电极的下表面直接接触。栅极电极可以具有实质上平坦的上表面和实质上平坦的下表面,并且具有沿着其长度实质上相同的厚度。

9、高掺杂的源极区、第一轻掺杂区和高掺杂的漏极区可以具有与半导体衬底相反的导电类型,例如n型,如果高掺杂的源极区、第一轻掺杂区和高掺杂的漏极区是n型,则半导体衬底例如可以是p型。

10、半导体衬底可以由硅形成,例如单晶硅或者被形成在基底衬底上的硅外延层。

11、根据本发明的实施例,晶体管器件包括:具有第一掺杂剂类型的掺杂浓度的半导体衬底;被形成在半导体衬底的第一表面中的与第一掺杂剂类型相反的第二掺杂剂类型的高掺杂的源极区;以及被形成在半导体衬底的第一表面中的第二掺杂剂类型的高掺杂的漏极区。半导体衬底在高掺杂的源极区和高掺杂的漏极区之间提供沟道区。晶体管器件进一步包括被布置在第一表面上的栅极结构。栅极结构包括:被布置在第一表面上的具有厚度d1的栅极绝缘层;栅极电极,其被形成在栅极绝缘层上并且包括从栅极电极朝向高掺杂的漏极区延伸的场板延伸;以及具有大于第一厚度d1的第二厚度d2的延伸绝缘层。场板延伸被通过延伸绝缘层与第一表面间隔开。过渡部被形成在栅极绝缘层和延伸绝缘层之间。过渡部与高掺杂的漏极区在横向上间隔开距离l。

12、该晶体管器件可以被认为是非对称器件,因为栅极电极仅在漏极侧上包括场板。

13、更薄的栅极绝缘层和更厚的延伸绝缘层之间的过渡部可以在被布置在第一表面上的绝缘层的厚度中具有台阶或者突然增加的形式。过渡部的定位也是栅极电极和场板延伸之间的过渡部或者台阶的定位。该过渡部或者台阶被定位在沟道区上。

14、在一些实施例中,栅极电极的上表面和场板延伸的上表面是实质上共面的。在这些实施例中,场板延伸的厚度小于栅极电极的厚度。该过渡部或者台阶也是提供栅极电极/场板结构的导电材料的厚度中的台阶的过渡部。栅极长度对应于被通过具有厚度d1的栅极绝缘层与半导体衬底的第一表面间隔开的导电材料的长度。场板延伸的长度对应于被通过具有厚度d2的延伸绝缘层与半导体衬底的第一表面间隔开的导电材料的长度。

15、由于过渡部与高掺杂的漏极区在横向上间隔开距离l,因此过渡部被竖向地定位在具有晶体管器件的反型层的沟道区上方,而不是被定位在高掺杂的漏极区或者诸如ldd漏极延伸的轻掺杂漏极区上方。

16、提供了一种晶体管器件,其具有降低的cgg和cgd,以便降低输入相关噪声电平、闪烁噪声电平,并且提供由更高gm/id所要求的白噪声改进。这是通过在栅极电极的漏极侧上包括场板延伸来实现的。晶体管器件适合于在其中操作电压vds<供给电压vdd(或者技术节点的标称供给电压)的应用中使用。例如,应用的示例是模拟麦克风应用、源极跟随器模式操作、在低于供给电压vdd下操作的vco(电压控制运算器)以及在饱和模式(vgs-vt)<vds下在阈值附近(例如vg~vt)操作的器件。

17、在一些实施例中,场板延伸至少部分地与高掺杂的漏极区重叠。

18、在一些实施例中,高掺杂的源极区和高掺杂的漏极区这两者仅与半导体衬底接触。

19、半导体衬底在高掺杂的源极区和高掺杂的漏极区之间提供沟道区。在一些实施例中,沟道区具有n×10x的第一掺杂剂类型的平均掺杂水平,该平均掺杂水平在高掺杂的源极区和高掺杂的漏极区之间沿着平行于第一表面的横向方向变化小于0.5×n×10x。x处于13至16的范围内,从而沟道区的平均掺杂水平处于1013至1016的范围内。对于5×1015的平均掺杂水平而言,变化可以在0和2.5×1015之间。

20、由于沟道区具有n×10x的平均掺杂水平,该平均掺杂水平在平行于第一表面的横向方向上在第一轻掺杂区和高掺杂的漏极区之间变化小于0.5×n×10x,因此晶体管器件不具有分级的沟道区,并且沟道区从第一轻掺杂区到高掺杂的漏极区具有实质上相同的掺杂水平。更进一步地,晶体管器件不具有晕环注入。

21、在一些实施例中,过渡部和高掺杂的漏极区之间的距离l为0nm<l≤1μm,或者0nm<l≤250nm,或者10nm≤l≤250nm,或者50nm≤l≤250nm,或者100nm≤l≤225nm。

22、在一些实施例中,晶体管器件进一步包括被形成在第一表面中并且在栅极电极下方从高掺杂的源极区延伸的第二掺杂剂类型的第一轻掺杂区。因此,第一轻掺杂区仅被定位在栅极电极的源极侧端部下方,并且被通过沟道区与高掺杂的漏极区间隔开,该沟道区具有n×10x的第一掺杂剂类型的平均掺杂水平,该平均掺杂水平在轻掺杂源极区和高掺杂的漏极区之间沿着平行于第一表面的横向方向变化小于0.5×n×10x。

23、在一些实施例中,晶体管器件进一步包括在场板延伸下方从高掺杂的漏极区延伸的第二掺杂剂类型的第二轻掺杂区。在这些实施例中,过渡部仍然被通过沟道区的一部分与第二轻掺杂区间隔开。因此,过渡部被竖向地布置在沟道区上方而不是第二轻掺杂区上方。因此,第二轻掺杂区仅被定位在场板延伸的漏极侧端部下方,并且被通过沟道区与高掺杂的源极区或者与第一轻掺杂区(如果存在的话)间隔开,该沟道区具有n×10x的第一掺杂剂类型的平均掺杂水平,该平均掺杂水平变化小于0.5×n×10x。

24、在一些实施例中,晶体管器件进一步包括在栅极绝缘层中和/或在半导体衬底的第一表面处的降噪剂。在一些实施例中,降噪剂被布置在半导体衬底中紧接在第一表面下方的层中。

25、在一些实施例中,降噪剂包括氟离子。

26、在一些实施例中,晶体管器件进一步包括被布置在栅极结构的侧面上的间隔壁。例如,间隔壁可以被布置在栅极电极的相对的侧面上。在包括漏极侧场板延伸的实施例中,间隔壁被布置在栅极电极的源极侧侧面上和场板延伸的漏极侧侧面上。降噪剂可以是在横向上邻近于间隔壁引入的,并且移动到被布置在间隔壁下方和栅极电极下方的栅极绝缘层中。

27、在一些实施例中,晶体管器件进一步包括第一阱,第一阱包括第一掺杂剂类型。第一阱被形成在第一表面中,并且与半导体衬底的其余部分电绝缘。高掺杂的源极区和高掺杂的漏极区包括第二掺杂剂类型并且被定位在第一阱中。

28、在该实施例中,第一阱和它被形成在其中的半导体衬底具有相同的导电类型。该实施例可以被用于在p掺杂的衬底材料中制备例如一个或者多个p沟道器件,例如pfets。p沟道器件可以是以三阱方式构建的以将器件本体与衬底隔离。这具有器件本体可以被独立偏置的益处。隔离的三阱可以是通过n隔离注入和n型沉陷部(sinker)/阱形成的,以连接到深隔离带,深隔离带是n掺杂的并且将p掺杂阱与p掺杂衬底横向隔离。

29、在一些实施例中,第一阱被通过从第一表面延伸到半导体衬底中的一个或者多个电绝缘沟槽或者第二掺杂剂类型的沉陷部以及通过被布置在第一阱下方的第二掺杂剂类型的横向绝缘层来与半导体衬底电绝缘。

30、在一些实施例中,沟槽或者沉陷部从第一表面延伸到半导体衬底中,并且在一些实施例中,在横向上包围并且连续地包围阱和被形成在其中的(一个或多个)晶体管器件。横向绝缘层可以在沟槽或者沉陷部之间延伸。

31、在一些实施例中,晶体管器件进一步包括第二掺杂剂类型的第二阱和被形成在第二阱中的进一步的晶体管器件,其中第二阱与半导体衬底电绝缘。进一步的晶体管器件包括:被形成在第二阱的第一表面中的第一掺杂剂类型的高掺杂的源极区;被形成在阱中的第一掺杂剂类型的高掺杂的漏极区;以及栅极结构,其包括在第二阱上方被形成在第一表面上的栅极电极。

32、在一些实施例中,第二阱被通过从第一表面延伸到半导体衬底中的一个或者多个电绝缘沟槽或者受损区以及通过被布置在第二阱下方的横向绝缘层来与半导体衬底电绝缘。受损区包括半导体衬底的结晶受损的(例如被破坏的)并且电绝缘的材料。

33、例如,该实施例可以被用于在p掺杂的衬底上制备n沟道器件。在p掺杂的衬底材料上,n沟道器件(例如nfets)可以是以三阱方式构建的,以将器件本体与衬底隔离。(一个或多个)n沟道器件和(一个或多个)p沟道器件可以被形成在同一半导体衬底中。

34、在一些实施例中,第二阱和被形成在其中的进一步的晶体管器件与半导体衬底电绝缘。

35、在一些实施例中,沟槽从第一表面延伸到半导体衬底中,并且在一些实施例中在横向上包围并且连续地包围第二阱和被形成在其中的(一个或多个)晶体管器件。横向绝缘层可以在沟槽之间延伸。

36、在一些实施例中,晶体管器件是pmos或者nmos器件,例如p沟道cmos器件或者n沟道cmos器件。

37、本领域技术人员在阅读以下详细描述和在查看随附附图时将认识到附加的特征和优点。

- 还没有人留言评论。精彩留言会获得点赞!