一种叠层芯片预埋基板封装结构及其制备方法与流程

本发明涉及半导体封装结构领域,具体为一种叠层芯片预埋基板封装结构及其制备方法。

背景技术:

1、正常的eclga封装结构在一般设计过程中仅简单的预埋一颗芯片,上面贴装一颗电感元器件,实现电源部分结构的载流设计,但是通道和电流的负载能力上存在局限,需要在节省空间布局的情况下多通道满足实际功能需求,同时要满足产品的散热,不能受热导致影响产品功能受阻。

技术实现思路

1、针对现有技术中eclga封装结构电流负载能力不足的问题,本发明提供一种叠层芯片预埋基板封装结构及其制备方法。

2、本发明是通过以下技术方案来实现:

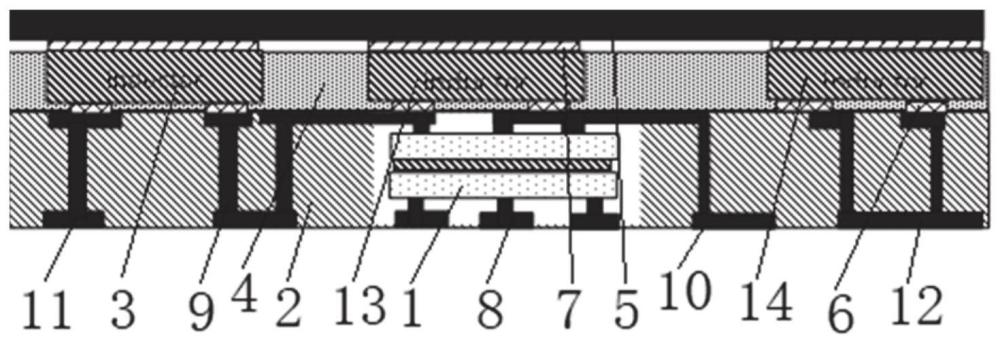

3、一种叠层芯片预埋基板封装结构,包括叠层芯片、基板、电感元器件、塑封料、连通铜柱和散热片,叠层芯片预埋于基板内部,叠层芯片通过连通铜柱引至基板的上表面和下表面,叠层芯片利用基板工艺的电镀引线实现芯片的电路导通;电感元器件设置于基板的上表面,并与连通铜柱电气连接;塑封料包覆于电感元器件周围,散热片连接于电感器元器件上方。

4、优选的,叠层芯片以未切割的wafer作为载体先叠层后切割所制。

5、优选的,叠层时采用daf膜进行连接。

6、优选的,基板上开设有凹槽,叠层芯片通过胶膜埋置于凹槽内部;凹槽的其余部分灌充有abf胶。

7、优选的,连接铜柱的上表面与基板上表面平齐。

8、优选的,塑封料的上表面与电感元器件的上表面平齐。

9、优选的,连接铜柱包括第一铜柱、第二铜柱、第三铜柱、第四铜柱和第五铜柱,电感元器件包括第一元器件、第二元器件和第三元器件,叠层芯片通过第一铜柱引至基板下表面,叠层芯片分别通过第二铜柱的右侧铜柱和第三铜柱引至基板上表面并与第二元器件连接;第四铜柱的下表面引至基板下表面,上表面引至基板上表面并与第一元器件连接,第二铜柱的左侧铜柱上表面与第一元器件连接;第五铜柱的下表面引至基板下表面,第五铜柱的两根连接铜柱单独引至基板上表面与第三元器件连接。

10、优选的,基板的上表面和下表面均镀有solder mask。

11、优选的,散热片与电感元器件之间通过散热胶进行连接。

12、一种叠层芯片预埋基板封装结构的制备方法,包括以下步骤:

13、步骤1:减薄wafer,并制作叠层芯片;

14、步骤2:将叠层芯片埋置于基板中,并减薄基板,再经建设、布线、层压、曝光、溅镀、蚀刻和正反镀,获得第一次封装体;

15、步骤3:在第一封装体的基板上贴装电感元器件,然后进行塑封,获得塑封零件;

16、步骤4:采用磨胶工艺露出电感元器件的上表面,并贴装散热片,获得成品零件。

17、与现有技术相比,本发明具有以下有益效果:

18、本发明一种叠层芯片预埋基板封装结构利用wafer当做基材在wafer贴一层芯片,切割后得到双面的单颗芯片,利用基板的多层布局,使叠层芯片线路导通,通过增加通道是电流的负载能力增加,集成度提高,在借助高导率塑封料和散热片的双重散热为产品导热,提高产品功能和空间利用率。

19、本发明一种叠层芯片预埋基板封装结构的制备方法以wafer作为载体进行芯片的叠层,在把叠层芯片的wafer切成单颗预埋到基板内部,再利用基板工艺的电镀引线把双层的芯片电路连接导通,最后在基板上贴装电感元器件,在整体塑封包裹,最后磨出电感元器件的顶部使其露出,在贴装散热片,使其引导电感元器件产生的热量能散发出去,不影响产品运行的功能效率。

技术特征:

1.一种叠层芯片预埋基板封装结构,其特征在于,包括叠层芯片(1)、基板(2)、电感元器件、塑封料(4)、连通铜柱和散热片(5),叠层芯片(1)预埋于基板(2)内部,叠层芯片(1)通过连通铜柱引至基板(2)的上表面和下表面,叠层芯片(1)利用基板(2)工艺的电镀引线实现芯片的电路导通;电感元器件设置于基板(2)的上表面,并与连通铜柱电气连接;塑封料(4)包覆于电感元器件周围,散热片(5)连接于电感器元器件上方。

2.根据权利要求1所述的叠层芯片预埋基板封装结构,其特征在于,叠层芯片(1)以未切割的wafer作为载体先叠层后切割所制。

3.根据权利要求1所述的叠层芯片预埋基板封装结构,其特征在于,叠层时采用daf膜(6)进行连接。

4.根据权利要求1所述的叠层芯片预埋基板封装结构,其特征在于,基板(2)上开设有凹槽,叠层芯片(1)通过胶膜埋置于凹槽内部;凹槽的其余部分灌充有abf胶。

5.根据权利要求1所述的叠层芯片预埋基板封装结构,其特征在于,连接铜柱的上表面与基板(2)上表面平齐。

6.根据权利要求1所述的叠层芯片预埋基板封装结构,其特征在于,塑封料(4)的上表面与电感元器件的上表面平齐。

7.根据权利要求1所述的叠层芯片预埋基板封装结构,其特征在于,连接铜柱包括第一铜柱(8)、第二铜柱(9)、第三铜柱(10)、第四铜柱(11)和第五铜柱(12),电感元器件包括第一元器件(3)、第二元器件(13)和第三元器件(14),叠层芯片(1)通过第一铜柱(8)引至基板(2)下表面,叠层芯片(1)分别通过第二铜柱(9)的右侧铜柱和第三铜柱(10)引至基板(2)上表面并与第二元器件(13)连接;第四铜柱(11)的下表面引至基板(2)下表面,上表面引至基板(2)上表面并与第一元器件(3)连接,第二铜柱(9)的左侧铜柱上表面与第一元器件(3)连接;第五铜柱(12)的下表面引至基板(2)下表面,第五铜柱(12)的两根连接铜柱单独引至基板(2)上表面与第三元器件(14)连接。

8.根据权利要求1所述的叠层芯片预埋基板封装结构,其特征在于,基板(2)的上表面和下表面均镀有solder mask。

9.根据权利要求1所述的叠层芯片预埋基板封装结构,其特征在于,散热片(5)与电感元器件之间通过散热胶(7)进行连接。

10.一种如权利要求1~9任一项所述的叠层芯片预埋基板封装结构的制备方法,其特征在于,包括以下步骤:

技术总结

本发明涉及半导体封装结构领域,尤其涉及一种叠层芯片预埋基板封装结构,包括叠层芯片、基板、电感元器件、塑封料、连通铜柱和散热片,叠层芯片预埋于基板内部,叠层芯片通过连通铜柱引至基板的上表面和下表面,叠层芯片利用基板工艺的电镀引线实现芯片的电路导通;电感元器件设置于基板的上表面,并与连通铜柱电气连接;塑封料包覆于电感元器件周围,散热片连接于电感器元器件上方。本发明使用纵向立体式排布,利用基板自身厚度内嵌双层IC芯片,相当于使用基板把双层芯片导通,再利用高导热塑封料和散热片双重散热提高元器件本身的运行效率。

技术研发人员:李伟,刘卫东

受保护的技术使用者:华天科技(南京)有限公司

技术研发日:

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!