半导体器件以及其测试方法与流程

本技术涉及半导体,具体而言,涉及一种半导体器件以及其测试方法。

背景技术:

1、salicide(自对准金属硅化物)工艺已经广泛应用在半导体器件的制作工艺中,可有效降低多晶硅栅和有源区方块电阻以及接触电阻,同时在设计上可以得到更小串联电阻,降低rc delay(电阻电容的延迟),提高电路的速度;工艺上通过在多晶硅栅和有源区上淀积一层金属层,经过热退火等工艺,在多晶硅栅和有源区同时形成金属硅化物。

2、目前在65nm以下工艺,主要采用ni-salicide,首先在低温下形成ni2si,随着温度升高再形成nisi。但nisi具有热不稳定性,在高温下容易形成稳定的化合物nisi2,在这个过程中ni是主要扩散物,导致nisi2深入衬底形成短路,会形成漏电问题。

3、在实际应用中会出现nisi深入衬底导致junction leakage(结漏电),从而导致半导体器件的测试失效。图1示出了sram失效的结构示意图,图2示出了sram正常以及失效情况下的i-v走势图,图3示出了otp结构的失效示意图,图4示出了otp结构在正常和失效情况下的i-v走势图。

4、目前inline(线上)需要检测bvc(bright voltage contrast,明电压对比),或者在efa(exploratory factor analysis,探索性因子分析)/pfa(principal factoranalysis,主因子分析)后才能发现nisi spiking的问题,存在较多误判或漏判现象,inline无法高效监控nisi深入衬底导致的漏电问题。

技术实现思路

1、本技术的主要目的在于提供一种半导体器件以及其测试方法,以解决现有技术中无法有效监控线上半导体器件是否漏电的问题。

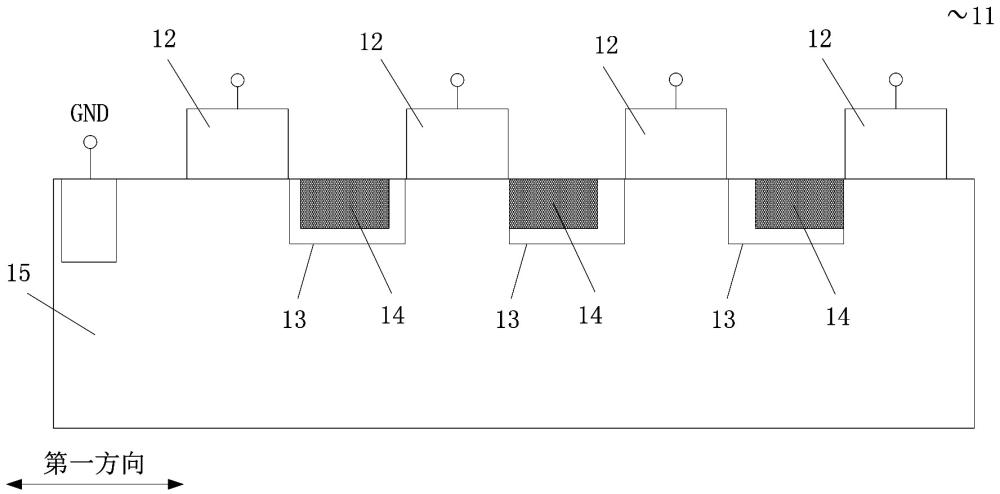

2、为了实现上述目的,根据本技术的一个方面,提供了一种半导体器件,包括:器件结构,包括mos器件,所述mos器件包括器件有源区和器件金属硅化物,所述器件金属硅化物位于所述器件有源区;测试结构,包括测试器件,所述测试器件包括多个测试栅极、至少一个测试有源区和至少一个测试金属硅化物,多个所述测试栅极间隔排列,所述测试有源区位于两个所述测试栅极之间,测试金属硅化物一一对应地位于所述测试有源区,其中,所述器件金属硅化物和所述测试金属硅化物为通过同一步骤形成的。

3、可选地,所述测试有源区和所述测试金属硅化物分别有多个,多个所述测试金属硅化物包括第一金属硅化物、第二金属硅化物和第三金属硅化物,多个所述测试栅极包括依次排列的第一测试栅极、第二测试栅极、第三测试栅极和第四测试栅极,其中,所述第一金属硅化物位于所述第一测试栅极与所述第二测试栅极之间的所述测试有源区,且所述第一金属硅化物的边缘不与所述测试有源区的边缘接触;所述第二金属硅化物位于所述第二测试栅极与所述第三测试栅极之间的所述测试有源区,且所述第二金属硅化物的左边缘与所述测试有源区的边缘接触;所述第三金属硅化物位于所述第三测试栅极与所述第四测试栅极之间的所述测试有源区中,且所述第三金属硅化物的右边缘与所述测试有源区的边缘接触,其中,所述左边缘与所述右边缘为所述测试金属硅化物沿第一方向的两个边缘,所述第一方向垂直于所述半导体器件的厚度方向。

4、可选地,多个所述测试栅极包括第五测试栅极,所述测试金属硅化物位于与所述第五测试栅极相邻的所述测试有源区中。

5、可选地,所述测试器件还包括多个第一引出线和至少一个第二引出线,所述第一引出线与所述测试栅极一一对应连接,所述第二引出线与所述测试有源区连接。

6、可选地,所述mos器件还包括器件栅极,所述器件栅极与所述器件有源区在第一方向上的距离为第一距离,所述测试栅极与所述测试有源区在所述第一方向上的距离为第二距离,所述第一距离与所述第二距离的差值小于预设值,所述第一方向垂直于所述半导体器件的厚度方向。

7、根据本技术的另一个方面,提供了一种所述的半导体器件的测试方法,包括:施加步骤,在第一目标结构上施加电压,并获取第二目标结构的电流,得到测试电流,其中,所述第一目标结构包括第一目标栅极和第一目标有源区中至少之一,在所述第一目标结构包括所述第一目标栅极的情况下,所述第二目标结构包括第二目标栅极和第二目标有源区中至少之一,在所述第一目标结构包括所述第一目标有源区的情况下,所述第二目标结构包括第三目标栅极,所述第一目标栅极、所述第二目标栅极和所述第三目标栅极均为测试栅极,所述第一目标栅极与所述第二目标栅极相邻,所述第一目标栅极与所述第二目标有源区相邻,所述第一目标有源区与所述第三目标栅极相邻,所述第一目标有源区和所述第二目标有源区均为测试有源区;第一确定步骤,根据所述测试电流,确定mos器件是否存在漏电流异常,在所述测试电流大于预设阈值的情况下,确定所述mos器件存在漏电流异常。

8、可选地,所述第一确定步骤包括:在所述测试电流大于所述预设阈值、所述第一目标结构包括所述第一目标栅极且所述第二目标结构包括所述第二目标栅极的情况下,确定所述mos器件存在沿第一方向的漏电流异常;在所述测试电流大于所述预设阈值且满足以下至少之一的情况下,确定所述mos器件存在沿第二方向的漏电流异常:所述第一目标结构包括所述第一目标有源区且所述第二目标结构包括所述第三目标栅极、所述第一目标结构包括所述第一目标栅极且所述第二目标结构包括所述第二目标有源区,其中,所述第一方向与所述第二方向垂直,所述第二方向为所述半导体器件的厚度方向。

9、可选地,所述半导体器件为所述的半导体器件,所述测试电流包括第一测试子电流、第二测试子电流和第三测试子电流,所述施加步骤包括:在第一测试栅极和第二测试栅极中之一施加所述电压,并获取所述第一测试栅极和所述第二测试栅极中另一个对应的所述电流,得到所述第一测试子电流;在所述第二测试栅极和第三测试栅极中之一施加所述电压,并获取所述第二测试栅极和所述第三测试栅极中另一个对应的所述电流,得到所述第二测试子电流;在所述第三测试栅极和第四测试栅极中之一施加所述电压,并获取所述第三测试栅极和所述第四测试栅极中另一个对应的所述电流,得到所述第三测试子电流。

10、可选地,所述第一确定步骤包括:在所述第一测试子电流、所述第二测试子电流和所述第三测试子电流分别大于所述预设阈值的情况下,确定所述mos器件存在所述漏电流异常,且漏电流方向包括左边缘指向右边缘的方向和所述右边缘指向左边缘的方向;在所述第一测试子电流和所述第三测试子电流不大于所述预设阈值且所述第二测试子电流大于所述预设阈值的情况下,确定所述mos器件存在所述漏电流异常,且所述漏电流方向为所述左边缘指向所述右边缘的方向;在所述第一测试子电流和所述第二测试子电流不大于所述预设阈值且所述第三测试子电流大于所述预设阈值的情况下,确定所述mos器件存在所述漏电流异常,且所述漏电流方向为所述右边缘指向所述左边缘的方向。

11、可选地,所述半导体器件为所述的半导体器件,所述施加步骤包括:在第五测试栅极和设置有所述测试金属硅化物的所述测试有源区中之一施加所述电压,并获取所述第五测试栅极和设置有所述测试金属硅化物的所述测试有源区中另一个对应的所述电流,得到所述测试电流,所述第一确定步骤包括:在所述测试电流大于预设阈值的情况下,确定所述mos器件存在漏电流异常,且漏电流方向为所述半导体器件的厚度方向。

12、可选地,所述方法还包括:第二确定步骤,确定与所述第一目标结构相邻的所述第一目标结构为新的所述第一目标结构;循环步骤,循环执行所述第二确定步骤、所述施加步骤和所述第一确定步骤,直到获取所有的所述第二目标结构的电流。

13、应用本技术的技术方案,本技术达到的意想不到的技术效果是:在半导体器件上设置器件结构和测试结构,且使得器件结构的器件金属硅化物和测试结构的测试金属硅化物是在同一步骤形成的,这样测试结构的金属硅化物工艺情况可以表征器件结构的金属硅化物工艺情况,通过线上测试测试结构的漏电流,来确定器件结构的漏电流,从而确定器件结构是否由于金属硅化物工艺异常造成漏电流异常,可以实现对每个半导体器件的监控,解决了无法有效监控线上半导体器件是否由于金属硅化物工艺造成漏电的问题,实现了对每个半导体器件性能的高效准确监控,避免异常品流向下个工序。

- 还没有人留言评论。精彩留言会获得点赞!