扇出型堆叠芯片封装方法及封装结构与流程

本公开实施例属于半导体封装,具体涉及一种扇出型堆叠芯片封装方法及封装结构。

背景技术:

1、消费电子产品持续的向轻薄化发展,这样也带动了对半导体器件轻薄化的需求。在手持设备中,特别是像智能手机类应用,pop(package on package,封装上封装堆叠)结构是处理器的主流封装形式。在pop中底层是处理器封装,而上层是存储器封装。目前电子产品对于存储的容量需求越来越大,对于手机类dram应用,最高已经达到16g的容量。由于单个芯片的容量有限,为实现大容量存储,需要多芯片堆叠封装。

2、目前一种超薄化方向是采用堆叠扇出封装方法,如图1中结构,通过采用芯片错位,然后通过通孔电镀工艺,形成导电柱3,可以实现多层同种芯片(芯片1和芯片2)垂直堆叠。但通孔电镀工艺成本较高,对于消费类产品,成本控制要求高。

3、于是提出了另一种堆叠扇出封装方法,该方法通过垂直打线工艺,实现芯片的垂直信号连接,替代电镀,降低成本。这种封装结构的流程是:首先将芯片通过错位方法,贴合到临时载板上,然后通过垂直悬空打线的方法,在每个芯片焊盘表面形成一个垂直键合线4,然后通过塑封,将芯片和垂直线都包裹起来,研磨塑封层表面,使垂直线暴露在塑封层外,最后在塑封层表面形成互连层,得到如图2所示的封装结构。本封装工艺的一个问题是,由于dram芯片的焊盘一般比较小,通常小于50um,因此无法使用比较粗的线,而使用细线,在形成悬空垂直线后,在做塑封时,由于塑封的流动、压力等作用会发生偏移,如图3所示,如果偏移过大,在最终形成平面互连层时,就会发生错位,导致良率下降。

4、针对上述问题,有必要提出一种设计合理且有效解决上述问题的扇出型堆叠芯片封装方法及封装结构。

技术实现思路

1、本公开实施例旨在至少解决现有技术中存在的技术问题之一,提供一种风电机组数据记录方法、装置、电子设备及存储介质。

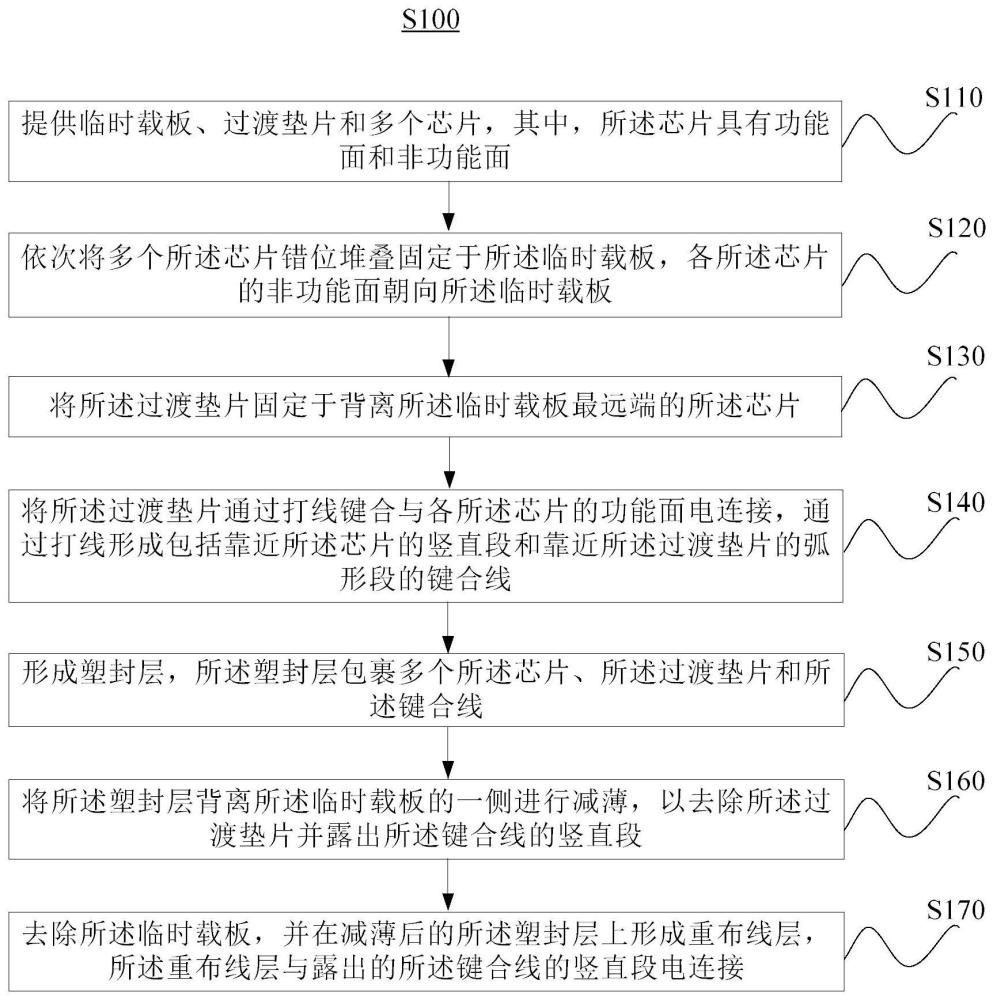

2、本公开实施例的一方面提供一种扇出型堆叠芯片封装方法,所述方法包括:

3、提供临时载板、过渡垫片和多个芯片,其中,所述芯片具有功能面和非功能面;

4、依次将多个所述芯片错位堆叠固定于所述临时载板,各所述芯片的非功能面朝向所述临时载板;

5、将所述过渡垫片固定于背离所述临时载板最远端的所述芯片;

6、将所述过渡垫片通过打线键合与各所述芯片的功能面电连接,通过打线形成包括靠近所述芯片的竖直段和靠近所述过渡垫片的弧形段的键合线;

7、形成塑封层,所述塑封层包裹多个所述芯片、所述过渡垫片和所述键合线;

8、将所述塑封层背离所述临时载板的一侧进行减薄,以去除所述过渡垫片并露出所述键合线的竖直段;

9、去除所述临时载板,并在减薄后的所述塑封层上形成重布线层,所述重布线层与露出的所述键合线的竖直段电连接。

10、可选的,所述芯片的功能面设置有第一焊盘,所述过渡垫片背离所述芯片方向的表面设置有第二焊盘;

11、所述将所述过渡垫片通过打线键合与各所述芯片的功能面电连接,通过打线形成包括靠近所述芯片的竖直段和靠近所述过渡垫片的弧形段的键合线,包括:

12、将所述键合线的第一端焊接于与其对应的所述第一焊盘,进行竖直打线形成所述竖直段;

13、沿着所述竖直段以预设弧度继续进行打线形成所述弧形段,并将所述键合线的第一端焊接于与其对应的所述第二焊盘。

14、可选的,相邻两个所述芯片中朝向所述过渡垫片的所述芯片上的所述竖直段的高度为预设高度;

15、背离所述过渡垫片的所述芯片上的所述竖直段,凸出于朝向所述过渡垫片的所述芯片的表面至少所述预设高度。

16、可选的,所述将所述过渡垫片固定于背离所述临时载板最远端的所述芯片,包括:

17、将过渡垫片通过粘结胶层固定于背离所述临时载板最远端的所述芯片。

18、可选的,所述将所述塑封层背离所述临时载板的一侧进行减薄,以去除所述过渡垫片并露出所述键合线的竖直段,包括:

19、采用研磨工艺将所述塑封层背离所述临时载板的一侧进行减薄,去除所述过渡垫片并保留部分所述粘结胶层,以露出所述键合线的竖直段。

20、可选的,所述依次将多个所述芯片错位堆叠固定于所述临时载板,包括:

21、将多个所述芯片通过贴片胶层依次错位堆叠固定,形成芯片模组;

22、将所述芯片模组通过所述芯片上的所述贴片胶层固定于所述临时载板;

23、所述形成塑封层,包括:

24、在所述临时载板朝向所述芯片的表面形成所述塑封层。

25、可选的,所述依次将多个所述芯片错位堆叠固定于所述临时载板,还包括:

26、将多个所述芯片通过贴片胶层依次错位堆叠固定,形成芯片模组;

27、将所述芯片模组通过临时键合胶层固定于所述临时载板;

28、所述形成塑封层,还包括:

29、在所述临时键合胶层上形成所述塑封层。

30、可选的,所述在减薄后的所述塑封层上形成重布线层,包括:

31、图形化所述第一介电层,在对应所述键合线的竖直段处形成开口;

32、在图形化后的所述第一介电层上形成互连金属层,所述互连金属层与所述竖直段电连接;

33、图形化所述互连金属层,并在图形化后的所述互连金属层上形成包裹所述互连金属层的第二介电层。

34、可选的,所述在减薄后的所述塑封层上形成重布线层之后,所述方法还包括:

35、在所述重布线层上形成多个焊球,形成封装体;

36、对所述封装体进行切割,形成多个独立的封装结构。

37、本公开实施例的另一方面提供一种扇出型堆叠芯片封装结构,采用前文所述的扇出型堆叠芯片封装方法封装形成。

38、本公开实施例的扇出型堆叠芯片封装方法及封装结构,该封装方法中,依次将多个芯片错位堆叠固定于临时载板后,将过渡垫片固定于背离临时载板最远端的芯片;将过渡垫片通过打线键合与各芯片的功能面电连接,通过打线形成包括靠近芯片的竖直段和靠近过渡垫片的弧形段的键合线;然后减薄塑封层露出键合线的竖直段,通过键合线的竖直段实现芯片的垂直互连。通过设置过渡垫片,可以使键合线在芯片和过渡垫片之间形成线弧,过渡垫片对键合线起到约束和定型作用,可以在进行塑封时有效减少键合线竖直段的偏移,为超薄的扇出型多层堆叠存储器封装提供了解决方案,可以有效提升封装器件的良率。另外,不需要电镀工艺,通过现有打线键合工艺就可以得到竖直键合线,实现芯片的垂直互连,减小了封装器件的封装高度,节约了成本。

技术特征:

1.一种扇出型堆叠芯片封装方法,其特征在于,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述芯片的功能面设置有第一焊盘,所述过渡垫片背离所述芯片方向的表面设置有第二焊盘;

3.根据权利要求1所述的方法,其特征在于,相邻两个所述芯片中朝向所述过渡垫片的所述芯片上的所述竖直段的高度为预设高度;

4.根据权利要求1至3任一项所述的方法,其特征在于,所述将所述过渡垫片固定于背离所述临时载板最远端的所述芯片,包括:

5.根据权利要求4所述的方法,其特征在于,所述将所述塑封层背离所述临时载板的一侧进行减薄,以去除所述过渡垫片并露出所述键合线的竖直段,包括:

6.根据权利要求1至3任一项所述的方法,其特征在于,所述依次将多个所述芯片错位堆叠固定于所述临时载板,包括:

7.根据权利要求1至3任一项所述的方法,其特征在于,所述依次将多个所述芯片错位堆叠固定于所述临时载板,还包括:

8.根据权利要求1至3任一项所述的方法,其特征在于,所述在减薄后的所述塑封层上形成重布线层,包括:

9.根据权利要求1至3任一项所述的方法,其特征在于,所述在减薄后的所述塑封层上形成重布线层之后,所述方法还包括:

10.一种扇出型堆叠芯片封装结构,其特征在于,采用权利要求1至9任一项所述的扇出型堆叠芯片封装方法封装形成。

技术总结

本公开实施例提供一种扇出型堆叠芯片封装方法及封装结构,该方法包括:依次将多个芯片错位堆叠固定于临时载板,各芯片的非功能面朝向临时载板;将过渡垫片固定于背离临时载板最远端的芯片;将过渡垫片通过打线键合与各芯片的功能面电连接,通过打线形成包括靠近芯片的竖直段和靠近过渡垫片的弧形段的键合线;形成包裹多个芯片、过渡垫片和键合线的塑封层;将塑封层背离临时载板的一侧进行减薄,以去除过渡垫片并露出键合线的竖直段;去除临时载板,并在减薄后的塑封层上形成重布线层,重布线层与露出的键合线的竖直段电连接。通过过渡垫片,可以再塑封时有效控制键合线线弧偏移,提高对位精度,提升良率,为超薄扇出型堆叠封装结构提供解决方案。

技术研发人员:杜茂华

受保护的技术使用者:通富微电子股份有限公司

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!