一种空气内侧墙堆叠纳米片环栅晶体管及制备方法

本发明涉及晶体管领域,特别涉及一种空气内侧墙堆叠纳米片环栅晶体管及制备方法。

背景技术:

1、随着晶体管特征尺寸的不断微缩,常规的cmos器件经历了由平面结构到三维结构的转变,这是在提升器件性能的同时减弱了短沟道效应带来的影响。目前主流的三维结构晶体管是finfet,而在最新发布的international roadmap for devices and systems(irds)中,纳米片环栅晶体管(nanosheet-gaafet)是3nm节点之后可以有效替代finfet的关键器件,并且可以显著抑制短沟效应,提升器件的电流驱动性能。目前,nanosheet-gaafet的研究进展受到了学术界和产业界的广泛关注。

2、堆叠nanosheet-gaa fet的制备与主流finfet的制备工艺流程兼容,相较于传统的finfet器件,由于栅极到源漏和栅极到sub-fin的面积大大增加,导致堆叠nanosheet-gaa fet器件的寄生电容急剧上升,会明显降低电路的工作速度。因此,如何降低纳米片环栅晶体管的寄生电容成为研究热点。

3、为此,提出本发明。

技术实现思路

1、本发明的主要目的在于提供一种空气内侧墙堆叠纳米片环栅晶体管及制备方法,能在nanosheet-gaa fet中源漏区与栅极之间引入具有空腔的侧墙,这样以空气替代部分固态介电材料,大幅降低了器件的寄生电容,并且工艺简单。

2、为了实现以上目的,本发明提供了以下技术方案。

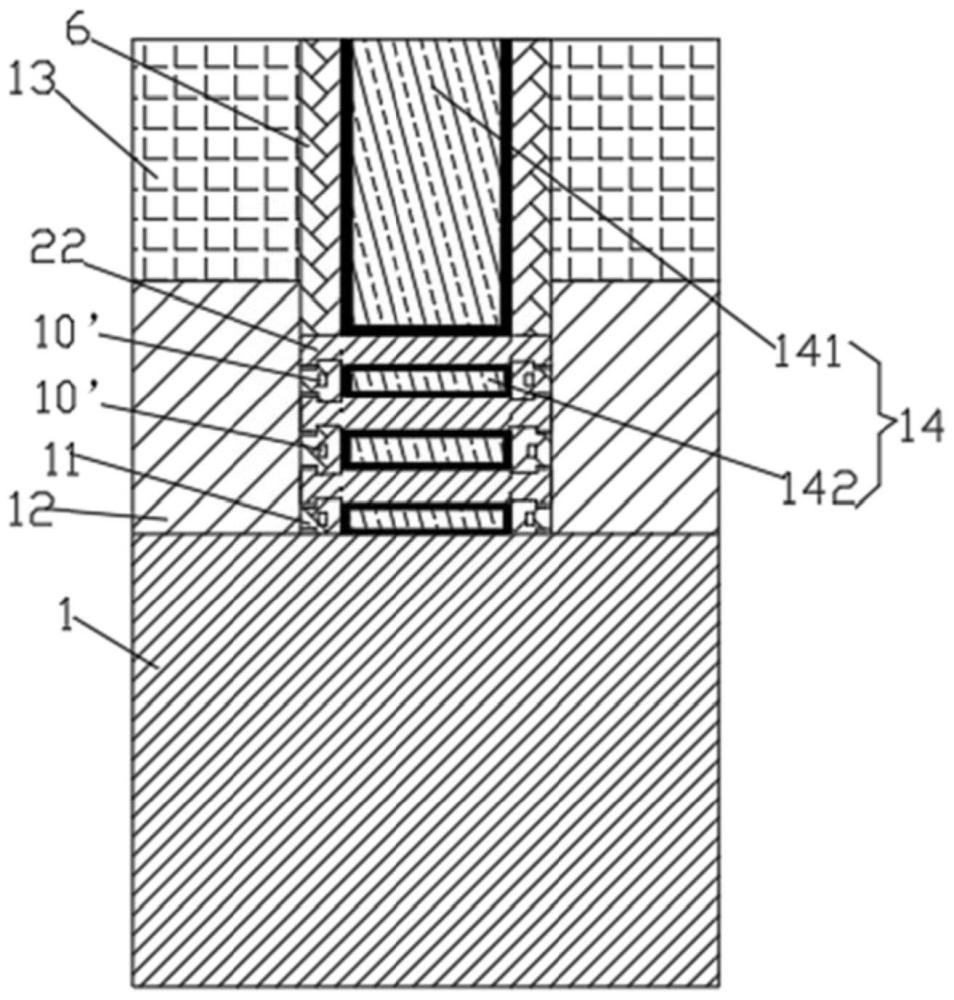

3、本发明的第一方面提供了一种空气内侧墙堆叠纳米片环栅晶体管,其包括:

4、表面具有浅沟槽隔离结构的衬底;

5、设置于所述衬底上方的纳米片堆栈部,其中,所述纳米片堆栈部包括多个纳米片形成的叠层,所述纳米片形成的叠层构成多个导电沟道;

6、环绕式栅极,其环绕所述纳米片堆栈部;

7、源漏区,位于所述纳米片堆栈部的相对的两侧,所述源漏区与环绕式栅极之间设置有侧墙;

8、所述侧墙内部含有多个空腔。

9、进一步地,还包括包围和覆盖所述环绕式栅极的第二介质层;

10、所述环绕式栅极包括填充在所述多个纳米片之间的层间栅以及包围所述纳米片堆栈部的外围栅;

11、所述侧墙包括位于所述第二介质层与所述外围栅之间的第一侧墙,以及位于所述层间栅与所述源漏区之间的第二侧墙,所述多个空腔设置在所述第二侧墙内部。

12、进一步地,每个所述空腔的体积为1nm3~9×103nm3。

13、进一步地,所述第一侧墙和所述第二侧墙各自独立地采用以下材料中的至少一种:sinx、sio2、sicn、sicon、sicox、sinox。

14、进一步地,所述浅沟槽隔离结构采用氧化硅。

15、进一步地,所述环绕式栅极包括栅介质层和金属栅层。

16、本发明的第二方面提供了一种空气内侧墙堆叠纳米片环栅晶体管的制备方法,其可用于制备第一方面的晶体管,具体包括:

17、提供衬底;

18、在所述衬底上形成牺牲层;

19、在所述牺牲层上表面形成第一半导体层;

20、在所述第一半导体层表面外延生长不同半导体材料交替层叠的超晶格叠层,所述超晶格叠层包括交替堆叠的沟道半导体层和牺牲半导体层;

21、刻蚀所述超晶格叠层以及所述第一半导体层的部分厚度,形成鳍片;

22、在所述第一半导体层上形成第一介质层,作为浅沟槽隔离,并且所述第一介质层上表面不超过所述超晶格叠层的底部;

23、在所述鳍片上沉积假栅,在所述假栅的侧壁上形成沉积第一侧墙;

24、刻蚀鳍片中的超晶格叠层,释放出源漏区域;

25、在超晶格叠层中的牺牲半导体层的侧壁形成牺牲墙;

26、回刻部分所述牺牲墙;

27、氧化超晶格叠层中的沟道半导体层的裸露的表面或者在沟道半导体层的裸露的表面沉积氧化物,得到凸出隔层;

28、去除剩余所述牺牲墙,使牺牲半导体层的侧壁裸露;

29、各向同性回刻部分超晶格叠层,形成由相邻的沟道半导体层、牺牲半导体层和凸出隔层合围成的内凹瓶结构;

30、在牺牲半导体层的侧壁的形成第二侧墙,第二侧墙在内凹瓶结构处伴随形成空腔;

31、在所述源漏区域沉积掺杂的半导体材料,形成源漏区;

32、在所述源漏区上形成第二介质层,并与所述假栅齐平;

33、去除假栅;

34、刻蚀掉所述超晶格叠层中的牺牲半导体层,实现纳米片沟道释放,所述纳米片形成的叠层构成多个导电沟道;

35、形成环绕式栅极,其环绕所述纳米片形成的叠层;

36、沉积层间介质;

37、进行互联。

38、进一步地,所述牺牲墙采用非晶碳,所述沟道半导体层采用硅,所述牺牲半导体层采用锗硅。

39、进一步地,所述填充第三介质层为:采用pecvd法填充氧化硅。

40、进一步地,所述各向同性回刻部分超晶格叠层采用以下方法中的至少一种:反应离子干法各向同性刻蚀、热原子层表面刻蚀和湿法各向同性腐蚀。例如,反应离子干法各向同性刻蚀可采用cl基等离子体,通过调整偏压方向、气压等实现各向同性刻蚀。热原子层表面刻蚀各向同性腐蚀可采用cl基或f基或cl及f基气体表面吸附,在一定温度范围内进行各向同性原子层级反应腐蚀;湿法各向同性腐蚀可采用醋酸或硝酸等溶液或混合液进行各向同性腐蚀。上述刻蚀与腐蚀时间依据所需深度进行调整。

41、与现有技术相比,本发明达到了以下技术效果:

42、(1)在源漏区与环绕式栅极之间设置侧墙,该侧墙内部具有多个空腔,空腔中充满了空气,即空气替代了传统侧墙的部分结构,以空气取代固态介质材料,可以大幅减小器件寄生电容,有效的提高器件和电路工作速度。

43、(2)源漏区与栅极之间的侧墙由空腔和固态介质材料两部分组成,这样既保证了内部精细结构具有稳定的支撑力,又可以减小寄生电容。

44、(3)通过牺牲性墙部分回刻,再选择氧化,然后去除牺牲墙,并各向同性刻蚀超晶格叠层形成内凹瓶结构,再填充内凹瓶,利用边缘瓶口填充时的垂挂效应形成具有空腔的侧墙。

技术特征:

1.一种空气内侧墙堆叠纳米片环栅晶体管,其特征在于,包括:

2.根据权利要求1所述的空气内侧墙堆叠纳米片环栅晶体管,其特征在于,还包括包围和覆盖所述环绕式栅极的第二介质层;

3.根据权利要求1所述的空气内侧墙堆叠纳米片环栅晶体管,其特征在于,每个所述空腔的体积为1nm3~9×103nm3。

4.根据权利要求1所述的空气内侧墙堆叠纳米片环栅晶体管,其特征在于,所述第一侧墙和所述第二侧墙各自独立地采用以下材料中的至少一种:sinx、sio2、sicn、sicon、sicox、sinox。

5.根据权利要求1所述的空气内侧墙堆叠纳米片环栅晶体管,其特征在于,所述浅沟槽隔离结构采用氧化硅。

6.根据权利要求1所述的空气内侧墙堆叠纳米片环栅晶体管,其特征在于,所述环绕式栅极包括栅介质层和金属栅层。

7.一种空气内侧墙堆叠纳米片环栅晶体管的制备方法,其特征在于,包括:

8.根据权利要求7所述的制备方法,其特征在于,所述牺牲墙采用非晶碳,所述沟道半导体层采用硅,所述牺牲半导体层采用锗硅。

9.根据权利要求7所述的制备方法,其特征在于,所述填充第三介质层为:采用pecvd法填充氧化硅。

10.根据权利要求7所述的制备方法,其特征在于,所述各向同性回刻部分超晶格叠层采用以下方法中的至少一种:反应离子干法各向同性刻蚀、热原子层表面刻蚀和湿法各向同性腐蚀。

技术总结

本发明涉及一种空气内侧墙堆叠纳米片环栅晶体管及制备方法。空气内侧墙堆叠纳米片环栅晶体管包括:表面具有浅沟槽隔离结构的衬底;设置于所述衬底上方的纳米片堆栈部,其中,所述纳米片堆栈部包括多个纳米片形成的叠层,所述纳米片形成的叠层构成多个导电沟道;环绕式栅极,其环绕所述纳米片堆栈部;源漏区,位于所述纳米片堆栈部的相对的两侧,所述源漏区与环绕式栅极之间设置有侧墙;所述侧墙内部含有多个空腔。本发明具有空腔的侧墙,这样以空气替代部分固态介电材料,大幅降低了器件的寄生电容,并且工艺简单。

技术研发人员:殷华湘,曹磊,李庆坤,张青竹

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/4/22

- 还没有人留言评论。精彩留言会获得点赞!