一种LED外延片及其制备方法与流程

本发明涉及激光二极管,尤其涉及一种led外延片及其制备方法。

背景技术:

1、发光二极管(light emitting diode)简称led,作为一种节能环保的新型光源,led近年来受到了很大的关注,许多国家将led相关的半导体照明视作一种战略技术。通过大量研发和实验,半导体照明技术取得了突飞猛进的发展,真正地实现了半导体照明的商业化,各种类型的led被广泛应用于指示、显示、背光、投射等领域。半导体照明取得的这些成就主要得益于gan基led相关技术的进步,相对于其它的材料体系,无论是在效率上还是在可靠性上,gan基led都有着明显的优势。

2、对于algainn材料体系来说,由于电子相比空穴具有更高的迁移率和更小的有效质量,同时电子较容易激活且具有更高的浓度,导致注入到有源区中的电子空穴浓度极其不匹配,靠近n型半导体层的量子阱几乎不发光,而电子可以轻易的注入到有源区甚至进入到p型半导体层造成电子泄漏。而且,在algainn材料体系中mg的离化率偏低,导致p型半导体材料中空穴浓度普遍较低,所以发光二极管获取高质量高空穴浓度的p型材料十分困难。此外,作为发光二极管主要功能层的电子阻挡层,除了会阻挡电子注入至p型半导体层发光之外,还会起到阻挡空穴注入至有源区的作用,进一步降低有源区中的空穴浓度,导致有源区中电子空穴浓度不匹配的问题更为严峻。因此,为了提高gan基led的发光效率,提高p型材料空穴注入效率和改善有源区中的电子空穴匹配度是十分必要的。

技术实现思路

1、本发明所要解决的技术问题在于,提供一种led外延片,能够提高p型材料空穴注入效率,改善有源区中的电子空穴匹配度,进而提高gan基led的发光效率。

2、为了解决上述技术问题,本发明第一方面提供了一种led外延片,包括衬底,还包括在所述衬底上依次层叠设置的缓冲层、n型半导体层、低温应力释放层、多量子阱发光层、多阶p型电子阻挡层、p型半导体层,

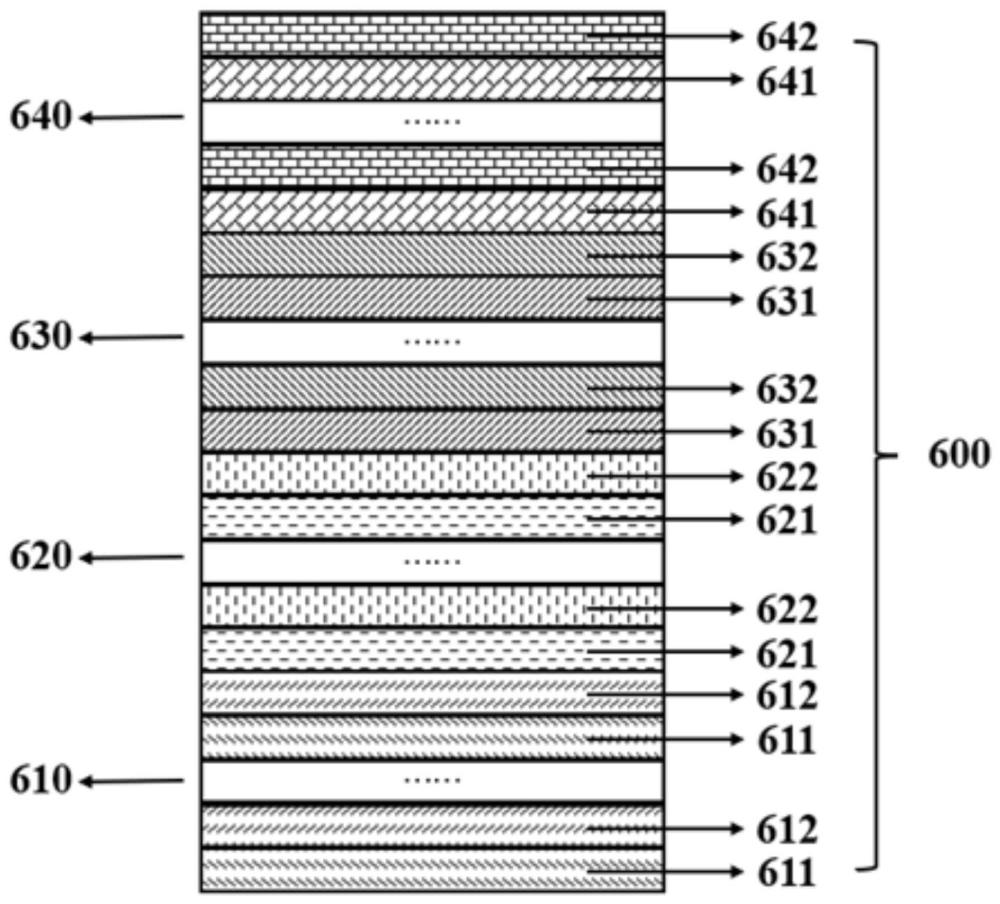

3、其中,所述多阶p型电子阻挡层包括依次层叠于所述多量子阱发光层的第一阶电子阻挡层、第二阶电子阻挡层、第三阶电子阻挡层、第四阶电子阻挡层;

4、所述第一阶电子阻挡层为交替层叠的aln层和gan层组成的超晶格结构;所述第二阶电子阻挡层为交替层叠的第一algan层和第一mg掺gan层组成的超晶格结构;所述第三阶电子阻挡层为交替层叠的第二algan层和第一mg掺ingan层组成的超晶格结构;所述第四阶电子阻挡层为交替层叠的第二mg掺gan层和第二mg掺ingan层组成的超晶格结构。

5、作为上述方案的改进,所述第一algan层中的al组分为0.4~0.8;所述第一mg掺gan层中的mg的掺杂浓度为3×1018/cm3~8×1018/cm3;

6、所述第二algan层中的al组分为0.2~0.6;所述第一mg掺ingan层中的in组分为0.03~0.09,mg的掺杂浓度为8×1018/cm3~1.2×1019/cm3;

7、所述第二mg掺gan层中的mg的掺杂浓度为1.2×1019/cm3~5×1019/cm3;所述第二mg掺ingan层中的in组分为0.09~0.15,所述mg的掺杂浓度为1.2×1019/cm3~5×1019/cm3。

8、作为上述方案的改进,所述第一algan层中的al组分≥所述第二algan层中的al组分。

9、作为上述方案的改进,所述第一mg掺ingan层中的in组分≤所述第二mg掺ingan层中的in组分。

10、作为上述方案的改进,所述第一mg掺gan层中的mg的掺杂浓度≤所述第一mg掺ingan层中的mg的掺杂浓度≤所述第二mg掺gan层中的mg的掺杂浓度和/或所述第二mg掺ingan层中的mg的掺杂浓度。

11、作为上述方案的改进,所述第一阶电子阻挡层的周期数为2~4;

12、所述第二阶电子阻挡层的周期数为2~6;

13、所述第三阶电子阻挡层的周期数为2~8;

14、所述第四阶电子阻挡层的周期数为2~10。

15、作为上述方案的改进,所述第一阶电子阻挡层的周期数≤所述第二阶电子阻挡层的周期数≤所述第三阶电子阻挡层的周期数≤所述第四阶电子阻挡层的周期数。

16、作为上述方案的改进,所述第一阶电子阻挡层中,所述aln层的厚度为2nm~8nm,所述gan层的厚度为2nm~8nm;

17、所述第二阶电子阻挡层中,所述第一algan层的厚度为2nm~8nm,所述第一mg掺gan层的厚度为2nm~8nm;

18、所述第三阶电子阻挡层中,所述第二algan层的厚度为2nm~8nm,所述第一mg掺ingan层的厚度为2nm~8nm;

19、所述第四阶电子阻挡层中,所述第二mg掺gan层的厚度为2nm~8nm,所述第二mg掺ingan层的厚度为2nm~8nm。

20、作为上述方案的改进,所述第一阶电子阻挡层的生长温度为900℃~1050℃,生长压力为20torr~300torr;

21、所述第二阶电子阻挡层的生长温度为900℃~1050℃,生长压力为20torr~300torr;

22、所述第三阶电子阻挡层的生长温度为900℃~1050℃,生长压力为20torr~300torr;

23、所述第四阶电子阻挡层的生长温度为900℃~1050℃,生长压力为20torr~300torr。

24、相应地,本发明第二方面提供了一种led外延片的制备方法,包括:

25、(1)选取一所述衬底;

26、(2)于所述衬底上生长缓冲层、n型半导体层、低温应力释放层、多量子阱发光层、多阶p型电子阻挡层、p型半导体层;

27、其中,所述多阶p型电子阻挡层包括依次层叠于所述多量子阱发光层的第一阶电子阻挡层、第二阶电子阻挡层、第三阶电子阻挡层、第四阶电子阻挡层;

28、所述第一阶电子阻挡层为交替层叠的aln层和gan层组成的超晶格结构;所述第二阶电子阻挡层为交替层叠的第一algan层和第一mg掺gan层组成的超晶格结构;所述第三阶电子阻挡层为交替层叠的第二algan层和第一mg掺ingan层组成的超晶格结构;所述第四阶电子阻挡层为交替层叠的第二mg掺gan层和第二mg掺ingan层组成的超晶格结构。

29、实施本发明,具有如下有益效果:

30、本发明中的外延片还包括设置于多量子阱发光层和p型半导体层之间的多阶p型电子阻挡层,具体包括交替层叠的aln层和gan层组成的第一阶电子阻挡层、交替层叠的第一algan层和第一mg掺gan层组成的第二阶电子阻挡层、第二algan层和第一mg掺ingan层组成的第三阶电子阻挡层以及交替层叠的第二mg掺gan层和第二mg掺ingan层组成的第四阶电子阻挡层,通过将电子阻挡层设置为四阶多层结构,可以减弱对空穴的阻挡作用,提高空穴注入效率,同时防止电子注入到p型半导体层中造成电子泄露,改善多量子阱发光层中的电子空穴匹配度,以提高led器件的发光效率和电光转化效率,并降低工作电压。

- 还没有人留言评论。精彩留言会获得点赞!