一种伪栅阵列DEMOS器件及其制作方法

本发明涉及半导体集成电路,具体是一种伪栅阵列demos器件及其制作方法。

背景技术:

1、demos(drain extended metal oxide semiconductor,漏极延伸金属氧化物半导体)是一种高压mos器件,其具有较高的击穿电压和较低的导通电阻,通常在bcd工艺中用作高压大功率模块。

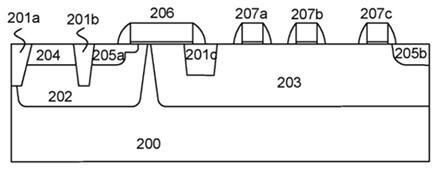

2、如图1所示,以n型器件为例,demos通常包含:

3、硅衬底,其由p型外延衬底100组成,在所述硅衬底表面形成浅沟槽隔离氧化物101a、101b和101c,由所述浅沟槽隔离氧化物隔离出demos器件有源区。

4、阱区,其由p型阱102组成。

5、漂移区,其由n型漂移区103组成。

6、栅极结构,栅极结构106由栅极氧化层、栅极多晶硅层和氮化硅侧墙组成,所述栅极结构覆盖部分p型阱102和部分n型漂移区103。

7、体区,其由p型阱102表面的p型重掺杂区104组成;

8、源区,其由p型阱102表面的n型重掺杂区105a组成,所述源区与所述栅极结构的第一侧自对准;

9、漏区,其由n型漂移区103表面的n型重掺杂区105b组成,所述漏区与所述栅极结构的第二侧相隔一段距离。

10、随着电动汽车、智能驾驶等产业的快速发展,人们对汽车芯片的高耐压和高可靠性提出了更高的要求。然而,上述传统demos器件内部电场分布不均,尖峰电场集中在栅极与漂移区交界处,极大地限制器件的击穿电压和损害器件可靠性。

技术实现思路

1、为了解决传统demos器件击穿电压偏低和可靠性不足的问题,本发明提供一种伪栅阵列demos器件及其制作方法。

2、本发明的第一方面,提供了一种伪栅阵列demos器件,包括硅衬底、阱区、源区、漏区、漂移区、伪栅阵列结构和栅极结构。在硅衬底上设有阱区和漂移区;所述栅极结构覆盖部分阱区和部分漂移区;所述源区与所述栅极结构的第一侧自对准;

3、所述伪栅阵列结构由多个伪栅结构组成,且均位于所述漂移区上方,用于调漂移区的电场,从而降低栅极与漂移区交界处的尖峰电场;

4、所述漏区与远离所述栅极结构的伪栅结构的第二侧自对准。

5、进一步说,每个所述的伪栅结构均包括栅极氧化层、栅极多晶硅层和氮化硅侧墙。

6、进一步说,所述伪栅阵列结构在靠近栅极结构的阵列密度大于远离栅极结构的阵列密度。

7、进一步说,所述的伪栅结构的偏置电压相同,且可调整。

8、本发明的第二方面,提供了一种伪栅阵列demos器件的制作方法,包括如下步骤:

9、步骤301,提供外延衬底,在衬底上局部氧化隔离,定义demos器件有源区;

10、步骤302,在demos区域分别注入p型离子和n型离子并扩散,形成器件的阱区和漂移区;

11、步骤303,生长栅氧化层,淀积多晶硅,淀积氮化硅侧墙,形成栅极结构和伪栅阵列结构;

12、步骤304,分别大剂量注入n型离子和p型离子,形成源区、漏区和体区。

13、本发明的有益效果:

14、本发明在不增加额外光罩和额外工艺步骤的情况下,设计了伪栅阵列demos器件,该器件通过在漂移区上方增加伪栅阵列,并给予伪栅不同的偏置电压,可以有效调控器件漂移区处的电场,降低栅极与漂移区交界处的尖峰电场,大幅提升器件击穿电压和可靠性。

15、此外,由于越靠近栅极,电场强度越高,所以在靠近栅极处的伪栅阵列排布较密,远离处排布较疏,这样可以在保证击穿电压和可靠性不变的情况下,减少伪栅数量,从而减小器件面积,提升芯片内器件密度。

技术特征:

1.一种伪栅阵列demos器件,其特征在于:包括硅衬底、阱区、源区、漏区、漂移区、伪栅阵列结构和栅极结构;

2.根据权利要求1所述的一种高频demos器件,其特征在于:每个所述的伪栅结构均包括栅极氧化层、栅极多晶硅层和氮化硅侧墙。

3.根据权利要求1或2所述的一种高频demos器件,其特征在于:所述伪栅阵列结构在靠近栅极结构的阵列密度大于远离栅极结构的阵列密度。

4.根据权利要求3中任一项所述的一种高频demos器件,其特征在于:所述的伪栅结构的偏置电压相同,且可调整。

5.一种权利要求1至4中任一项所述的伪栅阵列demos器件的制作方法,其特征在于包括如下步骤:

技术总结

本发明公开了一种伪栅阵列DEMOS器件及其制作方法。本发明中的伪栅阵列DEMOS器件包括硅衬底、阱区、源区、漏区、漂移区、伪栅阵列结构和栅极结构;在硅衬底上设有阱区和漂移区;所述栅极结构覆盖部分阱区和部分漂移区;所述源区与所述栅极结构的第一侧自对准;所述伪栅阵列结构由多个伪栅结构组成,且均位于所述漂移区上方,用于调漂移区的电场;所述漏区与远离所述栅极结构的伪栅结构的第二侧自对准。本发明设计了伪栅阵列DEMOS器件,该器件通过在漂移区上方增加伪栅阵列,并给予伪栅不同的偏置电压,可以有效调控器件漂移区处的电场,降低栅极与漂移区交界处的尖峰电场,大幅提升器件击穿电压和可靠性。

技术研发人员:许凯,黄霄云,吴永玉,宋逸贤,康平瑞,许成刚

受保护的技术使用者:浙江大学

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!