半导体测试结构及半导体测试方法与流程

本发明涉及半导体集成电路制造领域,特别涉及一种半导体测试结构及半导体测试方法。

背景技术:

1、栅氧的击穿是芯片中最重要的器件失效机制之一,现有的与时间相关介质击穿测试(tddb,time dependent dielectric breakdown)能够有效的对栅氧的本征寿命进行评估。

2、在现有的对栅氧的本征寿命进行评估的tddb测试结构中,一般上电极为大块的栅极层,下电极为大块的有源层,在栅极层和有源层之间为大块的栅氧层;测试时一般在栅极层上施加恒定电压,有源层接地。

3、在rfsoi工艺中,为了加强器件的隔离性,减少寄生效应,以提升晶体管速度,会在有源层与下层衬底之间设置绝缘埋层,绝缘埋层和周围的浅沟槽隔离结构会对器件进行完全的隔离。由于绝缘埋层的导热性不好(例如半导体衬底的材质为si,绝缘埋层的材质为sio2,si的导热系数为150w/mk,sio2的导热系数为7.6w/mk),而现有的对栅氧的本征寿命进行评估的tddb测试结构不会考虑周围环境导致的导热/隔热差异,因此,在rfsoi工艺中使用现有的tddb测试结构对栅氧的本征寿命进行评估时,会因为绝缘埋层的隔热效应导致器件温度高于设定温度,进而导致寿命推算不准确。

4、因此,需要对tddb测试结构进行改进,以使得对栅氧的寿命评估的更加准确。

技术实现思路

1、本发明的目的在于提供一种半导体测试结构及半导体测试方法,使得对栅氧层的寿命推测的更加准确。

2、为实现上述目的,本发明提供了一种半导体测试结构,包括:

3、衬底、栅氧层和栅极层;

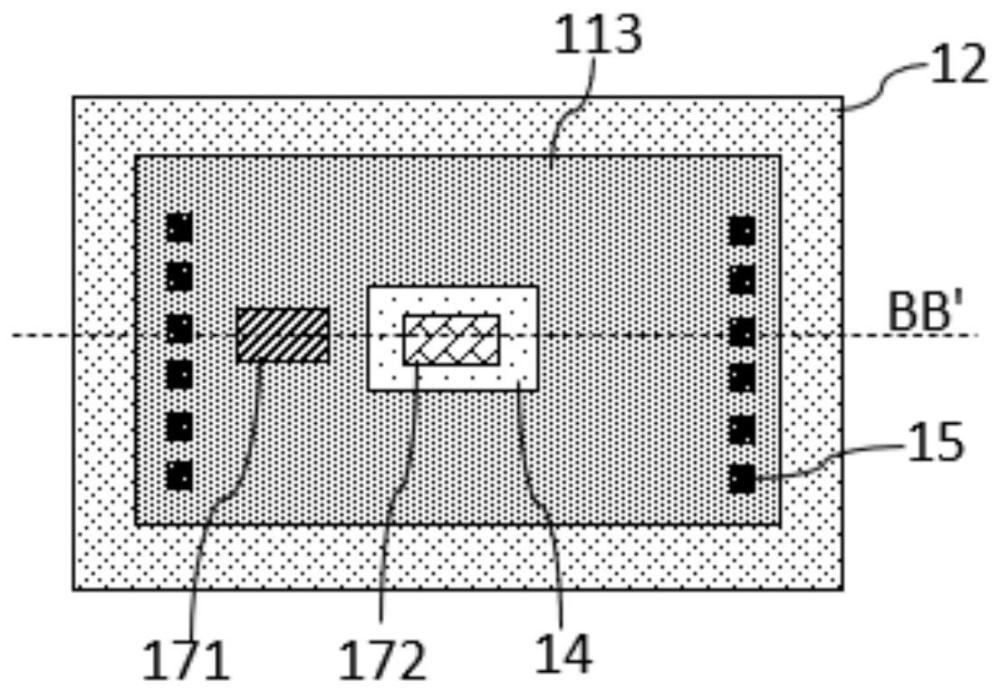

4、浅沟槽隔离结构,所述浅沟槽隔离结构所包围的所述衬底为有源区,所述栅氧层和所述栅极层自下向上形成于部分所述有源区上,所述有源区的面积与所述栅极层的面积之比大于2。

5、可选地,所述有源区的面积与所述栅极层的面积之比大于10。

6、可选地,所述衬底为体衬底,或者,所述衬底为soi衬底,所述soi衬底包括自下向上的下层衬底、绝缘埋层和半导体层。

7、可选地,所述半导体测试结构还包括:

8、层间介质层,所述层间介质层覆盖所述栅极层、所述有源区和所述浅沟槽隔离结构;

9、导热结构,所述导热结构贯穿所述层间介质层且与所述衬底接触,所述导热结构的导热系数大于所述层间介质层的导热系数。

10、可选地,所述衬底为soi衬底时,所述导热结构还贯穿所述半导体层和所述绝缘埋层,所述导热结构的导热系数大于所述绝缘埋层的导热系数。

11、可选地,所述导热结构的材质为金属材料或半导体材料,所述层间介质层和所述绝缘埋层的材质为绝缘材料。

12、可选地,所述衬底为soi衬底时,所述浅沟槽隔离结构的底面与所述绝缘埋层接触。

13、可选地,所述半导体测试结构还包括:

14、第一金属互连结构和第一焊盘,所述第一焊盘通过所述第一金属互连结构与所述有源区电连接;

15、第二金属互连结构和第二焊盘,所述第二焊盘通过所述第二金属互连结构与所述栅极层电连接。

16、可选地,所述半导体测试结构位于切割道区。

17、本发明还提供一种半导体测试方法,包括:

18、提供包含所述的半导体测试结构的待测半导体结构;

19、对所述半导体测试结构执行与时间相关介质击穿测试,以减小所述半导体测试结构的实际温度与设定温度之间的差值。

20、可选地,对所述半导体测试结构执行与时间相关介质击穿测试包括:

21、向所述栅极层施加电压且所述有源区接地,直至所述栅氧层击穿,以使得能够根据所述栅氧层击穿时对应的测试时间计算所述栅氧层的与时间相关介质击穿时间。

22、与现有技术相比,本发明的技术方案具有以下有益效果:

23、1、本发明的半导体测试结构,由于包括:衬底、栅氧层和栅极层;浅沟槽隔离结构,所述浅沟槽隔离结构所包围的所述衬底为有源区,所述栅氧层和所述栅极层自下向上形成于部分所述有源区上,所述有源区的面积与所述栅极层的面积之比大于2,使得对栅氧层的寿命推测的更加准确。

24、2、本发明的半导体测试方法,由于包括:提供包含所述的半导体测试结构的待测半导体结构;对所述半导体测试结构执行与时间相关介质击穿测试以减小所述半导体测试结构的实际温度与设定温度之间的差值,使得对栅氧层的寿命推测的更加准确。

技术特征:

1.一种半导体测试结构,其特征在于,包括:

2.如权利要求1所述的半导体测试结构,其特征在于,所述有源区的面积与所述栅极层的面积之比大于10。

3.如权利要求1所述的半导体测试结构,其特征在于,所述衬底为体衬底,或者,所述衬底为soi衬底,所述soi衬底包括自下向上的下层衬底、绝缘埋层和半导体层。

4.如权利要求3所述的半导体测试结构,其特征在于,所述半导体测试结构还包括:

5.如权利要求4所述的半导体测试结构,其特征在于,所述衬底为soi衬底时,所述导热结构还贯穿所述半导体层和所述绝缘埋层,所述导热结构的导热系数大于所述绝缘埋层的导热系数。

6.如权利要求5所述的半导体测试结构,其特征在于,所述导热结构的材质为金属材料或半导体材料,所述层间介质层和所述绝缘埋层的材质为绝缘材料。

7.如权利要求3所述的半导体测试结构,其特征在于,所述衬底为soi衬底时,所述浅沟槽隔离结构的底面与所述绝缘埋层接触。

8.如权利要求1所述的半导体测试结构,其特征在于,所述半导体测试结构还包括:

9.如权利要求1~8中任一项所述的半导体测试结构,其特征在于,所述半导体测试结构位于切割道区。

10.一种半导体测试方法,其特征在于,包括:

11.如权利要求10所述的半导体测试方法,其特征在于,对所述半导体测试结构执行与时间相关介质击穿测试包括:

技术总结

本发明提供一种半导体测试结构及半导体测试方法,半导体测试结构包括:衬底、栅氧层和栅极层;浅沟槽隔离结构,所述浅沟槽隔离结构所包围的所述衬底为有源区,所述栅氧层和所述栅极层自下向上形成于部分所述有源区上,所述有源区的面积与所述栅极层的面积之比大于2。本发明的技术方案使得对栅氧层的寿命推测的更加准确。

技术研发人员:于鹏,王帆,方明海

受保护的技术使用者:武汉新芯集成电路制造有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!