半导体结构的制备方法及半导体结构

本申请涉及半导体,涉及但不限于一种半导体结构的制备方法及半导体结构。

背景技术:

1、在摩尔定律不断深化的当下,特别是在全环绕栅(gate all around,gaa)技术节点之后,继续推进晶体管尺寸微缩是当前业界研发的热点问题。垂直晶体管让电流以垂直的方式输运,不仅可以提高晶体管的密度,还可以提高电源使用效率,被认为是延续集成电路尺寸微缩的重要技术之一。

2、然而,垂直晶体管的源极、漏极和栅极之间往往存在较大的寄生电容,例如,在源极和栅极之间以及漏极和栅极之间均存在较大的寄生电容,影响晶体管的电性能。

技术实现思路

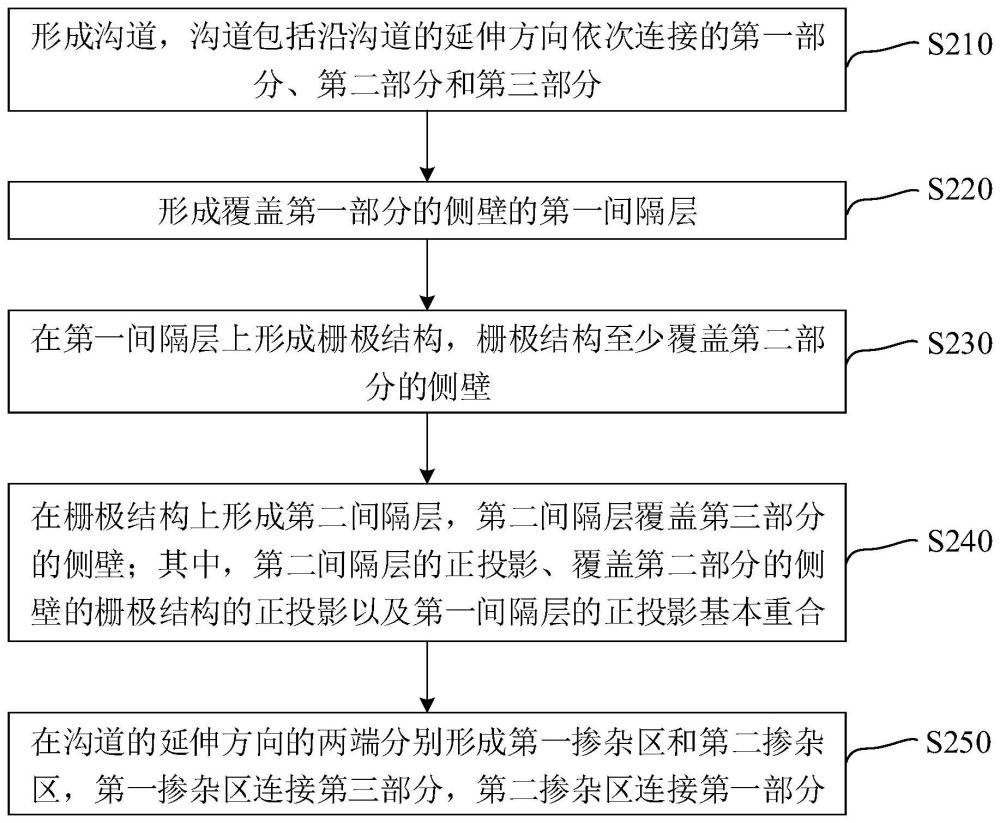

1、根据本申请实施例的第一方面,提供一种半导体结构的制备方法,包括:

2、形成沟道,所述沟道包括沿所述沟道的延伸方向依次连接的第一部分、第二部分和第三部分;

3、形成覆盖所述第一部分的侧壁的第一间隔层;

4、在所述第一间隔层上形成栅极结构,所述栅极结构至少覆盖所述第二部分的侧壁;

5、在所述栅极结构上形成第二间隔层,所述第二间隔层覆盖所述第三部分的侧壁;其中,所述第二间隔层的正投影、覆盖所述第二部分的侧壁的所述栅极结构的正投影以及所述第一间隔层的正投影基本重合;

6、在所述沟道的延伸方向的两端分别形成第一掺杂区和第二掺杂区,所述第一掺杂区连接所述第三部分,所述第二掺杂区连接所述第一部分。

7、在一些实施例中,所述形成覆盖所述第一部分的侧壁的第一间隔层,包括:

8、形成覆盖所述第一部分的侧壁的第一电介质层;

9、在所述第一电介质层上形成第二电介质层,所述第二电介质层覆盖所述第二部分的侧壁、所述第三部分的侧壁和所述第三部分的顶部;其中,所述第二电介质层的宽度小于所述第一电介质层的宽度,所述第二电介质层的材料和所述第一电介质层的材料不同;

10、以所述第二电介质层为刻蚀掩膜,刻蚀所述第一电介质层,直至去除所述第二电介质层正下方的所述第一电介质层,并在所述第二电介质层的正下方形成第一空隙;

11、填充所述第一空隙,形成所述第一间隔层;其中,所述第一间隔层的宽度和所述第二电介质层的宽度基本相同。

12、在一些实施例中,所述在所述第一间隔层上形成栅极结构,包括:

13、在形成所述第一间隔层之后,去除所述第二电介质层,暴露所述第二部分的侧壁、所述第三部分的侧壁和所述第三部分的顶部;

14、形成覆盖所述第二部分的侧壁和所述第三部分的侧壁的栅介质材料层;

15、形成覆盖所述栅介质材料层的栅极材料层;其中,所述栅极材料层和所述栅介质材料层的宽度之和基本等于所述第一间隔层的宽度;

16、沿朝向所述第一间隔层的方向,刻蚀所述栅极材料层,形成第二空隙,所述第二空隙的底部和所述第三部分的底部基本平齐;其中,保留的栅极材料层构成所述栅极结构的栅极,覆盖所述第二部分的侧壁的所述栅介质材料层构成所述栅极结构的栅介质层。

17、在一些实施例中,覆盖所述第三部分的侧壁的所述栅介质材料层构成第一子间隔层;所述在所述栅极结构上形成第二间隔层,包括:

18、填充所述第二空隙,形成第二子间隔层;其中,所述第二子间隔层和所述第一子间隔层构成所述第二间隔层,所述第二子间隔层的介电常数小于所述第一子间隔层的介电常数。

19、在一些实施例中,所述制备方法还包括:

20、在衬底上形成所述沟道,所述沟道的延伸方向和所述衬底垂直;

21、所述在所述沟道的延伸方向的两端分别形成第一掺杂区和第二掺杂区,包括:

22、形成覆盖所述第三部分和所述第二间隔层的第一掺杂区;

23、在形成所述第一掺杂区后,键合形成有所述第一掺杂区的衬底和载体晶圆,使得所述第一掺杂区位于所述衬底和所述载体晶圆之间;

24、倒置键合的所述衬底和所述载体晶圆,使得所述衬底远离所述沟道的表面朝上,去除所述衬底,暴露所述第一部分和所述第一间隔层;

25、形成覆盖所述第一部分和所述第一间隔层的第二掺杂区;其中,所述第二掺杂区和所述第一掺杂区关于所述沟道对称。

26、根据本申请实施例的第二方面,提供一种半导体结构,包括:

27、沟道,包括:沿所述沟道的延伸方向依次连接的第一部分、第二部分和第三部分;

28、第一间隔层,覆盖所述第一部分的侧壁;

29、栅极结构,位于所述第一间隔层上且至少覆盖所述第二部分的侧壁;

30、第二间隔层,位于所述栅极结构上且覆盖所述第三部分的侧壁;其中,所述第二间隔层的正投影、覆盖所述第二部分侧壁的所述栅极结构的正投影以及所述第一间隔层的正投影基本重合;

31、第一掺杂区,连接所述第三部分;

32、第二掺杂区,连接所述第一部分;其中,所述第二掺杂区和所述第一掺杂区分别位于所述沟道的延伸方向的两端。

33、在一些实施例中,所述栅极结构包括栅介质层和栅极,所述栅介质层位于所述第二部分和所述栅极之间;所述第二间隔层包括:

34、第一子间隔层,覆盖所述第三部分的侧壁;

35、第二子间隔层,覆盖所述第一子间隔层;其中,所述第二子间隔层的介电常数小于所述第一子间隔层的介电常数。

36、在一些实施例中,所述第一子间隔层的宽度和所述栅介质层的宽度相同,所述第二子间隔层的宽度和所述栅极的宽度相同。

37、在一些实施例中,所述第二子间隔层的材料和所述第一间隔层的材料相同。

38、在一些实施例中,所述第一间隔层的材料包括硅碳氮化物、硅氧氮化物、掺杂硅碳氮化物、掺杂硅氧氮化物中的至少一种。

39、本申请实施例提供的制备方法中,通过形成沟道,沟道包括沿沟道的延伸方向依次连接的第一部分、第二部分和第三部分;形成覆盖第一部分的侧壁的第一间隔层;在第一间隔层上形成栅极结构,栅极结构至少覆盖第二部分的侧壁;在栅极结构上形成第二间隔层,第二间隔层覆盖第三部分的侧壁;其中,第二间隔层的正投影、覆盖第二部分的侧壁的栅极结构的正投影以及第一间隔层的正投影基本重合;在沟道的延伸方向的两端分别形成第一掺杂区和第二掺杂区,第一掺杂区连接第三部分,第二掺杂区连接第一部分。如此,第一间隔层的宽度较小,有利于减小栅极和第二掺杂区之间的寄生电容;并且第一间隔层和第二间隔层高度对称,有效降低栅极和源极之间的寄生电容以及栅极和漏极之间的寄生电容的非对称性,改善晶体管的电性能。

40、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本申请。

技术特征:

1.一种半导体结构的制备方法,其特征在于,包括:

2.根据权利要求1所述的制备方法,其特征在于,所述形成覆盖所述第一部分的侧壁的第一间隔层,包括:

3.根据权利要求2所述的制备方法,其特征在于,所述在所述第一间隔层上形成栅极结构,包括:

4.根据权利要求3所述的制备方法,其特征在于,覆盖所述第三部分的侧壁的所述栅介质材料层构成第一子间隔层;所述在所述栅极结构上形成第二间隔层,包括:

5.根据权利要求1所述的制备方法,其特征在于,所述制备方法还包括:

6.一种半导体结构,其特征在于,包括:

7.根据权利要求6所述的半导体结构,其特征在于,所述栅极结构包括栅介质层和栅极,所述栅介质层位于所述第二部分和所述栅极之间;所述第二间隔层包括:

8.根据权利要求7所述的半导体结构,其特征在于,所述第一子间隔层的宽度和所述栅介质层的宽度相同,所述第二子间隔层的宽度和所述栅极的宽度相同。

9.根据权利要求7所述的半导体结构,其特征在于,所述第二子间隔层的材料和所述第一间隔层的材料相同。

10.根据权利要求6或9所述的半导体结构,其特征在于,所述第一间隔层的材料包括硅碳氮化物、硅氧氮化物、掺杂硅碳氮化物、掺杂硅氧氮化物中的至少一种。

技术总结

本申请提供一种半导体结构的制备方法及半导体结构,该半导体结构的制备方法包括:形成沟道,沟道包括沿沟道的延伸方向依次连接的第一部分、第二部分和第三部分;形成覆盖第一部分的侧壁的第一间隔层;在第一间隔层上形成栅极结构,栅极结构至少覆盖第二部分的侧壁;在栅极结构上形成第二间隔层,第二间隔层覆盖第三部分的侧壁;其中,第二间隔层的正投影、覆盖第二部分的侧壁的栅极结构的正投影以及第一间隔层的正投影基本重合;在沟道的延伸方向的两端分别形成第一掺杂区和第二掺杂区,第一掺杂区连接第三部分,第二掺杂区连接第一部分。

技术研发人员:吴恒,王逸勐,滕飞宇,黄如,王润声,黎明

受保护的技术使用者:北京大学

技术研发日:

技术公布日:2024/3/12

- 还没有人留言评论。精彩留言会获得点赞!