半导体结构及其制备方法、半导体器件与流程

本申请属于半导体,尤其涉及一种半导体结构及其制备方法、半导体器件。

背景技术:

1、在半导体器件制造工艺中,包括顶层的金属互联层和形成于顶层的金属互联层的焊盘,焊盘用于进行封装测试。当前制备工艺中,焊盘表面的平整度较差,严重影响后续的封装工艺的良率。

技术实现思路

1、本申请实施例提供了一种半导体结构及其制备方法、半导体器件,可提升后续电连接的稳定性和可靠性,以使得电连接良率得以提升。

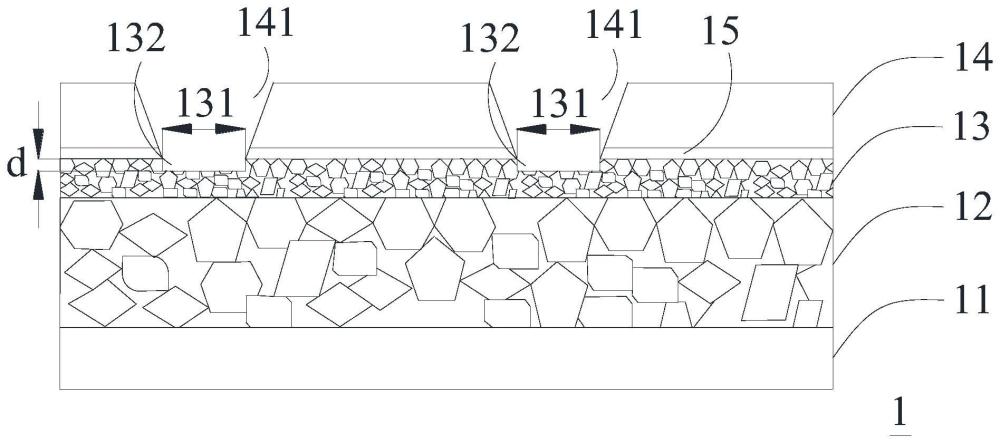

2、本申请实施例第一方面的实施例提供了一种半导体结构,包括:

3、衬底;

4、第一金属层,形成于所述衬底一侧;

5、第二金属层,形成于所述第一金属层背离所述衬底一侧,所述第一金属层内的晶粒尺寸大于所述第二金属层内的晶粒尺寸,所述第二金属层包括多个焊盘区。

6、根据本发明第一方面的实施方式,沿垂直于所述衬底方向,所述第二金属层的厚度小于所述第一金属层的厚度。

7、根据本发明第一方面前述任一实施方式,所述第二金属层的材料包括铝,沿垂直于所述衬底厚度方向,所述第二金属层的厚度为50nm-300nm;

8、所述第一金属层的材料包括铝。

9、根据本发明第一方面前述任一实施方式,还包括钝化层,所述钝化层位于所述第二金属层背离所述第一金属层的一侧,所述钝化层包括开口部,所述开口部暴露所述焊盘区中的至少部分。

10、根据本发明第一方面前述任一实施方式,所述焊盘区包括凹槽部,沿垂直于所述衬底方向,所述凹槽部的深度小于20nm。

11、根据本发明第一方面前述任一实施方式,还包括粘合层,位于所述第二金属层与所述钝化层之间,所述粘合层的材质包括钛或氮化钛。

12、本申请第二方面的实施例还提供了一种半导体结构的制备方法,包括:

13、提供衬底;

14、在所述衬底一侧形成第一金属层;

15、在所述第一金属层背离所述衬底一侧形成第二金属层,所述第一金属层内的晶粒尺寸大于所述第二金属层内的晶粒尺寸,所述第二金属层包括多个焊盘区。

16、根据本发明第二方面的实施方式,所述第一金属层和所述第二金属层分别通过沉积工艺制备形成,所述第一金属层的沉积速率大于所述第二金属层的沉积速率,所述第一金属层的沉积温度小于所述第二金属层的沉积温度。

17、根据本发明第二方面前述任一实施方式,还包括沉积形成钝化层并对所述钝化层图案化以形成开口部,所述钝化层位于所述第二金属层背离所述第一金属层一侧。

18、本申请第三方面的实施例还提供了一种半导体器件,包括本申请第一方面提供的任意一种半导体结构。

19、本申请提供的半导体结构中,金属互联层包括层叠设置的第一金属层和第二金属层,第二金属层形成于第一金属层背离衬底一侧,第一金属层内的晶粒尺寸大于第二金属层内的晶粒尺寸,第二金属层包括多个焊盘区,使得第二金属层在后续工艺暴露焊盘区以便于实现电连接的过程中,由于第二金属层内的晶粒尺寸较小,从而可降低相邻晶粒之间位置处的刻蚀速度与晶粒处刻蚀速度的差异,从而提升焊盘区的表面平整度,以提升后续电连接的可靠性和稳定性,即提升电连接的良率。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.根据权利要求1所述的半导体结构,其特征在于,沿垂直于所述衬底方向,所述第二金属层的厚度小于所述第一金属层的厚度。

3.根据权利要求1所述的半导体结构,其特征在于,所述第二金属层的材料包括铝,沿垂直于所述衬底厚度方向,所述第二金属层的厚度为50nm-300nm;

4.根据权利要求1所述的半导体结构,其特征在于,还包括钝化层,所述钝化层位于所述第二金属层背离所述第一金属层的一侧,所述钝化层包括开口部,所述开口部暴露所述焊盘区中的至少部分。

5.根据权利要求1所述的半导体结构,其特征在于,所述焊盘区包括凹槽部,沿垂直于所述衬底方向,所述凹槽部的深度小于20nm。

6.根据权利要求1所述的半导体结构,其特征在于,还包括粘合层,位于所述第二金属层与所述钝化层之间,所述粘合层的材质包括钛或氮化钛。

7.一种半导体结构的制备方法,其特征在于,包括:

8.根据权利要求7所述的制备方法,其特征在于,所述第一金属层和所述第二金属层分别通过沉积工艺制备形成,所述第一金属层的沉积速率大于所述第二金属层的沉积速率,所述第一金属层的沉积温度小于所述第二金属层的沉积温度。

9.根据权利要求7所述的,其特征在于,还包括沉积形成钝化层并对所述钝化层图案化以形成开口部,所述钝化层位于所述第二金属层背离所述第一金属层一侧。

10.一种半导体器件,包括权利要求1-7任一项所述的半导体结构。

技术总结

本申请公开了一种半导体结构及其制备方法、半导体器件,半导体结构包括衬底、第一金属层和第二金属层,第一金属层形成于衬底一侧;第二金属层形成于第一金属层背离衬底一侧,第一金属层内的晶粒尺寸大于第二金属层内的晶粒尺寸,第二金属层包括多个焊盘区。本申请提供的半导体结构中由于第二金属层内的晶粒尺寸较小,从而可降低相邻晶粒之间位置处的刻蚀速度与晶粒处刻蚀速度的差异,从而提升焊盘区的表面平整度,以提升后续电连接的可靠性和稳定性,即提升电连接的良率。

技术研发人员:赵勇

受保护的技术使用者:苏州华太电子技术股份有限公司

技术研发日:

技术公布日:2024/3/12

- 还没有人留言评论。精彩留言会获得点赞!