一种芯片及其测试方法、相关装置与流程

本发明涉及集成电路,尤其涉及一种芯片及其测试方法、相关装置。

背景技术:

1、随着目前的芯片复杂度和集成度越来越高,基于工艺和生产制造良率以及晶粒(die)复用等各方面的权衡考虑,在单个芯片封装中,封装多颗晶粒开始成为主流,比如chiplet(芯粒),这给芯片的生产测试带来了新的挑战。

2、对单晶粒封装的芯片测试,是将此芯片的多个管脚引出到封装外部与测试设备相连,用于生产测试,一般情况下其管脚数量比较多足以满足测试需求。

3、在多晶粒封装芯片的测试场景中,如果按照传统单晶粒封装芯片的测试方式,每个晶粒都引出足够多的管脚到封装外部的话,必然会增加芯片的测试成本。而且封装内部可能还会有些晶粒本身引出到封装外部的功能管脚数量很少,甚至完全不会引出管脚到封装外面,按照传统方式需要加入大量的测试专用管脚引出到封装外部,因此成本较高。

技术实现思路

1、有鉴于此,本发明实施例提供一种芯片及其测试方法、相关装置,能够有效降低芯片的测试成本。

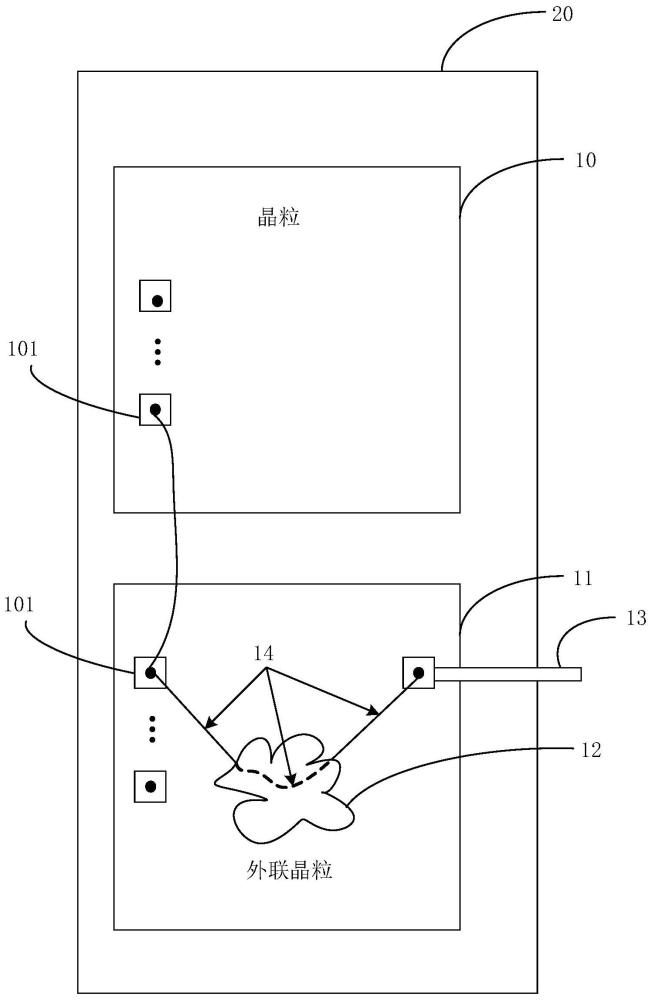

2、第一方面,本发明实施例提供一种芯片,包括:至少两个晶粒,所述至少两个晶粒被封装在同一个封装体中;在所述至少两个晶粒中,每个晶粒都与另外的、至少一个晶粒互连,并在每个晶粒中形成对应的互连节点;所述至少两个晶粒包括至少一个外联晶粒,每个所述外联晶粒中设置有至少一个引出管脚和电通路,其中,所述电通路的一端电连接于该外联晶粒的至少一个所述互连节点,另一端向该外联晶粒内部延伸,并经由第一通路切换网络与所述外联晶粒的所述引出管脚电连接;所述第一通路切换网络用于,对该电通路进行延伸方向的调整,以将所述互连节点与所述引出管脚电连接;其中,所述引出管脚被引出到所述封装体的外部。

3、在一种实施方式中,所述至少两个晶粒还包括至少一个内联晶粒,每个所述内联晶粒直接与所述外联晶粒电连接,或者通过一个或多个其他内联晶粒与所述外联晶粒电连接;每个所述内联晶粒中设置有电通路,该电通路一端电连接于所述内联晶粒的第一互连节点,另一端向该内联晶粒内部延伸,并经由第二通路切换网络电连接于该内联晶粒的第二互连节点,所述第二通路切换网络用于,对该电通路进行延伸方向的调整,以将所述第一互连节点与所述第二互连节点电连接,其中,所述第一互连节点为所述内联晶粒的、与所述封装体中的一个晶粒的互连节点,所述第二互连节点为所述内联晶粒的、与所述封装体中的另一个晶粒的互连节点。

4、在一种实施方式中,所述外联晶粒包括目标外联晶粒;所述目标外联晶粒的至少一个引出管脚被配置为,一端与测试设备电连接,另一端通过所述目标外联晶粒中的电通路所经由的第一通路切换网络,与目标外联晶粒中的目标互连节点电连接,以对所述目标互连节点关联的待测晶粒进行测试。

5、在一种实施方式中,所述目标互连节点与所述待测晶粒直接电连接;或者,所述至少两个晶粒还包括至少一个内联晶粒,所述目标互连节点通过一个或多个所述内联晶粒,与所述待测晶粒电连接。

6、在一种实施方式中,所述目标互连节点通过一个或多个内联晶粒,与所述待测晶粒电连接;所述一个或多个内联晶粒,通过各自的电通路所经由的第二通路切换网络对各自的所述电通路进行调整,以使各自的所述电通路穿过所在的内联晶粒,彼此电连接,形成串联通路,所述串联通路一端与所述目标互连节点电连接,另一端与所述待测晶粒电连接。

7、在一种实施方式中,所述目标外联晶粒的数量为至少两个;各所述目标外联晶粒的目标互连节点与所述待测晶粒之间分别形成对应的所述串联通路,不同目标外联晶粒的目标互连节点,对应的所述串联通路所经过的内联晶粒相同或不同。

8、在一种实施方式中,所述目标外联晶粒包括第一外联晶粒和第二外联晶粒;所述第一外联晶粒的目标互连节点对应第一串联通路,所述第二外联晶粒的目标互连节点对应第二串联通路;所述第一串联通路与所述第二串联通路所经过的内联晶粒相同,其中,每个所述内联晶粒的电通路所经由的第二通路切换网络被配置为:对第一电通路和第二电通路的延伸方向分别进行调整,以使各第一电通路穿过所在的内联晶粒,彼此电连接,形成所述第一串联通路,且使各第二电通路穿过所在的内联晶粒,彼此电连接,形成所述第二串联通路。

9、在一种实施方式中,所述引出管脚包括输入型引出管脚和/或输出型引出管脚;所述输入型引出管脚被配置为接收所述测试设备发送的测试信息,所述测试信息包括测试程序和/或测试数据;其中,所述测试信息从所述输入型引出管脚,沿所述电通路穿过所述目标外联晶粒,传入所述待测晶粒;所述输出型引出管脚被配置为向所述测试设备发送测试反馈信息,所述测试反馈信息包括测试中间信息和/或测试结果,其中,所述测试反馈信息从所述待测晶粒传输到关联的所述目标互连节点,沿所述目标外联晶粒中的电通路穿过所述目标外联晶粒,传入所述测试设备。

10、在一种实施方式中,所述待测晶粒包括处理模块,所述处理模块被配置为执行以下至少一项:通过所述目标外联晶粒接收所述测试设备发送的测试信息,并根据所述测试信息执行测试操作,其中,所述测试信息包括测试程序和/或测试数据;根据内置在所述芯片中的测试信息,执行测试操作,其中,所述测试信息可以包括测试程序和/或测试数据;将执行测试操作中形成的测试反馈信息,通过所述目标外联晶粒向所述测试设备发送,其中,所述测试反馈信息包括测试中间信息和/或测试结果。

11、在一种实施方式中,所述待测晶粒为所述内联晶粒;所述待测晶粒中的所述电通路所经由的所述第二通路切换网络被配置为:在对所述待测晶粒测试的情况下,调整所述待测晶粒中的所述电通路的延伸方向,以使所述电通路一端与所述处理模块电连接,另一端从所述待测晶粒引出,以与所述目标外联晶粒电连接;或者,在对其他晶粒进行辅助测试的情况下,调整所述待测晶粒中的所述电通路的延伸方向,以使所述电通路穿过所述待测晶粒,两端都从所述待测晶粒引出。

12、在一种实施方式中,所述待测晶粒为外联晶粒,所述待测晶粒中的所述电通路所经由的所述第一通路切换网络被配置为:在对所述待测晶粒测试的情况下,调整所述待测晶粒中的所述电通路的延伸方向,以使所述电通路一端与所述处理模块电连接,另一端从所述待测晶粒引出,以与所述目标外联晶粒电连接;或者,在对其他晶粒进行辅助测试的情况下,调整所述待测晶粒中的所述电通路的延伸方向,以使所述电通路一端与所述待测晶粒的所述引出管脚电连接,另一端从所述待测晶粒引出,以与被辅助的所述其他晶粒电连接。

13、在一种实施方式中,所述第一通路切换网络包括多路开关形成的开关网络,或者查找表;所述第二通路切换网络包括多路开关形成的开关网络,或者查找表。

14、在一种实施方式中,所述互连节点包括以下至少一种:焊盘互连节点、硅通孔互连节点。

15、第二方面,本发明的实施例还提供一种芯片的测试方法,所述芯片为前述第一方面所提供的芯片,所述方法包括:获取所述芯片中各晶粒的互连信息,所述互连信息包括以下至少一项:晶粒内的第一互连信息、晶粒之间的第二互连信息、晶粒与芯片外部的第三互连信息;根据所述互连信息,确定所述芯片中,为待测晶粒提供测试通路的辅助晶粒;对所述辅助晶粒中的所述电通路所经由的所述第一通路切换网络进行配置,以通过所述第一通路切换网络,在所述待测晶粒与测试设备之间建立测试通路;基于所述测试通路测试所述待测晶粒。

16、在一种实施方式中,所述根据所述互连信息,确定所述芯片中,为待测晶粒提供测试通路的辅助晶粒包括:根据所述互连信息,查找与所述待测晶粒直接互连的第一互连晶粒;确定所述第一互连晶粒中的电通路是否经由所述第一通路切换网络;响应于所述第一互连晶粒中的电通路经由所述第一通路切换网络,将所述第一互连晶粒确定为辅助晶粒。

17、在一种实施方式中,所述芯片中,所述至少两个晶粒还包括至少一个内联晶粒,每个所述内联晶粒直接与所述外联晶粒电连接,或者通过一个或多个其他内联晶粒与所述外联晶粒电连接;每个所述内联晶粒中设置有电通路,该电通路一端电连接于所述内联晶粒的第一互连节点,另一端向该内联晶粒内部延伸,并经由第二通路切换网络电连接于该内联晶粒的第二互连节点,所述第二通路切换网络用于,对该电通路进行延伸方向的调整,以将所述第一互连节点与所述第二互连节点电连接,其中,所述第一互连节点为所述内联晶粒的、与所述封装体中的一个晶粒的互连节点,所述第二互连节点为所述内联晶粒的、与所述封装体中的另一个晶粒的互连节点;所述方法还包括:响应于所述第一互连晶粒中的电通路不经由所述第一通路切换网络,确定所述第一互连晶粒中的电通路是否经由所述第二通路切换网络;在所述第一互连晶粒中的电通路经由所述第二通路切换网络的情况下,确定所述第一互连晶粒为备选晶粒;确定除所述待测晶粒外的、与所述备选晶粒直接互连的晶粒,为第二互连晶粒;以所述第二互连晶粒作为新的所述第一互连晶粒,跳转到所述确定所述第一互连晶粒中的电通路是否经由所述第一通路切换网络的步骤继续执行,直到将其中一个所述备选晶粒确定为所述辅助晶粒为止;将与所述辅助晶粒互连的各所述备选晶粒,均确定为所述辅助晶粒。

18、在一种实施方式中,所述对所述辅助晶粒中的所述电通路所经由的所述第一通路切换网络进行配置包括:对所述辅助晶粒中的所述电通路所经由的第一通路切换网络或所述辅助晶粒中的所述电通路所经由的第二通路切换网络进行配置。

19、在一种实施方式中,所述对所述辅助晶粒中的所述电通路所经由的第一通路切换网络或所述辅助晶粒中的所述电通路所经由的第二通路切换网络进行配置包括:通过预设接口向所述辅助晶粒发送配置指令,基于所述配置指令配置所述第一通路切换网络或所述第二通路切换网络,其中,所述预设接口包括以下至少一种:联合测试行动组接口(jtag,joint test action group)、集成电路总线接口(i2c,inter-integrated circuit)、通用异步收发传输器接口(uart,universal asynchronous receiver/transmitter,)、通用串行总线接口(usb,universal serial bus)、外围器件互联接口(pci,peripheralcomponent interconnect)。

20、在一种实施方式中,所述待测晶粒为外联晶粒或内联晶粒;所述待测晶粒包括处理模块;所述基于所述测试通路测试所述待测晶粒之前,所述方法还包括:配置所述待测晶粒中的电通路所经由的第一通路切换网络或第二通路切换网络,以调整所述待测晶粒中的所述电通路的延伸方向,使所述电通路一端与所述处理模块电连接,另一端从所述待测晶粒引出,以与所述辅助晶粒电连接。

21、在一种实施方式中,所述基于所述测试通路测试所述待测晶粒包括以下至少一项:通过所述测试通路向所述待测晶粒发送测试信息,所述测试信息包括测试程序和/或测试数据;通过所述测试通路接收所述待测晶粒发送的测试反馈信息,所述测试反馈信息包括测试中间信息和/或测试中间结果。

22、第三方面,本发明的实施例还提供一种芯片的测试装置,所述芯片为前述第一方面所提供的芯片,所述装置包括:获取单元,用于获取所述芯片中各晶粒的互连信息,所述互连信息包括以下至少一项:晶粒内的第一互连信息、晶粒之间的第二互连信息、晶粒与芯片外部的第三互连信息;确定单元,用于根据所述互连信息,确定所述芯片中,为待测晶粒提供测试通路的辅助晶粒;第一配置单元,用于对所述辅助晶粒中的所述电通路所经由的所述第一通路切换网络进行配置,以通过所述第一通路切换网络,在所述待测晶粒与测试设备之间建立测试通路;测试单元,用于基于所述测试通路测试所述待测晶粒。

23、在一种实施方式中,所述确定单元包括:查找模块,用于根据所述互连信息,查找与所述待测晶粒直接互连的第一互连晶粒;第一确定模块,用于确定所述第一互连晶粒中的电通路是否经由所述第一通路切换网络;第二确定模块,用于响应于所述第一互连晶粒中的电通路经由所述第一通路切换网络,将所述第一互连晶粒确定为辅助晶粒。

24、在一种实施方式中,所述芯片中,所述至少两个晶粒还包括至少一个内联晶粒,每个所述内联晶粒直接与所述外联晶粒电连接,或者通过一个或多个其他内联晶粒与所述外联晶粒电连接;每个所述内联晶粒中设置有电通路,该电通路一端电连接于所述内联晶粒的第一互连节点,另一端向该内联晶粒内部延伸,并经由第二通路切换网络电连接于该内联晶粒的第二互连节点,所述第二通路切换网络用于,对该电通路进行延伸方向的调整,以将所述第一互连节点与所述第二互连节点电连接,其中,所述第一互连节点为所述内联晶粒的、与所述封装体中的一个晶粒的互连节点,所述第二互连节点为所述内联晶粒的、与所述封装体中的另一个晶粒的互连节点;所述确定单元还包括:第三确定模块,用于响应于所述第一互连晶粒中的电通路不经由所述第一通路切换网络,确定所述第一互连晶粒中的电通路是否经由所述第二通路切换网络;第三确定模块,用于在所述第一互连晶粒中的电通路经由所述第二通路切换网络的情况下,确定所述第一互连晶粒为备选晶粒;第五确定模块,用于确定除所述待测晶粒外的、与所述备选晶粒直接互连的晶粒,为第二互连晶粒;触发模块,用于以所述第二互连晶粒作为新的所述第一互连晶粒,触发所述第一确定模块执行相应操作,直到将其中一个所述备选晶粒确定为所述辅助晶粒为止;第六确定模块,用于将与所述辅助晶粒互连的各所述备选晶粒,均确定为所述辅助晶粒。

25、在一种实施方式中,所述第一配置单元,具体用于对所述辅助晶粒中的所述电通路所经由的第一通路切换网络或所述辅助晶粒中的所述电通路所经由的第二通路切换网络进行配置。

26、在一种实施方式中,所述第一配置单元,具体用于通过预设接口向所述辅助晶粒发送配置指令,基于所述配置指令配置所述第一通路切换网络或所述第二通路切换网络,其中,所述预设接口包括以下至少一种:联合测试行动组接口、集成电路总线接口、通用异步收发传输器接口、通用串行总线接口、外围器件互联接口。

27、在一种实施方式中,所述待测晶粒为外联晶粒或内联晶粒;所述待测晶粒包括处理模块;所述装置还包括第二配置单元,用于在基于所述测试通路测试所述待测晶粒之前,配置所述待测晶粒中的所述电通路所经由的第一通路切换网络或第二通路切换网络,以调整所述待测晶粒中的所述电通路的延伸方向,使所述电通路一端与所述处理模块电连接,另一端从所述待测晶粒引出,以与所述辅助晶粒电连接。

28、在一种实施方式中,所述测试单元,具体用于以下至少一项:通过所述测试通路向所述待测晶粒发送测试信息,所述测试信息包括测试程序和/或测试数据;通过所述测试通路接收所述待测晶粒发送的测试反馈信息,所述测试反馈信息包括测试中间信息和/或测试中间结果。

29、第四方面,本发明的实施例还提供一种测试系统,包括:芯片和测试设备;其中,所述芯片为本发明的实施例提供的任一种芯片;所述测试设备与所述芯片通过预设接口电连接,通过所述预设接口对所述芯片进行配置,以在所述芯片中的待测晶粒与所述芯片中的外联晶粒的引出管脚之间建立测试通路;所述测试设备还与所述引出管脚电连接,以执行以下至少一项:通过所述引出管脚向所述待测晶粒发送测试信息,所述测试信息包括测试程序和/或测试数据;通过所述引出管脚接收所述待测晶粒发送的测试反馈信息,所述测试反馈信息包括测试中间信息和/或测试中间结果;所述芯片被配置为执行以下至少一项:所述待测晶粒通过所述外联晶粒的所述引出管脚接收所述测试设备发送的测试信息,并根据所述测试信息执行测试操作;所述待测晶粒根据内置在所述芯片中的测试信息,执行测试操作;所述待测晶粒将执行测试操作中形成的测试反馈信息,通过所述外联晶粒的所述引出管脚向所述测试设备发送。

30、第五方面,本发明的实施例还提供一种电子设备,所述电子设备包括:壳体、处理器、存储器、电路板和电源电路,其中,电路板安置在壳体围成的空间内部,处理器和存储器设置在电路板上;电源电路,用于为上述电子设备的各个电路或器件供电;存储器用于存储可执行程序代码;处理器通过读取存储器中存储的可执行程序代码来运行与可执行程序代码对应的程序,用于执行本发明的任一实施例提供的芯片的测试方法。

31、第六方面,本发明的实施例还提供一种计算机可读存储介质,所述计算机可读存储介质存储有一个或者多个程序,所述一个或者多个程序可被一个或者多个处理器执行,以实现本发明的任一实施例提供的芯片的测试方法。

- 还没有人留言评论。精彩留言会获得点赞!