一种减少EMI噪声的功率器件及制备方法与流程

本发明涉及半导体器件领域,尤其是一种减少emi噪声的功率器件及制备方法。

背景技术:

1、igbt器件是一种大功率半导体分立器件,结合了mos器件高开关频率,易于控制和bjt器件的大电流处理能力能等优点,在工业变频、消费电子、轨道交通、新能源、航天航空等领域有着广泛的应用。

2、igbt器件导通前期,集电极会向漂移区注入大量空穴,空穴会聚集在有源栅极下侧,当igbt器件开通瞬间,聚集在有源栅极附近的空穴会产生位移电流,从而引起栅极电压的振荡,使器件产生emi(electromagnetic interference)噪声。igbt器件关断时,大量注入漂移区的空穴无法快速去除而造成电流拖尾现象,增大了器件的关断损耗。因此,如何降低igbt器件的开关损耗并抑制emi噪声是亟需待解决的问题。

技术实现思路

1、本发明人针对上述问题及技术需求,提出了一种减少emi噪声的功率器件及制备方法,本发明的技术方案如下:

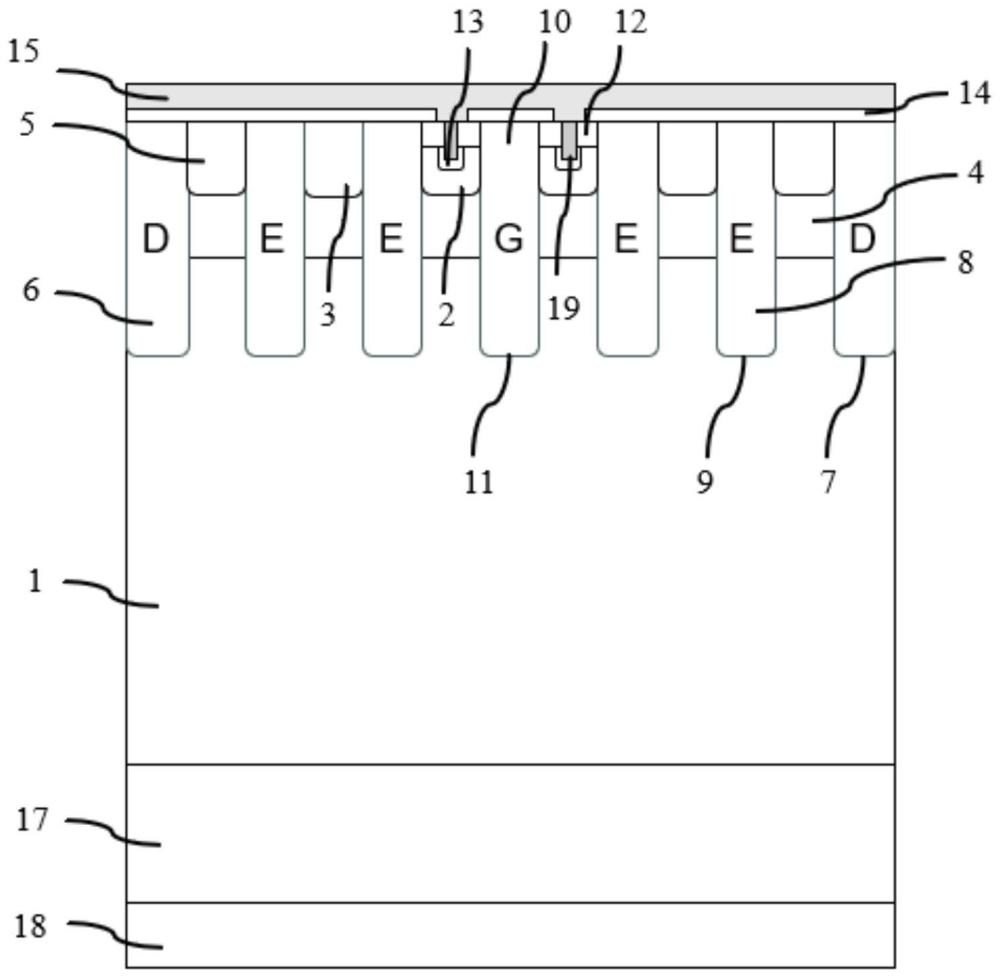

2、一种减少emi噪声的功率器件,包括具有第一导电类型的衬底以及制备于衬底有源区内的若干元胞,有源区内的元胞并联成一体,且所述元胞为沟槽型元胞;

3、在所述有源区截面上,对任一沟槽型元胞,包括有源栅单元、第一副栅单元组以及第二副栅单元组,其中,

4、所述有源栅单元位于第一副栅单元组以及第二副栅单元组之间;

5、所述第一副栅单元组至少包括一个副栅单元;

6、所述第二副栅单元组至少包括一个副栅单元;

7、所述副栅单元与衬底上方用于形成第一电极的第一电极金属电连接;

8、在有源区截面上,相邻的元胞之间至少包括一个伪栅单元;

9、所述伪栅单元、所述有源栅单元均与衬底上方用于形成第二电极的第二电极金属电连接。

10、其进一步的技术方案为,所述副栅单元包括副栅沟槽、制备于副栅沟槽内壁的副栅氧化层以及填充于副栅沟槽内的副栅多晶硅;

11、所述副栅多晶硅通过副栅氧化层与副栅沟槽内壁绝缘隔离,所述副栅多晶硅与第一电极金属欧姆接触;

12、所述有源栅单元包括有源栅沟槽、制备于有源栅沟槽内壁的有源栅氧化层以及填充于有源栅沟槽内的有源栅多晶硅;

13、所述有源栅多晶硅通过有源栅氧化层与有源栅沟槽内壁绝缘隔离,所述有源栅多晶硅与第二电极金属欧姆接触。

14、其进一步的技术方案为,还包括有源栅第二导电类型体区,其中,

15、在有源区截面上,所述有源栅第二导电类型体区设置于有源栅单元与相邻的副栅单元之间,且有源栅第二导电类型体区与有源栅单元以及对应的副栅单元接触;

16、有源栅第二导电类型体区中设置有第一导电类型源区以及第二导电类型源区,其中,

17、第一导电类型源区与有源栅单元以及对应的副栅单元接触;

18、第一导电类型源区位于第二导电类型源区上方,且第一导电类型源区与第二导电类型源区接触;

19、第一导电类型源区、第二导电类型源区均与第一电极金属欧姆接触。

20、其进一步的技术方案为,所述伪栅单元包括伪栅沟槽、制备于伪栅沟槽内壁的伪栅氧化层以及填充于伪栅沟槽内的伪栅多晶硅;

21、所述伪栅沟槽、有源栅沟槽与副栅沟槽的槽深相同;

22、所述伪栅多晶硅通过伪栅氧化层与伪栅沟槽内壁绝缘隔离,所述伪栅多晶硅与第二电极金属欧姆接触。

23、其进一步的技术方案为,所述第一副栅单元组、第二副栅单元组中副栅单元的数量相同或不同;

24、所述第一副栅单元组包括一个以上的副栅单元时,第一副栅单元组中的副栅单元沿有源栅单元指向第一副栅单元组的方向依次排列;

25、所述第二副栅单元组包括一个以上的副栅单元时,第二副栅单元组中的副栅单元沿有源栅单元指向第二副栅单元组的方向依次排列;

26、所述第一副栅单元组或第二副栅单元组仅包括一个副栅单元时,副栅单元与对应的伪栅单元之间包括伪栅第二导电类型体区;

27、伪栅第二导电类型体区与副栅沟槽侧壁以及对应的伪栅沟槽侧壁接触;

28、所述第一副栅单元组或第二副栅单元组包括一个以上的副栅单元时,伪栅单元与相邻的副栅单元之间包括伪栅第二导电类型体区;

29、伪栅第二导电类型体区与伪栅沟槽侧壁以及相邻的副栅沟槽侧壁接触。

30、其进一步的技术方案为,当第一副栅单元组和/或第二副栅单元组中包括一个以上的副栅单元时,相邻的副栅单元之间包括副栅体区单元;

31、所述副栅体区单元为副栅第二导电类型第一体区或副栅第二导电类型第二体区,其中,

32、在有源区截面上,所述副栅第二导电类型第一体区的结深小于副栅沟槽的深度,所述副栅第二导电类型第一体区与对应的副栅沟槽侧壁接触;

33、在有源区截面上,所述副栅第二导电类型第二体区的结深大于副栅沟槽的深度,所述副栅第二导电类型第二体区与对应的副栅沟槽侧壁接触,且包覆对应副栅沟槽的槽底。

34、其进一步的技术方案为,所述副栅体区单元为副栅第二导电类型第一体区时,还包括第一导电类型第一掩埋层以及第二导电类型掩埋层;

35、所述第一导电类型第一掩埋层至少设置于相邻的副栅沟槽之间,且位于副栅第二导电类型第一体区下方;

36、所述第一导电类型第一掩埋层与对应的副栅沟槽侧壁以及副栅第二导电类型第一体区接触,且副栅沟槽的槽底位于第一导电类型第一掩埋层的下方;

37、所述第二导电类型掩埋层至少位于第一导电类型第一掩埋层下方,第二导电类型掩埋层与第一导电类型第一掩埋层以及对应的副栅沟槽侧壁接触;

38、所述副栅第二导电类型第一体区与第一电极金属欧姆接触。

39、其进一步的技术方案为,所述副栅体区单元为副栅第二导电类型第二体区时,所述副栅第二导电类型第二体区中设置有第一导电类型第二掩埋层,其中,

40、所述第一导电类型第二掩埋层的结深小于副栅沟槽的深度,且第一导电类型第二掩埋层与对应的副栅沟槽侧壁接触;

41、所述第一导电类型第二掩埋层以及副栅第二导电类型第二体区均与第一电极金属欧姆接触。

42、其进一步的技术方案为,用于制备权利要求1所述的减少emi噪声的功率器件,其中,所述减少emi噪声的功率器件的制备方法包括:

43、提供第一导电类型衬底,并在与有源区对应的衬底正面进行正面元胞工艺,所述正面元胞工艺包括在与有源区对应的衬底正面制备有源栅单元、第一副栅单元组、第二副栅单元组以及若干个伪栅单元,其中,

44、所述有源栅单元位于第一副栅单元组以及第二副栅单元组之间,相邻的元胞之间至少包括一个伪栅单元;;

45、所述第一副栅单元组至少包括一个副栅单元;

46、所述第二副栅单元组至少包括一个副栅单元;

47、在衬底正面制备金属层时,所述副栅单元与衬底上方用于形成第一电极的第一电极金属电连接,所述伪栅单元、有源栅单元与衬底上方用于形成第二电极的第二电极金属电连接。

48、其进一步的技术方案为,所述正面元胞工艺包括:

49、在衬底内制备得到有源栅沟槽、若干个副栅沟槽以及若干个伪栅沟槽;

50、在上述衬底正面进行氧化层生长并淀积多晶硅,在有源栅沟槽内制备得到有源栅氧化层以及有源栅多晶硅,在副栅沟槽内制备得到副栅氧化层以及副栅多晶硅,在伪栅沟槽内制备得到伪栅氧化层以及伪栅多晶硅;

51、在有源区内进行体区制备工艺,以制备得到第二导电类型体区单元;

52、所述第二导电类型体区单元包括在有源栅沟槽与相邻的副栅沟槽之间制备有源栅第二导电类型体区,以及在伪栅沟槽与对应的副栅沟槽之间制备伪栅第二导电类型体区;

53、在上述有源栅第二导电类型体区中制备得到第一导电类型源区;

54、在上述衬底正面淀积绝缘介质层,并对绝缘介质层进行第一接触孔刻蚀;

55、通过第一接触孔在所述有源栅第二导电类型体区中制备得到第二导电类型源区;

56、在形成接触孔的绝缘介质层上制备金属层,以形成用于形成第一电极的第一电极金属,以及用于形成第二电极的第二电极金属;

57、所述副栅多晶硅、第一导电类型源区以及第二导电类型源区与第一电极金属欧姆接触,所述伪栅多晶硅、有源栅多晶硅与第二电极金属欧姆接触。

58、所述“第一导电类型”和“第二导电类型”两者中,对于n型功率器件,第一导电类型指n型,第二导电类型为p型;对于p型功率器件,第一导电类型与第二导电类型所指的类型与n型器件相反。

59、本发明的有益技术效果是:

60、本发明提供的减少emi噪声的功率器件在有源栅单元两侧设置了副栅单元,且所述副栅单元与第一电极金属欧姆连接。所述功率器件的元胞之间设置有伪栅单元,且伪栅单元与第二电极金属欧姆连接。副栅单元与有源栅单元产生电容耦合,伪栅单元与相邻的副栅单元产生电容耦合,减小了器件的输入电容及输出电容,在降低开关损耗的同时抑制第二电极的电压振荡,从而减少了器件的emi噪声。

- 还没有人留言评论。精彩留言会获得点赞!