半导体测试器件的制作方法

本技术实施例是有关于一种半导体测试器件。

背景技术:

1、三维集成电路(3dic)是半导体封装的最新发展,其中多个半导体管芯彼此堆叠(例如,使用封装上封装(pop)及系统级封装(sip)封装技术)。由于堆叠的管芯之间的互连长度减少,3dic提供了更高的集成密度及其他优势,例如更快的速度及更高的带宽。在将多个管芯(例如,集成电路系统(soic)管芯或其他类型的管芯)堆叠在一起以形成堆叠的半导体器件之后,在上执行电路探头(电路探头)或其他类型的晶片验收测试(wat)整个堆叠的半导体器件。

技术实现思路

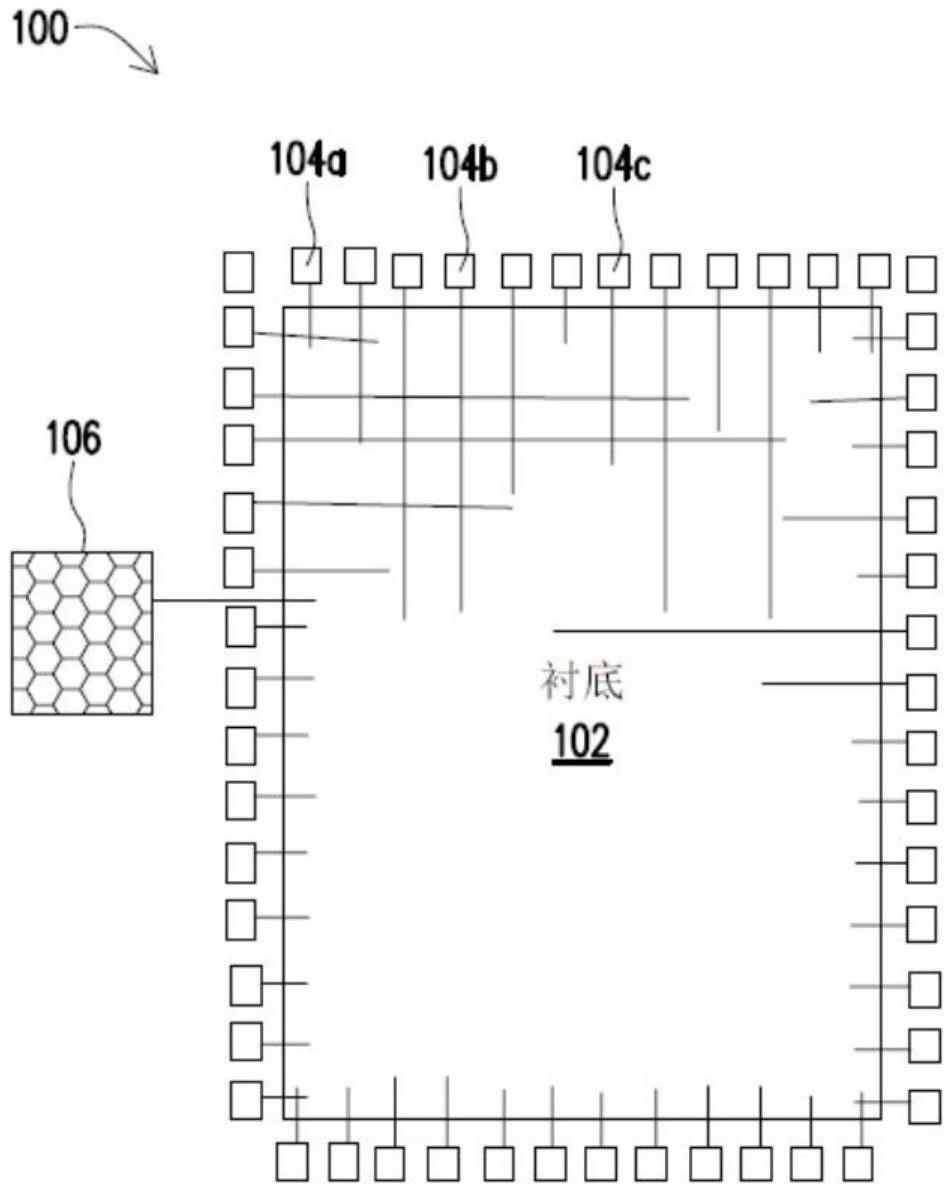

1、在本实用新型的一实施例中,一种半导体测试器件,包括:多个用于测试的器件形成在多个管芯的衬底上,其中所述多个管芯中的每个管芯与用于测试的所述多个器件中的对应一个相关联;以及多个焊盘,其中所述多个管芯中的每个管芯与所述多个焊盘中的对应一个相关联。

2、为让本实用新型实施例的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

技术特征:

1.一种半导体测试器件,其特征在于,包括:

2.根据权利要求1的所述器件,其特征在于,更包括:

3.根据权利要求1的所述器件,其特征在于,更包括:

4.根据权利要求1的所述器件,其特征在于,更包括:

5.根据权利要求4的所述器件,其特征在于,更包括:

6.根据权利要求4的所述器件,其特征在于,更包括:

7.根据权利要求1的所述器件,其特征在于,更包括:

8.根据权利要求7所述的器件,其特征在于,所述初始测试模块形成在不包括所述多个管芯的所述衬底的一部分上。

9.根据权利要求1所述的器件,其特征在于,用于测试的所述多个器件为串联,以形成闭回路。

10.根据权利要求1的所述器件,其特征在于,更包括:

技术总结

本技术实施例提供一种半导体测试器件,其包括用于测试的多个器件使用一个或多个重分布层串联,并用于对多个管芯进行半导体器件测试。如此,半导体器件测试可以支持数以千计或更多的每晶片总管芯数(例如,10,000个管芯或更多大)。此外,重分布层可以在使用后移除。在一些实施方式中,与管芯对应的用于测试的器件可以依序执行半导体器件测试。因此,可以生成测试数据并且可以包括比特序列,其中比特序列中的第一比特表示测试的总体结果,并且比特序列中的一个或多个后续比特表示每个半导体管芯或半导体器件测试的每条线的相应结果。

技术研发人员:郑光茗,高荣辉,黄健峻,杨富雄

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:20230103

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!