功率半导体器件及开关电源的制作方法

本技术涉及半导体制造,特别涉及一种功率半导体器件及开关电源。

背景技术:

1、碳化硅(sic)材料具有优良的物理和电学特性,以其宽禁带、高的热导率、高饱和漂移速度和高临界击穿电场等独特优点,成为制作高功率、高频、高压、耐高温、抗辐射器件的理想半导体材料。碳化硅mosfet器件则具有开关速度快、导通电阻小等优势,且在较小的漂移层厚度可以实现较高的击穿电压水平,减小功率开关模块的体积,降低能耗,在功率开关、转换器等应用领域中优势明显。

2、图1示出现有技术中的高压开关电源的电路结构示意图。如图1所示,该高压开关电源100包括稳压电路101、驱动控制电路102以及高压功率器件103,参考地一般为零电位。当高压开关电源100开始工作时,高压电源通过稳压电路101向驱动控制电路102提供工作电压和电流。高压功率器件103的第一端hv与高压电源连接,第二端lv与参考地连接,控制端dr接收驱动信号。当驱动控制电路102开始工作时,控制高压功率器件103导通从而进行功率转换。高压功率器件103为mos器件或igbt器件,其中,mos器件的第一端为漏极,第二端为源极,控制端为栅极;igbt器件的第一端为集电极,第二端为发射极,控制端为基极。当然,高压功率器件103还可以是其他类型的器件,不一一举例。

3、稳压电路101通过高压电阻对高压电源进行降压,从而为驱动控制电路102提供工作电压和电流。高压电阻的一端与高压电源连接,另一端与驱动控制电路102连接。由于高压电阻上的电流一直存在,无法同时兼顾启动时间和功耗,尤其当高压电源的电压很高时,高压电阻上的功耗也会进一步增大。

4、现有技术中的开关电源将低压控制电路、高压mos器件以及稳压电路集成在同一硅衬底上,采用高压bcd工艺实现,可以同时兼顾启动时间和功耗的问题。

5、但是开关电源采用高压bcd工艺使得整个系统芯片的工艺复杂,成本昂贵,而且由于硅材料本身高温特性的限制,使得高压bcd工艺中mos器件的功耗无法增加,无法拓展到大功率的应用;同时在碳化硅材料上无法实现bcd工艺,不利于该技术的应用和推广。

技术实现思路

1、鉴于上述问题,本实用新型的目的在于提供一种功率半导体器件及开关电源,采用不同沟道类型的晶体管集成在同一芯片上,工艺简单,降低芯片的复杂程度和成本。

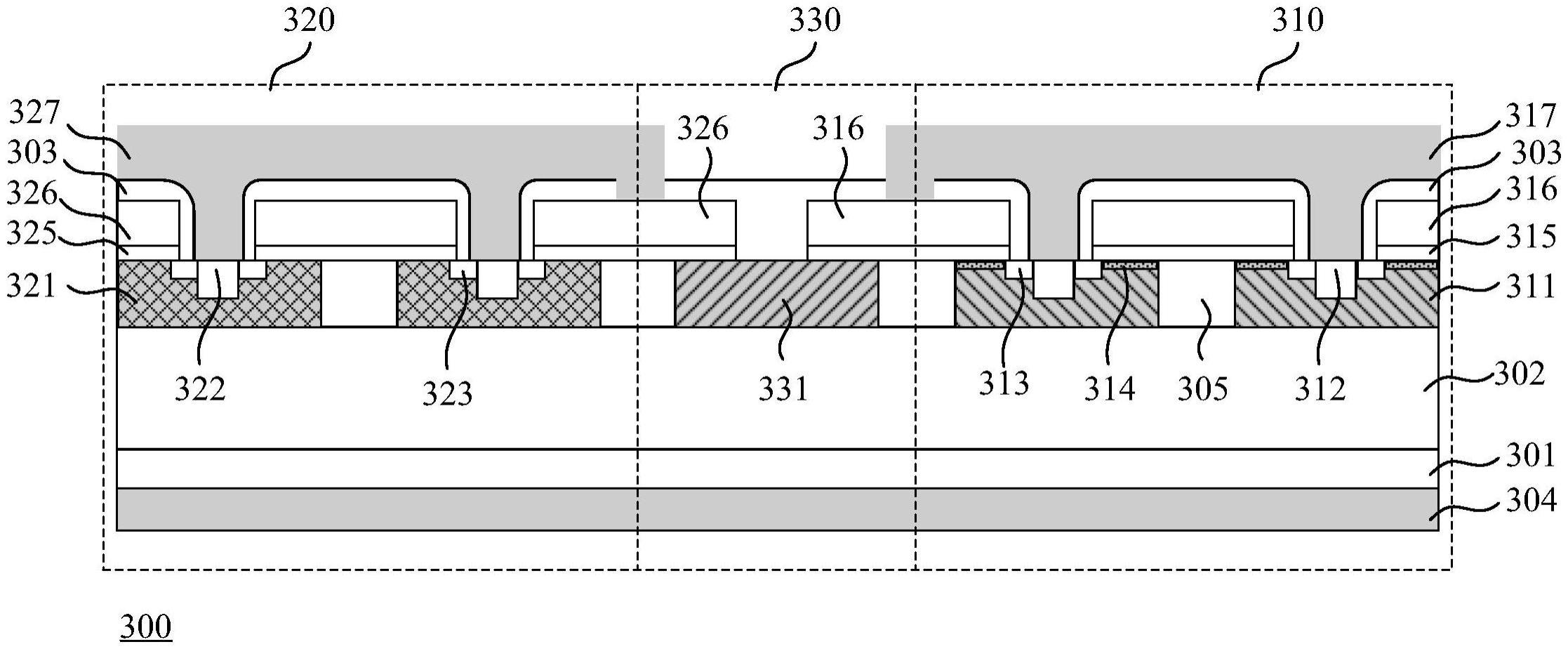

2、根据本实用新型的第一方面,提供一种功率半导体器件,包括:碳化硅衬底,具有第一掺杂类型;位于所述碳化硅衬底上的外延层,具有第一掺杂类型;积累型沟道结构和反型沟道结构,所述积累型沟道结构和所述反型沟道结构间隔设置,部分所述积累型沟道结构和所述反型沟道结构位于所述外延层中,以及部分所述积累型沟道结构和所述反型沟道结构位于所述外延层上;隔离结构,将积累型沟道结构和反型沟道结构之间彼此隔离开。

3、优选地,所述积累型沟道结构包括至少一个积累型元胞结构,每个积累型元胞结构包括:第一阱区,位于所述外延层中,具有第二掺杂类型;积累沟道层,位于所述第一阱区的表面,具有第一掺杂类型;第一欧姆接触区,位于所述第一阱区中,且从所述第一阱区的表面向所述第一阱区的内部延伸,具有第二掺杂类型;第一源区,位于所述第一阱区的表面且与所述第一阱区的外边缘具有一定距离,具有第一掺杂类型,所述第一源区与所述第一欧姆接触区接触;第一栅极结构,位于所述外延层上,且覆盖所述积累沟道层和部分第一源区。

4、优选地,所述反型沟道结构包括至少一个反型元胞结构,每个反型元胞结构包括:第二阱区,位于所述外延层中,具有第二掺杂类型;第二欧姆接触区,位于所述第二阱区中,且从所述第二阱区的表面向所述第二阱区的内部延伸,具有第二掺杂类型;第二源区,位于所述第二阱区的表面且与所述第二阱区的外边缘具有一定距离,具有第一掺杂类型,所述第二源区与所述第二欧姆接触区接触;第二栅极结构,位于所述外延层上,且覆盖部分所述第二阱区和部分所述第二源区。

5、优选地,所述第一栅极结构包括第一栅氧化层和第一栅极多晶,所述第一栅氧化层位于部分所述外延层、所述积累沟道层和部分所述第一源区上,所述第一栅极多晶位于所述第一栅氧化层上;所述第二栅极结构包括第二栅氧化层和第二栅极多晶,所述第二栅氧化层位于部分所述外延层、部分所述第二阱区和部分所述第二源区上,所述第二栅极多晶位于所述第二栅氧化层上。

6、优选地,所述功率半导体器件还包括:介质层,位于所述外延层上,覆盖所述第一栅极多晶的表面、所述第一栅氧化层和所述第一栅极多晶的侧壁、所述第二栅极多晶的表面以及所述第二栅氧化层和所述第二栅极多晶的侧壁;第一源极,位于所述介质层上,且与所述第一欧姆接触区和所述第一源区连接;第二源极,位于所述介质层上,且与所述第二欧姆接触区和所述第二源区连接;漏极,位于所述碳化硅衬底远离所述外延层的表面上;其中,所述积累型沟道结构和所述反型沟道结构的漏极共用。

7、优选地,所述隔离结构包括:第三阱区,位于所述外延层中;第三栅极结构,位于所述外延层上,覆盖部分所述第三阱区以及相邻的所述积累沟道层和部分第一源区;第四栅极结构,位于所述外延层上,覆盖部分所述第三阱区以及相邻的部分第二阱区和部分第二源区;其中,所述第三阱区位于所述第三栅极结构和所述第四栅极结构之间,且所述第三阱区浮空;所述第三栅极结构与所述第一源极连接;所述第四栅极结构与所述第二源极连接;所述第一阱区、所述第二阱区以及所述第三阱区在所述外延层中的结深相同。

8、优选地,所述隔离结构包括:第一掺杂区,位于所述外延层中;第三栅极结构,位于所述外延层上,覆盖部分所述第一掺杂区以及相邻的所述积累沟道层和部分第一源区;第四栅极结构,位于所述外延层上,覆盖部分所述第一掺杂区以及相邻的部分第二阱区和部分第二源区;其中,所述第一掺杂区位于所述第三栅极结构和所述第四栅极结构之间,且所述第一掺杂区浮空;所述第三栅极结构与所述第一源极连接;所述第四栅极结构与所述第二源极连接;所述第一掺杂区在所述外延层中的结深与所述第一阱区和所述第二阱区在所述外延层中的结深不同。

9、优选地,所述隔离结构包括:第二掺杂区,位于所述外延层中;位于所述外延层上的第一场氧化层和第二场氧化层,所述第一场氧化层覆盖部分所述第二掺杂区以及相邻的积累型沟道结构的积累沟道层和部分第一源区,所述第二场氧化层覆盖部分所述第二掺杂区以及相邻的反型沟道结构的部分第二阱区和部分第二源区;其中,所述第二掺杂区位于第一场氧化层和第二场氧化层之间,且所述第二掺杂区浮空;所述第二掺杂区在所述外延层中的结深与所述第一阱区和所述第二阱区在所述外延层中的结深相同或不同。

10、优选地,所述隔离结构包括:第三掺杂区,位于所述外延层中;第三栅极结构,位于所述外延层上,覆盖部分所述第三掺杂区以及相邻的所述积累沟道层和部分第一源区;第四栅极结构,位于所述外延层上,覆盖部分所述第三掺杂区以及相邻的部分第二阱区和部分第二源区;其中,所述第三掺杂区位于所述第三栅极结构和所述第四栅极结构之间,且所述第三掺杂区浮空;所述第三栅极结构与所述第一源极连接;所述第四栅极结构与所述第二栅极结构连接;其中,所述第三掺杂区在所述外延层中的结深与所述第一阱区和所述第二阱区在所述外延层中的结深相同或不同。

11、优选地,所述积累型沟道结构包括至少一个积累型元胞结构,每个积累型元胞结构包括:第一沟槽,位于所述外延层中,从所述外延层的表面延伸至外延层中;第一栅极结构,位于所述第一沟槽内;第一阱区,位于所述外延层中,位于所述第一沟槽的两侧,具有第二掺杂类型;第一源区,位于所述第一阱区中且从所述第一阱区的表面向所述第一阱区的内部延伸,具有第一掺杂类型;第一欧姆接触区,位于相邻第一沟槽之间的第一阱区表面且与相邻的第一沟槽具有一定距离,具有第二掺杂类型,所述第一欧姆接触区与所述第一源区接触;积累沟道层,位于所述第一源区下方的所述第一阱区中,且位于所述第一沟槽的两侧,具有第一掺杂类型。

12、优选地,所述反型沟道结构包括至少一个反型元胞结构,每个反型元胞结构包括:第二沟槽,位于所述外延层中,从所述外延层的表面延伸至外延层中;第二栅极结构,位于所述第二沟槽内;第二阱区,位于所述外延层中,位于所述第二沟槽的两侧,具有第二掺杂类型;第二源区,位于所述第二阱区中且从所述第二阱区的表面向所述第二阱区的内部延伸,具有第一掺杂类型;第二欧姆接触区,位于相邻第二沟槽之间的第二阱区表面且与相邻的第二沟槽具有一定距离,具有第二掺杂类型,所述第二欧姆接触区与所述第二源区接触。

13、优选地,所述第一栅极结构包括第一栅氧化层和第一栅极多晶,所述第一栅氧化层覆盖所述第一沟槽的内壁,所述第一栅极多晶位于所述第一栅氧化层上;所述第二栅极结构包括第二栅氧化层和第二栅极多晶,所述第二栅氧化层覆盖所述第二沟槽的内壁,所述第二栅极多晶位于所述第二栅氧化层上。

14、优选地,所述功率半导体器件还包括:介质层,位于所述外延层上,覆盖部分第一源区、第一栅极结构以及部分第二源区和第二栅极结构;第一源极,位于所述介质层上并与所述第一欧姆接触区和所述第一源区连接;第二源极,位于所述介质层上并与所述第二欧姆接触区和所述第二源区连接;漏极,位于所述碳化硅衬底远离所述外延层的表面上;其中,所述积累型沟道结构和所述反型沟道结构的漏极共用。

15、优选地,所述隔离结构包括:第四掺杂区,位于所述外延层中;第三栅极结构,位于所述外延层中的第一沟槽内,与所述第四掺杂区以及相邻的第一源区和积累沟道层接触;第四栅极结构,位于所述外延层中的第二沟槽内,与所述第四掺杂区以及相邻的第二阱区和第二源区接触;其中,所述第四掺杂区位于第三栅极结构和第四栅极结构之间,且所述第四掺杂区浮空;所述第三栅极结构与第一源极连接;所述第四栅极结构与第二源极连接;其中,所述第四掺杂区在外延层中的结深与所述第一阱区和第二阱区在外延层中的结深相同或不同。

16、优选地,所述积累型沟道结构的电参数的阈值比反型沟道结构的电参数的阈值低。

17、优选地,所述功率半导体器件还包括:高压环,位于所述功率半导体器件的边缘,围绕所述积累型沟道结构、所述反型沟道结构和所述隔离结构,具有第二掺杂类型。

18、优选地,所述功率半导体器件为mos器件或igbt器件。

19、优选地,所述功率半导体器件包括至少一个积累型沟道结构、至少一个反型沟道结构以及至少一个隔离结构。

20、根据本实用新型的另一方面,提供一种开关电源,包括:稳压电路,用于将高压电源转换成工作电压;驱动控制电路,与所述稳压电路连接,用于根据工作电压产生驱动信号和控制信号;高压功率器件,与所述驱动控制电路连接,用于根据所述驱动信号导通与关断;其中,所述高压功率器件包括第一晶体管,所述高压功率器件的结构为反型沟道结构,所述稳压电路包括第二晶体管,所述稳压电路的结构为积累型沟道结构,所述稳压电路和所述高压功率器件集成在同一衬底上以形成功率半导体器件,所述功率半导体器件的结构如上述所述。

21、优选地,所述第一晶体管的第一端与高压电源连接,第一晶体管的第二端与参考地连接,第一晶体管的控制端与驱动控制电路的驱动端连接以接收所述驱动信号;第二晶体管的第一端与高压电源连接,第二晶体管的第二端与驱动控制电路的电源端连接,向所述驱动控制电路提供工作电压,第二晶体管的控制端与驱动控制电路的控制端连接;所述开关电源刚启动时,驱动控制电路的控制端和电源端均为零电位,第二晶体管导通,向驱动控制电路提供工作电压以使驱动控制电路工作,驱动控制电路输出的驱动信号控制第一晶体管导通;开关电源的启动阶段完成后,驱动控制电路通过其控制端将第二晶体管的控制端置为零电位以关断第二晶体管,当驱动控制电路的电源端电位下降至一定电平后,驱动控制电路的驱动端输出的驱动信号控制第一晶体管关断。

22、本实用新型实施例提供的功率半导体器件及开关电源,采用不同沟道类型的晶体管集成在同一芯片上,工艺简单,降低芯片的复杂程度和成本。

23、进一步地,功率半导体器件包括积累型沟道结构的晶体管和反型沟道结构的晶体管,积累型沟道结构和反型沟道结构可以施加不同的控制电压,分别控制不同结构的导通和关断。

24、进一步地,反型沟道结构和积累型沟道结构基本相同,且共用同一衬底和外延层,只是反型沟道结构和积累型沟道结构的阱区形成步骤上有差异,其余的工艺步骤完全相同,从而降低了芯片的加工复杂程度和成本。

25、进一步地,第一阱区、积累沟道层以及第二阱区之间的掺杂浓度不同,可以调节积累沟道层的浓度,使得积累型沟道结构的阈值低。

26、进一步地,隔离结构包括第三栅极结构、第四栅极结构和位于第三栅极结构和第四栅极结构之间浮空的第三阱区,且第三栅极结构覆盖相邻的积累沟道层且与第一源极连接,第四栅极结构覆盖相邻的第二阱区且与第二源极连接,可以提高积累型沟道结构和反型沟道结构之间的隔离耐压。

27、进一步地,隔离结构包括第三栅极结构、第四栅极结构和位于第三栅极结构和第四栅极结构之间浮空的掺杂区,掺杂区单独形成,可以调节第一掺杂区在外延层中的结深来调节隔离耐压的大小。

28、进一步地,积累型沟道结构和反型沟道结构可以集成在同一个高压环内,由于高压器件高压环的面积很大,采用本专利中的结构减少了至少一个高压环的面积,缩小了芯片面积。

- 还没有人留言评论。精彩留言会获得点赞!