半导体封装装置的制作方法

本申请涉及半导体封装,具体涉及一种半导体封装装置。

背景技术:

1、某些半导体封装,例如focos(fan-out chip on substrate,扇出型基板上芯片封装)结构,包括模封材和埋设在模封材内的芯片,并会在芯片的晶背(背面)一侧的模封材(molding compound)表面长重布线层(redistribution layer,rdl)。

2、对于这些半导体封装来说,制程中精准对位非常重要。一种常用的对位方法是在芯片的晶背设置定位标记(alignment mark),但在rdl制程中定位标记经过多层介电层(pi)堆叠后会逐渐模糊,影响到对位的准确性。另外一种对位方法是设置铜柱(cupillar),铜柱埋在模封材内成为tmv(through molding via,塑封通孔),在磨掉模封材表面后露出铜柱作为定位标记来对位,但是露出的铜柱经过氧化后与围绕在旁边的模封材表面相比较的色差有变化,对位时会有所偏差甚至被有可能误判为填料颗粒(particle)而跳过(skip),导致无法对位。

3、由上可知目前常用的对位标记存在对位准确性不高,对位系统判读对位标标记的能力受限制的技术问题。

技术实现思路

1、本申请提出了一种半导体封装装置,用于解决目前常用的对位标记存在对位准确性不高,对位系统判读对位标记能力受限制的技术问题。

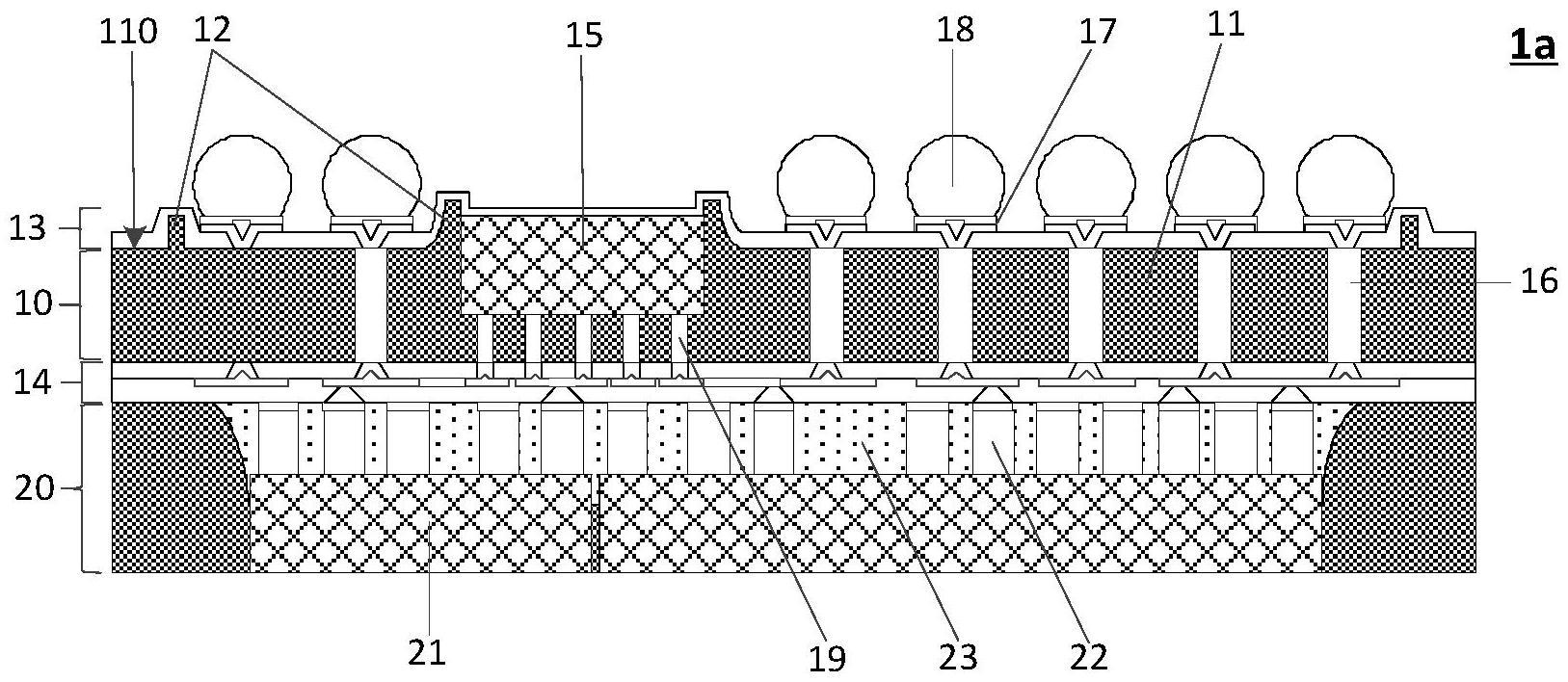

2、为实现上述目的,本申请采用如下技术方案:一种半导体封装装置,包括模封结构,所述模封结构包括:主体结构,具有第一表面;对位部,形成于所述第一表面,所述对位部的顶面与所述第一表面位于不同平面上。

3、在一些可选的实施方式中,所述对位部凸出于所述第一表面。

4、在一些可选的实施方式中,所述对位部内凹于所述第一表面。

5、在一些可选的实施方式中,所述的半导体封装装置还包括设置于所述第一表面的第一重布线层,所述第一重布线层覆盖所述对位部,具有包覆在所述对位部上、与所述对位部形状相对应的部分。

6、在一些可选的实施方式中,所述的半导体封装装置还包括相对于所述第一重布线层,设置在所述模封结构另一侧的第二重布线层,所述第二重布线层的线路密度与所述第一重布线层的线路密度不同。

7、在一些可选的实施方式中,所述第一重布线层与所述第二重布线层相比,所述第一重布线层为低密度线路,所述第二重布线层为高密度线路。

8、在一些可选的实施方式中,所述的半导体封装装置还包括设置在所述第一重布线层上的焊料球,所述对位部低于所述焊料球。

9、在一些可选的实施方式中,所述的半导体封装装置还包括内埋于所述模封结构内的芯片,所述芯片的晶背朝向所述第一表面,且所述晶背与所述对位部的顶面位于不同平面上。

10、在一些可选的实施方式中,所述晶背凸出于所述第一表面。

11、在一些可选的实施方式中,所述对位部凸出于所述第一表面,所述晶背在垂直方向上介于所述对位部的顶面与所述第一表面之间。

12、为了解决目前常用的对位标记存在对位准确性不高,对位系统判读对位标记能力受限制的技术问题,本申请提出了一种半导体封装装置。本申请在模封结构表面形成对位部,对位部的顶面与模封结构的表面位于不同平面,是一种明显的立体结构,该对位部作为对位标记时,后续制程中模封结构上的重布线层会形成与对位部相对应的立体结构部分,持续提供对位标记功能,不会因层叠介电层而逐渐模糊不清,另外,该对位部与模封结构是一体成型,材质一致,不会有氧化的问题,不会因色差被误判,以此,该对位部可以实现较好的对位效果,提高对位准确性,确保对位系统判读对位标记的能力不受限制。

技术特征:

1.一种半导体封装装置,其特征在于,包括模封结构,所述模封结构包括:

2.根据权利要求1所述的半导体封装装置,其特征在于,所述对位部凸出于所述第一表面。

3.根据权利要求1所述的半导体封装装置,其特征在于,所述对位部内凹于所述第一表面。

4.根据权利要求1所述的半导体封装装置,其特征在于,还包括设置于所述第一表面的第一重布线层,所述第一重布线层覆盖所述对位部,具有包覆在所述对位部上、与所述对位部形状相对应的部分。

5.根据权利要求4所述的半导体封装装置,其特征在于,还包括相对于所述第一重布线层,设置在所述模封结构另一侧的第二重布线层,所述第二重布线层的线路密度与所述第一重布线层的线路密度不同。

6.根据权利要求5所述的半导体封装装置,其特征在于,所述第一重布线层与所述第二重布线层相比,所述第一重布线层为低密度线路,所述第二重布线层为高密度线路。

7.根据权利要求4所述的半导体封装装置,其特征在于,还包括设置在所述第一重布线层上的焊料球,所述对位部低于所述焊料球。

8.根据权利要求1所述的半导体封装装置,其特征在于,还包括内埋于所述模封结构内的芯片,所述芯片的晶背朝向所述第一表面,且所述晶背与所述对位部的顶面位于不同平面上。

9.根据权利要求8所述的半导体封装装置,其特征在于,所述晶背凸出于所述第一表面。

10.根据权利要求9所述的半导体封装装置,其特征在于,所述对位部凸出于所述第一表面,所述晶背在垂直方向上介于所述对位部的顶面与所述第一表面之间。

技术总结

本申请提出了一种半导体封装装置,包括模封结构,所述模封结构包括:主体结构,具有第一表面;对位部,形成于所述第一表面,所述对位部的顶面与所述第一表面位于不同平面上。本申请在模封结构表面形成的对位部是一种明显的立体结构,该对位部作为对位标记时,后续制程中模封结构上的重布线层会形成与对位部相对应的立体结构部分,持续提供对位标记功能,不会因层叠介电层而逐渐模糊不清,另外,该对位部与模封结构是一体成型,材质一致,不会有氧化的问题,不会因色差被误判,以此,该对位部可以实现较好的对位效果,提高对位准确性,确保对位系统判读对位标记的能力不受限制。

技术研发人员:林裕凯,宋嘉濠

受保护的技术使用者:日月光半导体制造股份有限公司

技术研发日:20230116

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!