一种量子芯片及封装结构的制作方法

本申请属于量子芯片封装,特别是涉及一种量子芯片及封装结构。

背景技术:

1、随着量子计算的日益发展,量子比特数量越来越多,而量子芯片的尺寸有限,要满足比特数量的需求,量子芯片就需要增大尺寸或增加数量,依此来增加量子比特电路。然而,如果量子芯片尺寸增大,量子芯片与封装盒之间需要更多的键合线键合,键合难度也就增大,如果量子芯片数量增加,由于每个量子芯片需要一个封装盒,封装盒的数量也就相应增加,封装成本也就增加。

技术实现思路

1、本申请的目的是提供一种量子芯片及封装结构,以解决现有技术中,量子比特数量增加,导致量子芯片尺寸增大或者数量增多的问题。

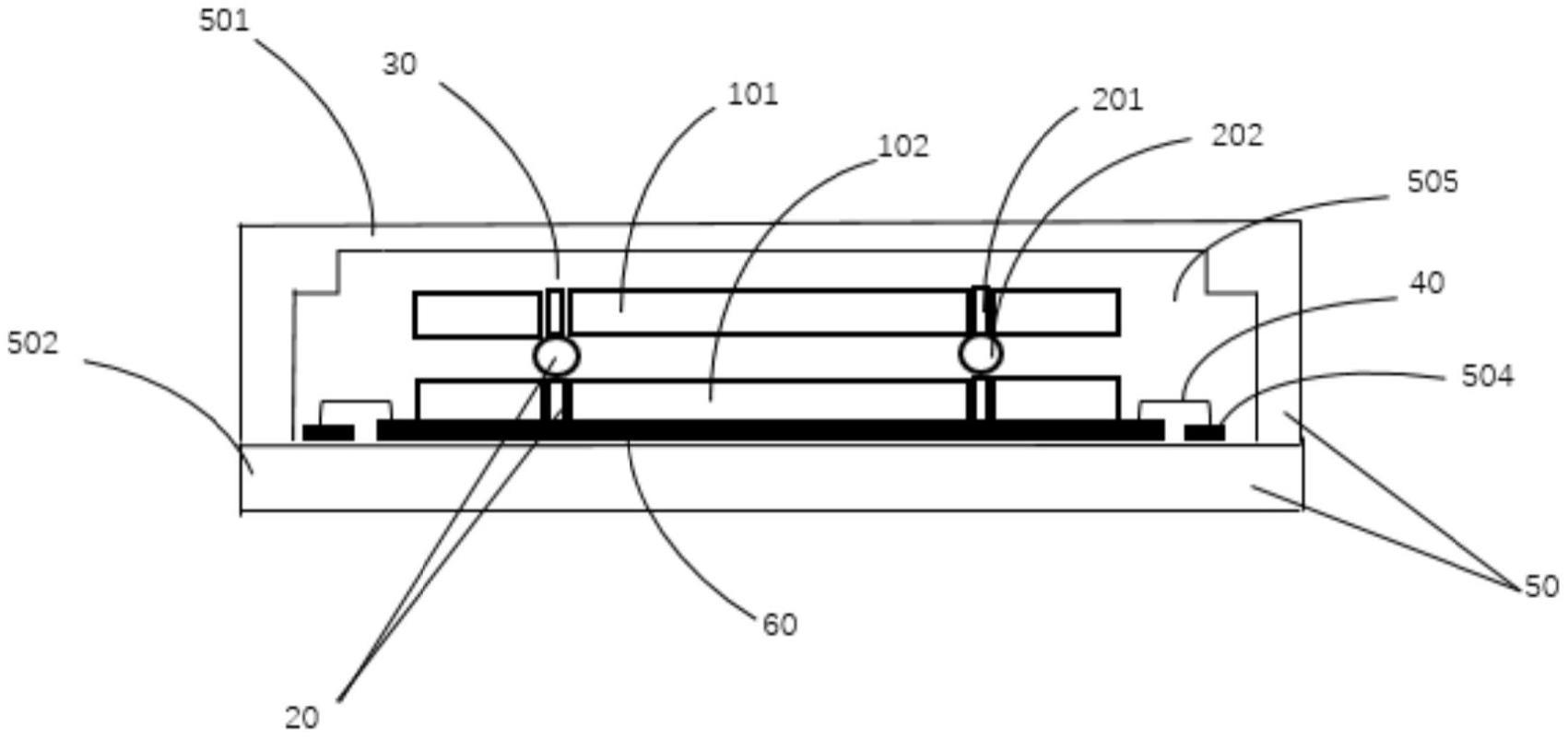

2、为解决上述技术问题,本实用新型提供一种量子芯片,包括第一芯片101、第二芯片102、互联件20,所述第一芯片101与所述第二芯片102相对设置,且所述第一芯片101、所述第二芯片102的两个表面都设有量子比特电路,所述第一芯片101、所述第二芯片102上的量子比特电路通过互联件20电性连接。

3、优选的,所述互联件20包括第一部件201和第二部件202,所述第一芯片101两个表面的量子比特电路以及所述第二芯片102两个表面的量子比特电路通过所述第一部件201电性连接,所述第一芯片101与所述第二芯片102相对的两个表面的量子比特电路通过所述第二部件202电性连接。

4、优选的,所述第二部件202位于第一芯片101与第二芯片102之间。

5、优选的,所述第二部件202为锡球或者焊点。

6、优选的,所述第一芯片101、所述第二芯片102均设有贯通两个表面的过孔30,所述第一部件201设置于所述过孔30中。

7、优选的,所述第一部件201为金属柱。

8、本申请提出一种封装结构,包括:封装盒50、引线40以及前述任一种的量子芯片,所述封装盒50形成有焊盘504和容置腔505,所述量子芯片置于所述容置腔505内,所述焊盘504邻近所述量子芯片设置,所述量子芯片最下方表面的量子比特电路与所述焊盘504通过所述引线40电性连接。

9、优选的,所述封装结构还包括导体层60,所述导体层60位于容置腔505底部,所述量子芯片置于所述导体层60上,所述量子芯片最下方表面的量子比特电路与所述导体层60电性连接,所述导体层60与所述焊盘504通过所述引线40电性连接。

10、优选的,所述导体层60包括铜层和金层,所述铜层附着于容置腔505底部,所述金层附着于所述铜层上,所述量子芯片最下方表面的量子比特电路与所述金层电性连接,所述金层与所述焊盘504通过所述引线40电性连接。

11、优选的,所述封装盒50包括基座502和盖体501,所述容置腔505和焊盘504形成在所述基座502上,所述盖体501用于封闭所述基座502。

12、与现有技术相比,本申请通过芯片叠层设计,在包含更多量子比特数量的情况下,既不增加量子芯片的尺寸,也不增加封装盒数量,从而能够降低键合难度,并且降低封装成本。

技术特征:

1.一种量子芯片,其特征在于,包括第一芯片(101)、第二芯片(102)、互联件(20),所述第一芯片(101)与所述第二芯片(102)相对设置,且所述第一芯片(101)、所述第二芯片(102)的两个表面都设有量子比特电路,所述第一芯片(101)、所述第二芯片(102)上的量子比特电路通过互联件(20)电性连接。

2.根据权利要求1所述的量子芯片,其特征在于:所述互联件(20)包括第一部件(201)和第二部件(202),所述第一芯片(101)两个表面的量子比特电路以及所述第二芯片(102)两个表面的量子比特电路通过所述第一部件(201)电性连接,所述第一芯片(101)与所述第二芯片(102)相对的两个表面的量子比特电路通过所述第二部件(202)电性连接。

3.根据权利要求2所述的量子芯片,其特征在于:所述第二部件(202)位于第一芯片(101)与第二芯片(102)之间。

4.根据权利要求3所述的量子芯片,其特征在于:所述第二部件(202)为锡球或者焊点。

5.根据权利要求2所述的量子芯片,其特征在于:所述第一芯片(101)、所述第二芯片(102)均设有贯通两个表面的过孔(30),所述第一部件(201)设置于所述过孔(30)中。

6.根据权利要求5所述的量子芯片,其特征在于:所述第一部件(201)为金属柱。

7.一种封装结构,其特征在于,包括:封装盒(50)、引线(40)以及权利要求1-6任一项所述的量子芯片,所述封装盒(50)形成有焊盘(504)和容置腔(505),所述量子芯片置于所述容置腔(505)内,所述焊盘(504)邻近所述量子芯片设置,所述量子芯片最下方表面的量子比特电路与所述焊盘(504)通过所述引线(40)电性连接。

8.根据权利要求7所述的封装结构,其特征在于:所述封装结构还包括导体层(60),所述导体层(60)位于容置腔(505)底部,所述量子芯片置于所述导体层(60)上,所述量子芯片最下方表面的量子比特电路与所述导体层(60)电性连接,所述导体层(60)与所述焊盘(504)通过所述引线(40)电性连接。

9.根据权利要求8所述的封装结构,其特征在于:所述导体层(60)包括铜层和金层,所述铜层附着于容置腔(505)底部,所述金层附着于所述铜层上,所述量子芯片最下方表面的量子比特电路与所述金层电性连接,所述金层与所述焊盘(504)通过所述引线(40)电性连接。

10.根据权利要求7所述的封装结构,其特征在于:所述封装盒(50)包括基座(502)和盖体(501),所述容置腔(505)和焊盘(504)形成在所述基座(502)上,所述盖体(501)用于封闭所述基座(502)。

技术总结

本申请公开了一种量子芯片及封装结构,属于量子芯片封装领域。量子芯片包括:第一芯片、第二芯片、互联件,第一芯片与第二芯片相对设置,且第一芯片、第二芯片上的量子比特电路通过互联件电性连接。通过芯片叠层设计,在包含更多量子比特数量的情况下,既不增加量子芯片的尺寸,也不增加封装盒数量,从而能够降低键合难度,并且降低封装成本。

技术研发人员:李舒啸

受保护的技术使用者:本源科仪(成都)科技有限公司

技术研发日:20230301

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!