半导体结构的制作方法

本技术涉及半导体,尤其涉及一种半导体结构。

背景技术:

1、异质结双极性晶体管(hetero-junction bipolar transistor,缩写为hbt)是双极性晶体管的一种,其发射层和基层采用不同的半导体材料形成异质结。异质结双极性晶体管比一般的双极性晶体管具有更好的高频信号特性和基层发射效率,可以在高达数百ghz的信号下工作,在现代的高速电路、射频系统和移动电话中应用广泛。

2、由于工艺均匀性等的限制,单个异质结双极型晶体管的尺寸较小,使得单个器件无法满足大功率的产品需求,故需要将几个异质结双极型晶体管并联起来以提供大功率。然而,大功率的器件的散热问题随之成为产品设计的难点。

3、因此,现有的异质结双极型晶体管结构有待进一步改善。

技术实现思路

1、本实用新型解决的技术问题是提供一种半导体结构,以提高半导体结构的性能。

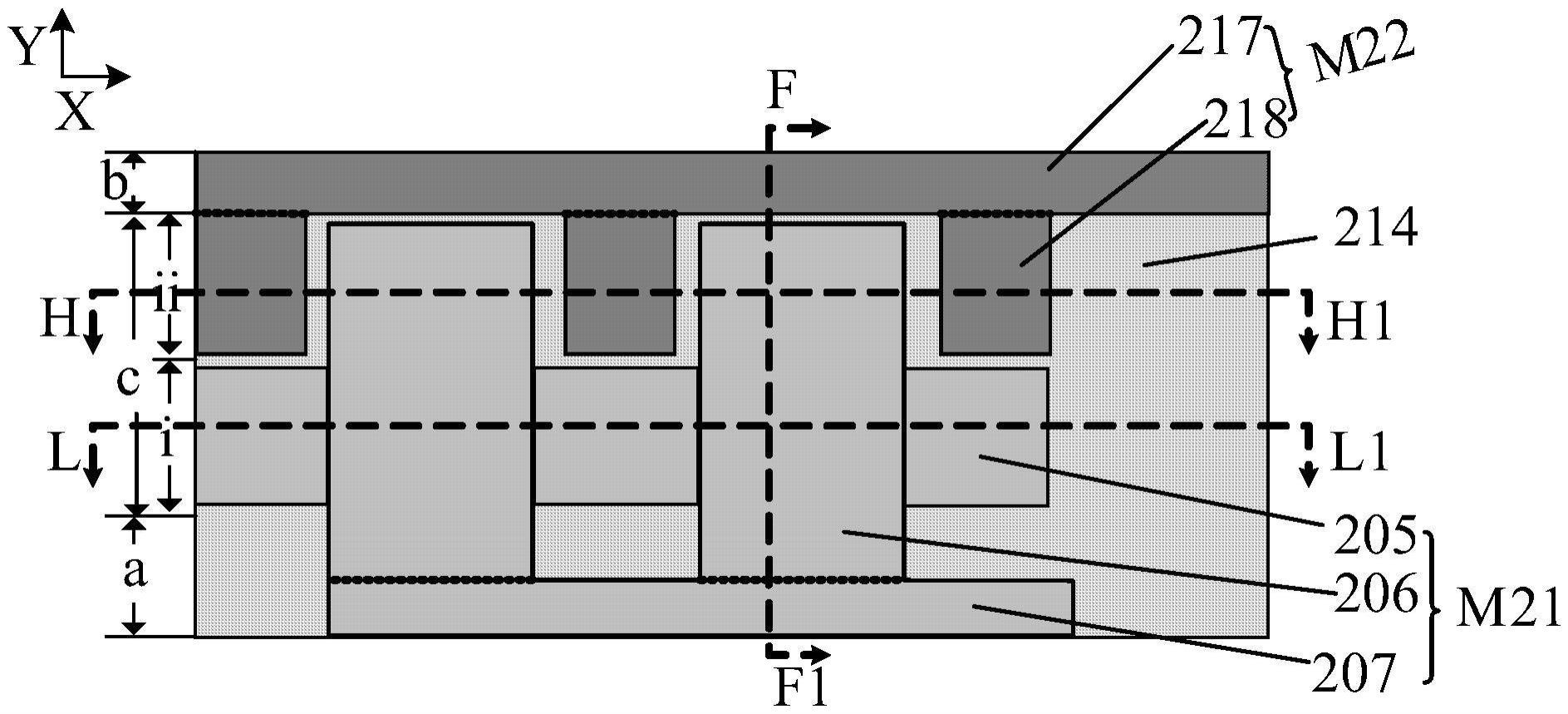

2、为解决上述技术问题,本实用新型实施例提供一种半导体结构,包括:集电基底层;位于所述集电基底层上的若干凸起结构,若干所述凸起结构沿第一方向排布,所述第一方向平行于所述集电基底层表面,各所述凸起结构包括集电层、位于所述集电层表面的基层和位于所述基层表面的发射层;位于各所述发射层的部分表面的发射极,所述发射极与所述发射层电连接;位于所述凸起结构上方的第一导电结构,所述第一导电结构包括若干导电连接层和若干第一导电层,一个所述第一导电层位于一个所述发射极表面,各所述导电连接层位于相邻的所述第一导电层之间,且与所述第一导电层电连接;位于各所述基层的部分表面的基极,所述基极还贯穿所述发射层,所述基极与所述基层电连接,所述基极与所述发射极分立放置;位于相邻的凸起结构之间的集电极,所述集电极与所述集电基底层电连接。

3、可选的,所述集电基底层包括沿第二方向排布的第一引出区、器件区及第二引出区,所述第二方向平行于所述集电基底层表面,且与所述第一方向相互垂直,所述第一引出区和所述第二引出区位于所述器件区的两侧;若干所述凸起结构和若干所述集电极均位于所述器件区上。

4、可选的,还包括:第二导电结构,所述第二导电结构包括第二总线、以及与所述第二总线电连接的若干第二导电层,所述第二总线位于所述第二引出区上,一个所述第二导电层位于一个所述集电极表面,在沿所述第二方向上,各所述第二导电层还包括第一部和第二部,所述第二部与所述第二总线相邻,且所述第二部位于所述第二总线和所述第一部之间;所述导电连接层位于所述第一部上方。

5、可选的,还包括:第三导电结构,所述第三导电结构包括第三总线、以及与所述第三总线电连接的若干第三导电层,所述第三总线位于所述第一引出区上,一个所述第三导电层位于一个所述基极表面。

6、可选的,所述基极包括相连接的第一基极部和第二基极部,所述第一基极部平行于所述第一方向放置,所述第二基极部平行于所述第二方向放置,所述第一基极部相对于所述第二基极部靠近所述第一引出区;所述第三导电层位于所述第一基极部表面。

7、可选的,还包括:介电层,所述介电层位于若干所述凸起结构表面、所述第二导电结构的部分表面和所述第三导电结构部分表面;所述介电层暴露出所述发射极表面、所述第二总线表面及所述第二部表面;所述第一导电结构位于所述介电层表面。

8、可选的,所述第一导电结构还包括第一总线,所述第一总线位于所述第一引出区上,且与若干所述第一导电层电连接。

9、可选的,还包括:第四导电结构,所述第四导电结构包括第四总线、以及与所述第四总线电连接的若干第四导电层,所述第四总线位于所述第二总线表面,所述第四导电层嵌入所述介电层,且位于所述第二部表面。

10、可选的,还包括:第五导电层,所述第五导电层位于所述介电层表面,所述第五导电层还位于所述发射极表面和所述第一导电层之间。

11、可选的,所述集电极在沿所述第二方向上具有第一尺寸,所述导电连接层在沿所述第二方向上具有第二尺寸,所述第二尺寸为所述第一尺寸的1/4至1/3。

12、与现有技术相比,本实用新型实施例的技术方案具有以下有益效果:

13、本实用新型技术方案提供的半导体结构中,所述第一导电结构包括若干导电连接层和若干第一导电层,一个所述第一导电层位于一个所述发射极上,且与所述发射极电连接,各所述导电连接层位于相邻的所述第一导电层之间,且与所述第一导电层连接,各所述导电连接层使相邻的所述第一导电层相互连接,增大了异质结双极型晶体管器件的散热面积,利于提高器件性能的可靠性。

14、进一步,在沿所述第二方向上,各所述第二导电层还包括第一部和第二部,所述第二部与所述第二总线相邻,且所述第二部位于所述第二总线和所述第一部之间;所述导电连接层位于所述第一部上方;第四导电结构,所述第四导电结构包括第四总线、以及与所述第四总线电连接的若干第四导电层,所述第四总线位于所述第二总线表面,所述第四导电层嵌入所述介电层,且位于所述第二部表面,所述第四导电结构与所述第二导电结构作为所述集电极的引出,提高了所述集电极引出金属导线的厚度,有利于提高了集电极端对输出电流的承载能力,减少因电流过大而导致金属线烧毁的概率,进而提高器件性能的稳定性;另外,通过调节所述第二部和所述第一部的尺寸,可以平衡所述第四导电结构的尺寸和所述导电连接层的尺寸,以平衡集电极端对输出电流的承载能力和器件的散热能力。

15、进一步,所述导电连接层位于所述第一部上方,所述第四导电层位于所述第二部表面,可以减少所述第四导电层和所述导电连接层之间可能的短路异常的概率。

16、进一步,第五导电层位于所述发射极上和所述第一导电层之间,第五导电层与所述发射极电连接,用于增加与所述发射极电连接的金属层厚度,以增大异质结双极型晶体管器件的散热面积,提高器件性能的可靠性。

17、进一步,所述第一导电结构还包括第一总线,所述第一总线位于所述第一引出区上,且与若干所述第一导电层电连接,所述导电连接层的存在,使得各个异质结双极型晶体管的发射极端到所述第一总线的电阻差异减小,从而利于平衡各个异质结双极型晶体管的发射极的电压,提高各个异质结双极型晶体管功率的一致性,有利于提高器件性能。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述的半导体结构,其特征在于,所述集电基底层包括沿第二方向排布的第一引出区、器件区及第二引出区,所述第二方向平行于所述集电基底层表面,且与所述第一方向相互垂直,所述第一引出区和所述第二引出区位于所述器件区的两侧;若干所述凸起结构和若干所述集电极均位于所述器件区上。

3.如权利要求2所述的半导体结构,其特征在于,还包括:第二导电结构,所述第二导电结构包括第二总线、以及与所述第二总线电连接的若干第二导电层,所述第二总线位于所述第二引出区上,一个所述第二导电层位于一个所述集电极表面;在沿所述第二方向上,各所述第二导电层还包括第一部和第二部,所述第二部与所述第二总线相邻,且所述第二部位于所述第二总线和所述第一部之间;所述导电连接层位于所述第一部上方。

4.如权利要求3所述的半导体结构,其特征在于,还包括:第三导电结构,所述第三导电结构包括第三总线、以及与所述第三总线电连接的若干第三导电层,所述第三总线位于所述第一引出区上,一个所述第三导电层位于一个所述基极表面。

5.如权利要求4所述的半导体结构,其特征在于,所述基极包括相连接的第一基极部和第二基极部,所述第一基极部平行于所述第一方向放置,所述第二基极部平行于所述第二方向放置,所述第一基极部相对于所述第二基极部靠近所述第一引出区;所述第三导电层位于所述第一基极部表面。

6.如权利要求4所述的半导体结构,其特征在于,还包括:介电层,所述介电层位于若干所述凸起结构表面、所述第二导电结构的部分表面和所述第三导电结构部分表面;所述介电层暴露出所述发射极表面、所述第二总线表面及所述第二部表面;所述第一导电结构位于所述介电层表面。

7.如权利要求6所述的半导体结构,其特征在于,所述第一导电结构还包括第一总线,所述第一总线位于所述第一引出区上,且与若干所述第一导电层电连接。

8.如权利要求6所述的半导体结构,其特征在于,还包括:第四导电结构,所述第四导电结构包括第四总线、以及与所述第四总线电连接的若干第四导电层,所述第四总线位于所述第二总线表面,所述第四导电层嵌入所述介电层,且位于所述第二部表面。

9.如权利要求6所述的半导体结构,其特征在于,还包括:第五导电层,所述第五导电层位于所述介电层表面,所述第五导电层还位于所述发射极表面和所述第一导电层之间。

10.如权利要求2所述的半导体结构,其特征在于,所述集电极在沿所述第二方向上具有第一尺寸,所述导电连接层在沿所述第二方向上具有第二尺寸,所述第二尺寸为所述第一尺寸的1/4至1/3。

技术总结

一种半导体结构,包括:集电基底层;位于集电基底层上的若干凸起结构,若干凸起结构沿第一方向排布,第一方向平行于集电基底层表面,各凸起结构包括集电层、位于集电层表面的基层和位于基层表面的发射层;位于各发射层的部分表面的发射极,发射极与发射层电连接;位于凸起结构上方的第一导电结构,第一导电结构包括若干导电连接层和若干第一导电层,一个第一导电层位于一个发射极表面,各导电连接层位于相邻的第一导电层之间,且与第一导电层连接,各导电连接层使相邻的第一导电层相互连接,增大了异质结双极型晶体管器件的散热面积,利于提高器件性能的可靠性。

技术研发人员:潘林,杨磊,袁海旭,何鹏

受保护的技术使用者:常州承芯半导体有限公司

技术研发日:20230515

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!