一种IGBT芯片的制作方法

本技术涉及一种igbt芯片。

背景技术:

1、现在的主流的igbt高频化应用芯片主要采用正面提高iegt效果的窄mesa设计,芯片背面采用高能离子注入技术形成场截止层。窄mesa设计即更精细的沟槽设计,窄mesa工艺的采用主要优化了igbt的通态特性,使得导通电压vcesat降低。高频应用的关键还是要把开关损耗降低。该结构设计的场截止(field stop)层,即fs层通常采用高能磷注入形成,载流子寿命长。在器件反向关断时,芯片内部载流子复合时间长、拖尾电流长,产生了非常大的关断损耗,不利于芯片的高频开关特性。

2、如公开号为cn115579381a公开的垂直型浮空及阻性场板终端的碳化硅igbt器件及制备方法,通过在在元胞终端区引入垂直型沟槽型金属-绝缘体-半导体mis结构,结合多区结终端扩展/多浮空场限环/半绝缘多晶硅sipos电阻场板技术,保证沟槽型碳化硅igbt器件高效率终端的前提下,保持高击穿电压及氧化层可靠性。但其fs层同样采用高能磷注入形成,使其关断过程中产生了非常大的消耗。

技术实现思路

1、为解决上述技术问题,本实用新型提供了一种igbt芯片。

2、本实用新型通过以下技术方案得以实现。

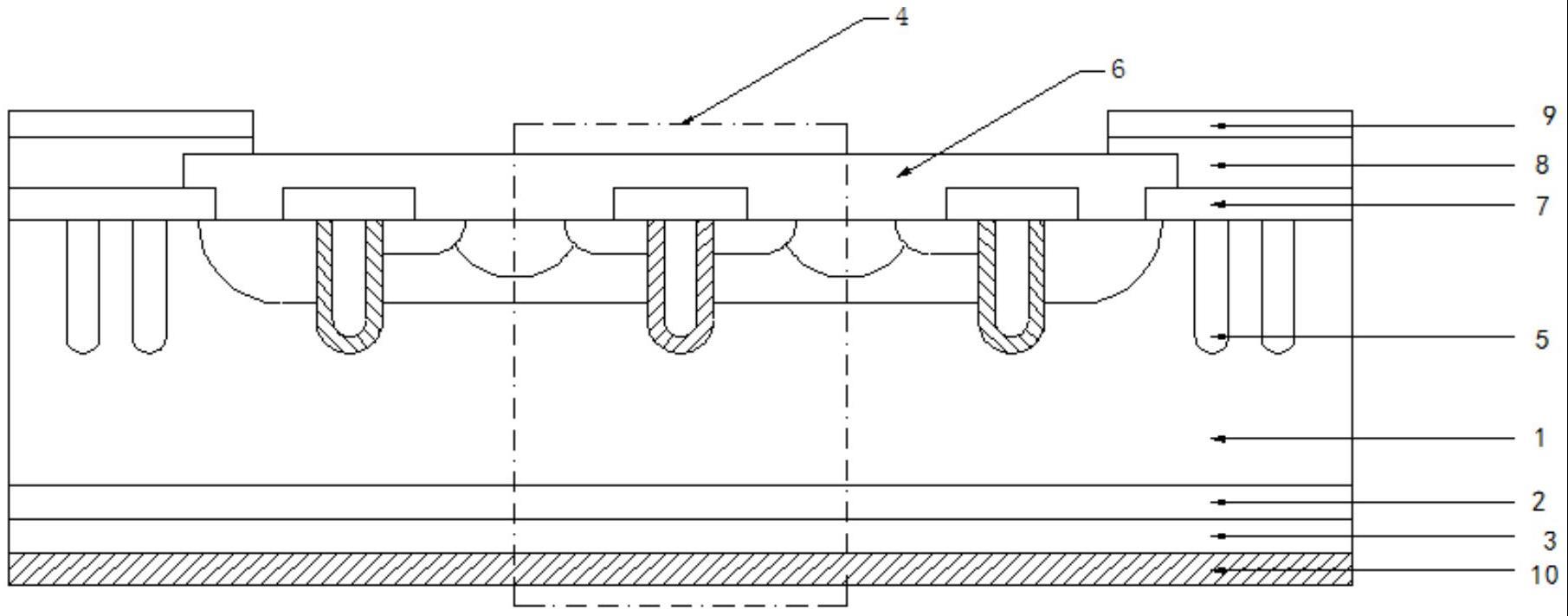

3、本实用新型提供的一种igbt芯片,包括漂移区;漂移区的正面中部加工有元胞组,元胞组的端面通过正面电极覆盖,漂移区的边缘加工有p+ring区,p+ring区的端面通过依次堆叠有场氧化层、sin钝化层、pi钝化层,所述漂移区的背面依次加工有场截止区、p+背集电区、背部电极。

4、所述元胞组包括pbase区,pbase区上加工有多个栅氧化层,栅氧化层内填充有多晶硅栅极,相邻的栅氧化层之间有p+元胞区加工在pbase区内,pbase区和p+元胞区之间通过有源n+区连接。

5、所述栅氧化层为u型槽,栅氧化层的底部伸出pbase区置于漂移区内。

6、所述栅氧化层顶部还设有内绝缘层,内绝缘层覆盖在栅氧化层上。

7、所述正面电极与场氧化层嵌入式连接。

8、所述p+背集电区内为htd。

9、所述sin钝化层和pi钝化层覆盖在正面电极的边缘。

10、一种igbt芯片的制备方法,其步骤为:

11、a、选择掺杂浓度为5e13~1e14cm-2的熔单晶硅晶圆作为漂移区;

12、b、在漂移区正面边缘制作结深为2~5μm的p+ring区;

13、c、在漂移区中部制作结深为3.5~4μm的pbase区;

14、d、在pbase区内制作深度3.5~5μm的栅氧化层,并在栅氧化层内填充多晶硅制作多晶硅栅极;

15、e、刻蚀出有源n+区窗口,进行硼离子注入后去胶形成结深为3~0.6μm有源n+区;

16、f、在相邻的有源n+区之间注入硼离子形成将相邻的pbase区连接的p+元胞区,去胶后激活;

17、g、在漂移区正面进行氧化硅和bpsg淀积,高温回流后刻蚀出电极孔;

18、h、在漂移区正面蒸铝后将电极孔内的铝层刻除,然后进行正面合金;

19、i、在漂移区正面边缘依次进行氮化硅淀积和pi淀积,然后进行pi亚胺化;

20、j、将漂移区的背面减薄,释放晶圆应力后依次进行磷注入,形成场截止区;

21、k、在漂移区背面进行高能质子h+注入,并通过激光退火形成具有htd的p+背集电区;

22、l、进行背面淀积钛镍银,形成背面金属电极背部电极。

23、所述步骤b的具体步骤为:

24、b1、在漂移区的正面生长厚度为的牺牲氧化层后;

25、b2、去氧化层并使用氢氟酸清洗25-30s;

26、b3、使用干湿干的方式生长厚度为的热氧化层,干湿干的氧化时间依次为30、120、30min,氧化温度为1100℃;

27、b4、在漂移区边缘的场氧化层上光刻出p+ring窗口后去胶;

28、b5、热生长厚度为的预氧化层;

29、b6、通过p+ring窗口在漂移区上进行硼离子注入,注入能量为120kev、角度为7°、5e13cm-2;

30、b7、进行推结,推结温度为1100℃,时间为120min。

31、所述步骤c的具体步骤为:

32、c1、在漂移区中部的场氧化层上光刻出p+有源区窗口后去胶;

33、c2、在p+有源区窗口注入硼离子,注入能量位80kev,角度为7°,剂量为5e14~8e14cm-2;

34、c3、推结,推结温度为1100℃,时间为70~90min。

35、所述步骤d的具体步骤为:

36、d1、在pbase区中部均匀刻蚀出多个深度为3.5~5μm的u型槽,完成后去胶;

37、d2、在u型槽内生长厚度为的牺牲氧化层,去氧化层并清洗;

38、d3、热生长厚度为的栅氧化层;

39、d4、在u型槽内进行多晶硅淀积;

40、d5、对多晶硅进行栅极布线并光刻,形成多晶硅栅后去胶。

41、本实用新型的有益效果在于:芯片背面的高能质子h+会形成具有电活性的杂质,结合芯片正面的低掺杂的pbase和多晶硅栅、边缘的p+ring区,在不影响芯片静态参数的情况下,能有效减少载流子寿命,降低反向关断时间,缩短拖尾电流时间,降低器件关断损耗,从而提高芯片的高频开关表现。

技术特征:

1.一种igbt芯片,包括漂移区(1),其特征在于:漂移区(1)的正面中部加工有元胞组(4),元胞组(4)的端面通过正面电极(6)覆盖,漂移区(1)的边缘加工有p+ring区(5),p+ring区(5)的端面通过依次堆叠有场氧化层(7)、sin钝化层(8)、pi钝化层(9),所述漂移区(1)的背面依次加工有场截止区(2)、p+背集电区(3)、背部电极(10)。

2.如权利要求1所述的igbt芯片,其特征在于:所述元胞组(4)包括pbase区(16),pbase区(16)上加工有多个栅氧化层(12),栅氧化层(12)内填充有多晶硅栅极(13),相邻的栅氧化层(12)之间有p+元胞区(15)加工在pbase区(16)内,pbase区(16)和p+元胞区(15)之间通过有源n+区(14)连接。

3.如权利要求2所述的igbt芯片,其特征在于:所述栅氧化层(12)为u型槽,栅氧化层(12)的底部伸出pbase区(16)置于漂移区(1)内。

4.如权利要求3所述的igbt芯片,其特征在于:所述栅氧化层(12)顶部还设有内绝缘层(11),内绝缘层(11)覆盖在栅氧化层(12)上。

5.如权利要求1所述的igbt芯片,其特征在于:所述正面电极(6)与场氧化层(7)嵌入式连接。

6.如权利要求1所述的igbt芯片,其特征在于:所述p+背集电区(3)内为htd。

技术总结

本技术提供的一种IGBT芯片,包括漂移区;漂移区的正面中部加工有元胞组,元胞组的端面通过正面电极覆盖,漂移区的边缘加工有P+ring区,P+ring区的端面通过依次堆叠有场氧化层、SIN钝化层、PI钝化层,所述漂移区的背面依次加工有场截止区、P+背集电区、背部电极。本技术芯片背面的高能质子H+会形成具有电活性的杂质,结合芯片正面的低掺杂的Pbase和多晶硅栅、边缘的P+ring区,在不影响芯片静态参数的情况下,能有效减少载流子寿命,降低反向关断时间,缩短拖尾电流时间,降低器件关断损耗,从而提高芯片的高频开关表现。

技术研发人员:江加丽,石文坤,冉龙玄,王智,莫宏康,赵冲冲

受保护的技术使用者:中国振华集团永光电子有限公司(国营第八七三厂)

技术研发日:20230529

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!