集成电路封装的制作方法

本技术涉及一种集成电路封装及其形成方法。

背景技术:

1、在现代半导体装置及系统中,组件的整合及小型化以越来越快的速度发展。位于封装的一或多个半导体晶粒上的诸多装置可通过发射电磁(electromagnetic,em)辐射而引起电性噪声及/或产生电磁干扰。射频(radio frequency,rf)装置及电感器是可产生电性噪声及em干扰的装置的实例。噪声源(例如rf装置)会在导电结构(例如金属引线(metallead))中所载送的信号中产生电性噪声。导电引线中的电性噪声可影响封装中的各种其他信号及装置。带噪声的电性信号会给半导体封装带来严重的问题。

技术实现思路

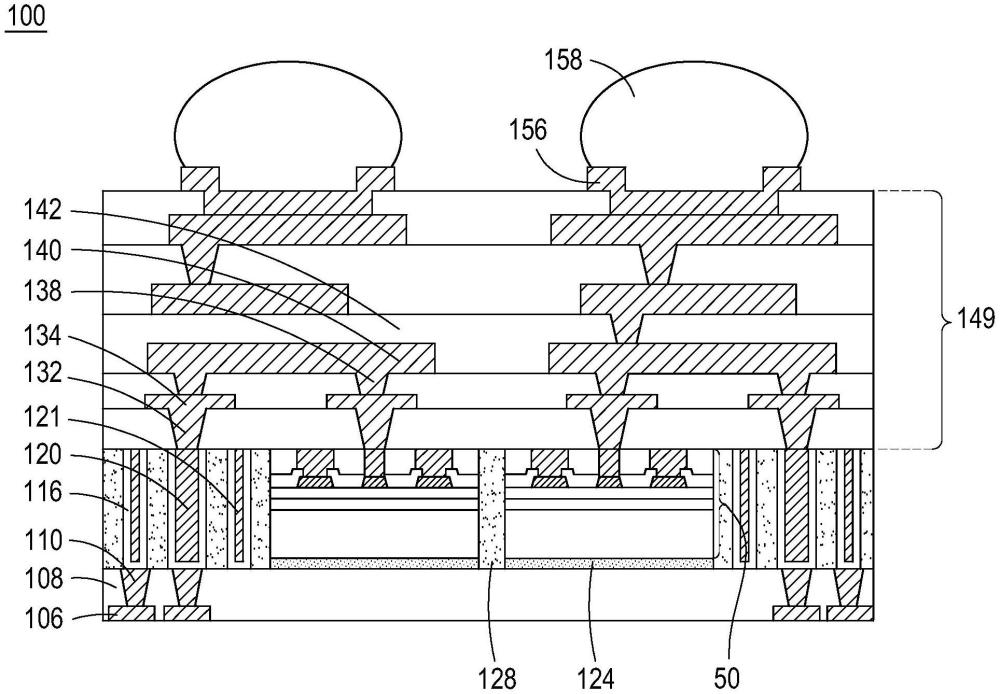

1、根据实施例,一种集成电路封装结构包括:第一重布线结构;绝缘材料,位于第一重布线结构之上;晶粒,嵌置于绝缘材料中;第二重布线结构,位于晶粒及绝缘材料之上;以及第一通孔,延伸穿过绝缘材料,其中第一通孔包括第一内导电芯及第一外导电屏蔽层,其中绝缘材料设置于第一内导电芯与第一外导电屏蔽层之间,且其中第一外导电屏蔽层在俯视图中具有环形形状。

2、根据实施例,一种集成电路封装包括:第一重布线结构;晶粒,设置于第一重布线结构之上;模制材料,环绕晶粒;第二重布线结构,位于晶粒及模制材料之上;以及第一通孔,所述第一通孔包括延伸穿过模制材料的第一部分及延伸穿过模制材料的第二部分,第一通孔的第一部分将第一重布线结构电性连接至第二重布线结构,其中第一通孔的第一部分被第一通孔的第二部分包围,且其中第二部分的外半径与内半径之间的差值介于自0.5微米至150微米的范围内。

3、根据实施例,一种形成集成电路封装的方法包括:在载体之上形成第一重布线结构;在第一重布线结构之上形成第一通孔及第二通孔,其中第一通孔及第二通孔中的每一者包括内芯及外屏蔽层,其中外屏蔽层包围内芯;将第一晶粒贴合至第一重布线结构,其中第一晶粒设置于第一通孔与第二通孔之间;以及在第一晶粒、第一通孔及第二通孔之上形成第二重布线结构。

4、本文中所揭露的一或多个实施例的有利特征可使得能够减小对内导电芯的电磁5g/6g高频干扰(electromagnetic 5g/6g high-frequency interference)。另外,集成电路封装的隔离线(isolation line)及通孔的数目可减少。另外,本文中所揭露的一或多个实施例使得封装元件之间的内连线长度较短,此进而使得时间延迟减少且集成电路封装对于先进可携式产品的适合性得到改进。另外,由于tiv的形成工艺与当前工艺相容,因此制造成本降低且效益得以提高。

技术特征:

1.一种集成电路封装,其特征在于,包括:

2.根据权利要求1所述的集成电路封装,其特征在于,所述第一外导电屏蔽层的外半径与内半径之间的差值介于自0.5微米至150微米的范围内。

3.根据权利要求1所述的集成电路封装,其特征在于,所述绝缘材料将所述第一内导电芯与所述第一外导电屏蔽层电性隔离开。

4.根据权利要求1所述的集成电路封装,其特征在于,设置于所述第一内导电芯与所述第一外导电屏蔽层之间的所述绝缘材料具有介于自0.5微米至200微米的范围内的宽度。

5.根据权利要求1所述的集成电路封装,其特征在于,还包括:

6.一种集成电路封装,其特征在于,包括:

7.根据权利要求6所述的集成电路封装,其特征在于,所述第一通孔的所述第一部分与所述第一通孔的所述第二部分通过所述模制材料而彼此电性隔离开。

8.根据权利要求7所述的集成电路封装,其特征在于,设置于所述第一通孔的所述第一部分与所述第一通孔的所述第二部分之间的所述模制材料的宽度介于自0.5微米至200微米的范围内。

9.根据权利要求6所述的集成电路封装,其特征在于,所述第二部分在俯视图中包括环形形状。

10.根据权利要求6所述的集成电路封装,其特征在于,所述第一通孔的所述第一部分的顶表面及所述第一通孔的所述第二部分的顶表面与所述晶粒的顶表面齐平。

11.根据权利要求6所述的集成电路封装,其特征在于,还包括:

技术总结

本技术提供一种集成电路封装结构,包括:第一重布线结构;绝缘材料,位于第一重布线结构之上;晶粒,嵌置于绝缘材料中;第二重布线结构,位于晶粒及绝缘材料之上;以及第一通孔,延伸穿过绝缘材料,其中第一通孔包括第一内导电芯及第一外导电屏蔽层,其中绝缘材料设置于第一内导电芯与第一外导电屏蔽层之间,且其中第一外导电屏蔽层在俯视图中具有环形形状。如此一来,可减小对内导电芯的电磁5G/6G高频干扰,且集成电路封装的隔离线及通孔的数目可减少。另外,封装元件之间的内连线可具有较短的长度,此进而使得时间延迟减少且集成电路封装对于先进可携式产品的适合性得到改进。

技术研发人员:廖文翔

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:20230616

技术公布日:2024/2/21

- 还没有人留言评论。精彩留言会获得点赞!