一种用于芯片测试的继电器扩容电路的制作方法

本技术涉及芯片测试,尤其是涉及一种继电器扩容电路。

背景技术:

1、在当前模拟半导体自动化测试中,需要采用芯片测试机(ate),并搭建测试芯片对应的测试硬件电路,再将测试机和测试硬件连接,用于测试激励的输入和输出。

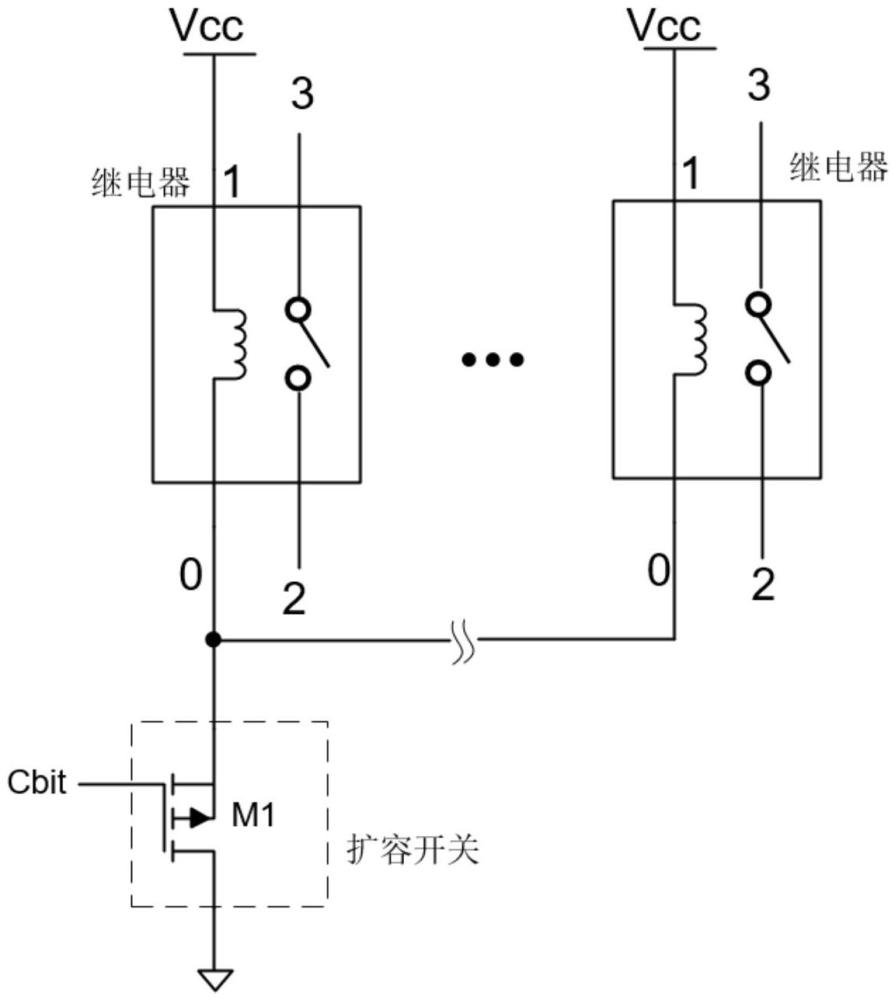

2、通常,将会用数量众多的电磁继电器来控制电路的通断或者测试激励的切换。常见的电磁继电器原理如图1所示,脚位0为控制管脚,脚位1为供电管脚,通常为+5v。当脚位0为低时,电流(通常为30ma)流过线圈产生磁场,继电器闭合,脚位2和3连通;当脚位0为高时,没有电流流过,继电器复位,脚位2和3断开。在芯片测试中,需要其他资源/设备控制电磁继电器脚位0的状态,从而使继电器切换或复位。在ate应用测试中,ate将提供继电器控制信号cbit来控制继电器脚位0,以实现控制继电器的功能。

3、如图2所示,通常继电器控制信号cbit由ate内部的继电器控制单元产生,但是继电器控制单元产生的下拉电流有一定局限性,通常仅为100ma,按照单个继电器30ma的需求,继电器控制信号cbit只能控制3个及以下的继电器,因此,在实际的应用中往往需要ate内部多个继电器控制单元产生多个继电器控制信号cbit,并送至芯片测试硬件电路以控制芯片测试硬件电路板上数量众多的电磁继电器。这样不仅浪费设备资源,在程序控制上也很复杂。

技术实现思路

1、本实用新型的目的在于提供一种用于芯片测试的继电器扩容电路,用于解决现有技术中ate在控制继电器时下拉电流不足的问题。

2、本实用新型提供了一种用于芯片测试的继电器扩容电路,包括:多个继电器,每个继电器至少包括控制端和供电端,每个继电器的供电端接收供电电压;以及扩容开关管,具有第一端、第二端和控制,其中扩容开关管的第一端耦接多个继电器的控制端,扩容开关管的第二端电连接地,扩容开关管的控制端接收芯片测试机发出的继电器控制信号,继电器控制信号具有第一逻辑状态和第二逻辑状态,当继电器控制信号具有第一逻辑状态时,继电器具有第一连接状态,当继电器控制信号具有第二逻辑状态时,继电器具有第二连接状态。

3、进一步地,耦接在扩容开关管第一端上继电器的数量由扩容开关管的第一端与第二端之间流过的最大导通电流决定。

4、进一步地,继电器还包括第一连接端和第二连接端,第一连接状态包括将继电器的第一连接端和继电器的第二连接端电连接,第二连接状态包括将继电器的第一连接端和继电器的第二连接端断开。

5、进一步地,继电器还包括第一连接端、第二连接端和第三连接端,第一连接状态包括将继电器的第一连接端和继电器的第二连接端电连接,第二连接状态包括将继电器的第一连接端和继电器的第三连接端电连接。

6、进一步地,芯片测试机内部包括控制逻辑电路和继电器控制单元,继电器控制单元包括:第一电阻;二极管,二极管的阳极通过第一电阻接收供电电压;以及第一开关管,具有第一端、第二端和控制,其中,第一开关管的第一端耦接二极管的阴极,第一开关管的第二端电连接地,第一开关管的控制端接收控制逻辑电路输出的控制信号,第一开关管的第一端提供继电器控制信号。

7、进一步地,扩容开关管的第一端与第二端之间的最大导通电流大于第一开关管的第一端与第二端之间的最大导通电流。

8、进一步地,扩容开关管包括pmos管。

9、本实用新型提供的继电器扩容电路可以灵活设置继电器控制信号可控制的继电器数量,极大减小了对芯片测试机中继电器控制单元数量的需求,连接ate和芯片的排线中也不需要更多的针位用于传输继电器控制信号,同时也简化了控制程序的设计。

技术特征:

1.一种用于芯片测试的继电器扩容电路,其特征在于,包括:

2.根据权利要求1所述的继电器扩容电路,其特征在于,耦接在所述扩容开关管第一端上继电器的数量由扩容开关管的第一端与第二端之间流过的最大导通电流决定。

3.根据权利要求1所述的继电器扩容电路,其特征在于,所述继电器还包括第一连接端和第二连接端,所述第一连接状态包括将继电器的第一连接端和继电器的第二连接端电连接,所述第二连接状态包括将继电器的第一连接端和继电器的第二连接端断开。

4.根据权利要求1所述的继电器扩容电路,其特征在于,所述继电器还包括第一连接端、第二连接端和第三连接端,所述第一连接状态包括将继电器的第一连接端和继电器的第二连接端电连接,所述第二连接状态包括将继电器的第一连接端和继电器的第三连接端电连接。

5.根据权利要求1所述的继电器扩容电路,其特征在于,所述芯片测试机内部包括控制逻辑电路和继电器控制单元,所述继电器控制单元包括:

6.根据权利要求1所述的继电器扩容电路,其特征在于,所述扩容开关管的第一端与第二端之间的最大导通电流大于第一开关管的第一端与第二端之间的最大导通电流。

7.根据权利要求1所述的继电器扩容电路,其特征在于,所述扩容开关管包括pmos管。

技术总结

本技术提供了一种用于芯片测试的继电器扩容电路。该继电器扩容电路包括多个继电器和扩容开关。扩容开关管的第一端耦接多个继电器的控制端,扩容开关管的第二端电连接地,扩容开关管的控制端接收芯片测试机发出的继电器控制信号。继电器控制信号具有第一逻辑状态和第二逻辑状态,当继电器控制信号具有第一逻辑状态时,继电器具有第一连接状态,当继电器控制信号具有第二逻辑状态时,继电器具有第二连接状态。该继电器扩容电路不受芯片测试机发出继电器控制信号的端口上的电流限制,可灵活设置继电器扩容电路中继电器的数量,节约设备资源,程序控制简单。

技术研发人员:唐锐

受保护的技术使用者:晶艺半导体有限公司

技术研发日:20230630

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!