接合结构以及半导体结构的制作方法

本申请涉及半导体,更具体地,涉及一种接合结构以及一种半导体结构。

背景技术:

1、图1为现有技术中接合结构30的截面示意图,图1示出了上、下相对的第一平板焊盘10和第二平板焊盘20,第一平板焊盘10上具有第一纳米线11(例如,铜纳米线),第二平板焊盘20上具有第二纳米线21(例如,铜纳米线)。第一平板焊盘10和第二平板焊盘20通过第一纳米线11和第二纳米线21接合时,在第一平板焊盘10的边缘(也可以称为周缘)处的第一纳米线11和在第二平板焊盘20的边缘处的第二纳米线21之间会出现未连接的现象40。实际上,第一纳米线11与第二纳米线21之间的接触面积是焊盘(第一焊盘10或者第二焊盘20)的顶表面面积的30%-60%。因为第一平板焊盘10和第二平板焊盘20之间的接触面积较小,导致电连接不理想。

2、因为第一纳米线11和第二纳米线21对接时,由于第一平板焊盘10的边缘处的第一纳米线11和第二平板焊盘20的边缘处的第二纳米线21相互挤压时导致边缘处的第一纳米线11和第二纳米线21外窜,而第一焊盘10和第二焊盘20侧边均没有边界,因此边缘处的第一纳米线11和第二纳米线21是分散的,导致边缘处的第一纳米线11和第二纳米线21未相互接触而使电连接不理想。

3、当第一平板焊盘10设置于芯片50(为了聚焦在焊盘接合结构上,仅呈现芯片50的一部分)上,第二平板焊盘20设置于基板60(为了聚焦在焊盘接合结构上,仅呈现基板60的一部分)上时,芯片50与基板60通过接合结构30连接组成半导体结构70,边缘处的第一纳米线11和第二纳米线21未相互接触,导致芯片50与基板60的电性能较差/电性能降低。

技术实现思路

1、针对接合结构之间的电连接不理想的问题,本申请的实施例提出了一种接合结构,至少能够避免第一导电结构和/或第二导电结构的边缘处的第一线和第二线不能相互接触而导致的电连接不理想。

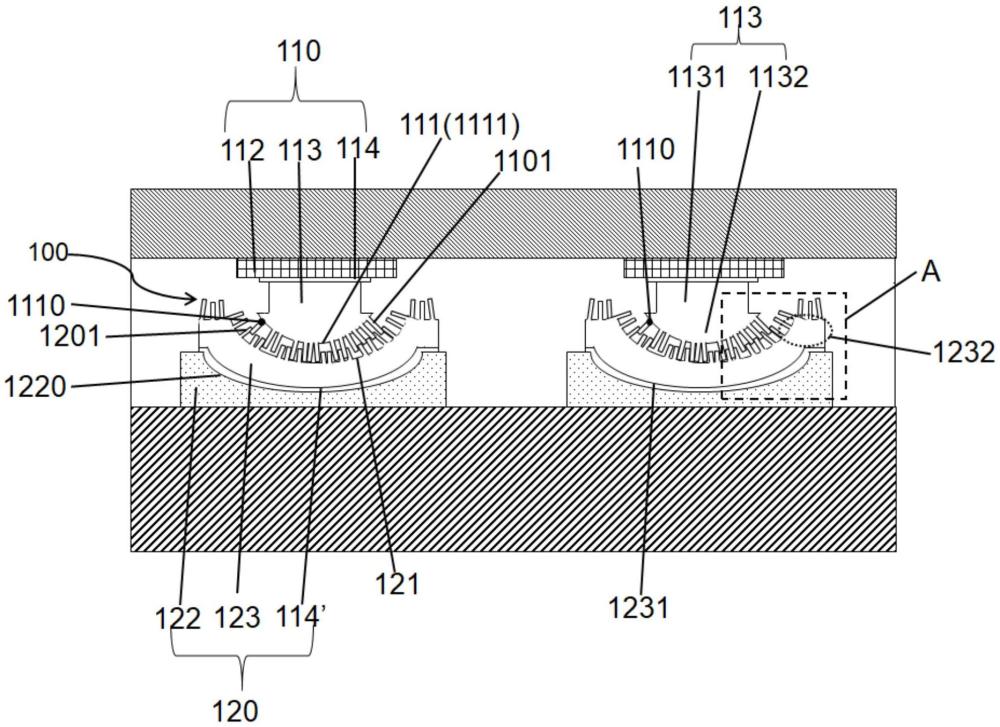

2、根据本申请的一个方面,提供了一种接合结构,该接合结构包括:第一导电结构,具有第一凸曲表面;第二导电结构,具有第二凹曲表面;多个第一线,沿着第一凸曲表面设置;多个第二线,沿着第二凹曲表面设置,多个第二线电连接多个第一线。

3、在一个或多个实施例中,多个第一线的延伸方向彼此不同。

4、在一个或多个实施例中,多个第一线以放射状方向由第一凸曲表面向外延伸。

5、在一个或多个实施例中,第一线与第一凸曲表面具有相交点,第一凸曲表面在相交点处的切线与第一线的延伸方向垂直。

6、在一个或多个实施例中,多个第二线的延伸方向彼此不同。

7、在一个或多个实施例中,第二导电结构的中心轴与第二凹曲表面的中心轴重合,多个第二线向第二导电结构的中心轴方向延伸。

8、在一个或多个实施例中,两个相邻的第二线之间的距离在从第二凹曲表面到第一凸曲表面的方向上渐缩。

9、在一个或多个实施例中,多个第一线和多个第二线均为纳米线。

10、在一个或多个实施例中,第二凹曲表面环绕包围第一凸曲表面。

11、针对芯片与基板的电性能较差/电性能降低的问题,本申请的实施例提出了一种半导体结构,至少能够避免接合结构的边缘处的电连接不理想而导致的芯片与基板的电性能较差/电性能降低。

12、根据本申请的另一个方面,提供了一种半导体结构,该半导体结构包括:芯片和基板,其中,芯片和基板通过上述任一种接合结构连接,第一导电结构设置在芯片上,第二导电结构设置在基板上。

13、本实用新型的技术效果包括:本实用新型提供的接合结构能够避免第一导电结构和/或第二导电结构的边缘处的第一线和第二线不能相互接触而导致的电连接不理想。当接合结构用于包括芯片和基板的半导体结构的时候,本实用新型提供的半导体结构能够避免芯片与基板的电性能降低。

技术特征:

1.一种接合结构,其特征在于,包括:

2.根据权利要求1所述的接合结构,其特征在于,所述多个第一线的延伸方向彼此不同。

3.根据权利要求2所述的接合结构,其特征在于,所述多个第一线以放射状方向由所述第一凸曲表面向外延伸。

4.根据权利要求3所述的接合结构,其特征在于,所述第一线与所述第一凸曲表面具有相交点,所述第一凸曲表面在所述相交点处的切线与所述第一线的延伸方向垂直。

5.根据权利要求1所述的接合结构,其特征在于,所述多个第二线的延伸方向彼此不同。

6.根据权利要求5所述的接合结构,其特征在于,所述第二导电结构的中心轴与所述第二凹曲表面的中心轴重合,所述多个第二线向所述第二导电结构的中心轴方向延伸。

7.根据权利要求5所述的接合结构,其特征在于,两个相邻的所述第二线之间的距离在从所述第二凹曲表面到所述第一凸曲表面的方向上渐缩。

8.根据权利要求1所述的接合结构,其特征在于,所述多个第一线和所述多个第二线均为纳米线。

9.根据权利要求1所述的接合结构,其特征在于,所述第二凹曲表面环绕包围所述第一凸曲表面。

10.一种半导体结构,包括:芯片和基板,其特征在于,所述芯片和所述基板通过权利要求1-9中任意一项所述的接合结构连接,所述第一导电结构设置在所述芯片上,所述第二导电结构设置在所述基板上。

技术总结

本申请的实施例公开了一种接合结构,该接合结构包括:第一导电结构,具有第一凸曲表面;第二导电结构,具有第二凹曲表面;多个第一线,沿着第一凸曲表面设置;多个第二线,沿着第二凹曲表面设置,多个第二线电连接多个第一线。上述技术方案至少能够避免第一导电结构和/或第二导电结构的边缘处的第一线和第二线不能相互接触而导致的电连接不理想。本申请的实施例还提供了一种半导体结构,该半导体结构包括:芯片和基板,其中,芯片和基板通过本申请的接合结构连接,第一导电结构设置在芯片上,第二导电结构设置在基板上。本申请的半导体结构至少能够避免接合结构的边缘处的电连接不理想而导致的芯片与基板的电性能较差/电性能降低。

技术研发人员:吕文隆

受保护的技术使用者:日月光半导体制造股份有限公司

技术研发日:20230712

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!