LDMOS器件的制作方法

本技术涉及半导体集成电路设计与制造,特别涉及一种ldmos器件。

背景技术:

1、横向双扩散金属氧化物半导体场效应晶体管(lateral double diffusedmosfet,ldmos)是上世纪九十年代发展起来的一种功率半导体器件。由于具有高增益、高线性、高耐压、高输出功率等技术特点,因此ldmos广泛应用在射频无线通信领域,如无线电短波通讯、基站、长距离发射机等领域。

2、在射频应用之中,射频ldmos(rf ldmos)作为放大器的核心元件,往往工作于不同的偏置条件下,射频信号通过栅极输入,放大后从漏区输出(源区接地)。当射频信号输入时,栅极电压的高速变化就使得沟道区域在反型(导通)和空穴积累(开启)两个状态之间高速切换。这就要求射频ldmos具有更高的抗干扰能力,避免源极和漏极的信号对栅极的干扰,以满足ldmos器件更高的频率特性。

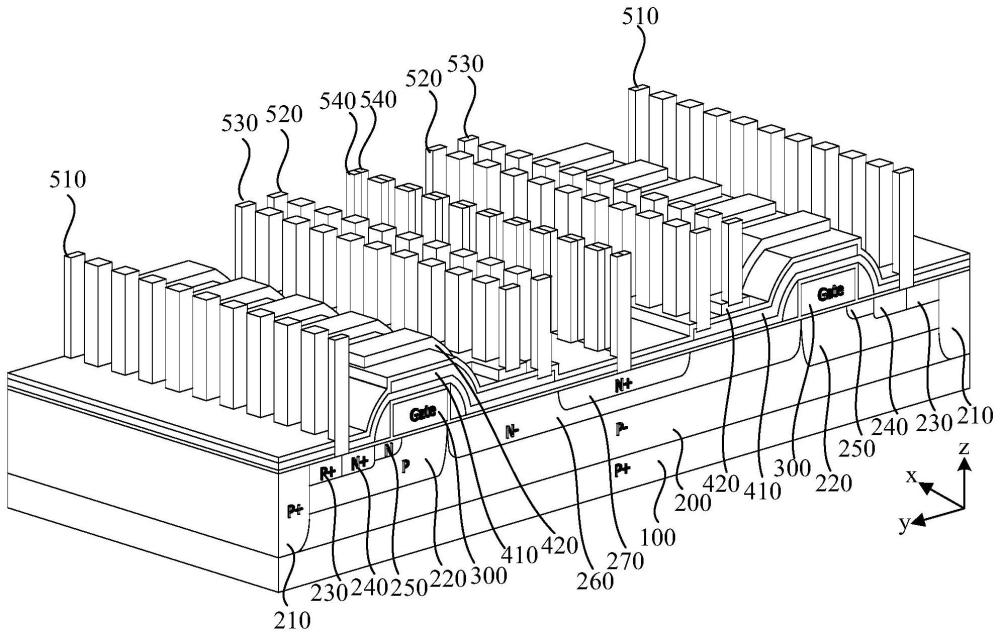

3、图1示出了根据现有技术的一种ldmos器件的结构示意图;图2示出了图1所示的ldmos器件的剖面示意图。为了更清楚的展示ldmos器件的立体结构,图1省略了图2中的金属层metal1和metal2。参见图1和图2,ldmos器件包括衬底10、外延层20、下沉区(sinker)21、沟道区22、接触区23、源区24、扩散区25、漂移区26、漏区27、栅极介质层、栅极30、法拉第结构、接触柱51、接触柱52、接触柱53、接触柱54、金属层metal1以及金属层metal2。为实现rf ldmos的高频应用,往往还需要在栅极和漂移区上设置法拉第结构。比如图1和图2所示的ldmos器件中,法拉第结构采用双层结构,包括第一法拉第层41和第二法拉第层42。法拉第结构设置在栅极30(输入端)和漏区27(高电平)之间,通过接触柱52-53以及金属层metal1与源区24电连接。

4、为充分屏蔽来自漏区27的信号干扰,提高栅极30的稳定性,进而提高ldmos器件的频率特性,法拉第结构最好覆盖整个栅极30的顶部,但又会增大输入电容,继而影响ldmos器件的开关时间和响应速度。因此,有待提出一种新的ldmos器件,以在不增大输入电容的前提下有效屏蔽干扰信号,提高ldmos器件的频率特性。

技术实现思路

1、鉴于上述问题,本实用新型的目的在于提供一种ldmos器件,其法拉第结构可以在不增大输入电容的前提下充分屏蔽来自漏区的干扰信号。

2、为实现上述目的,本实用新型提供的ldmos器件,包括:

3、半导体基板;

4、位于半导体基板中的沟道区和漂移区,沟道区中设有源区,漂移区中设有漏区;

5、位于半导体基板上且层叠设置的栅极介质层和栅极,栅极朝向漏区的一侧设有第一侧墙,栅极朝向源区的一侧设有第二侧墙;以及

6、法拉第结构,覆盖栅极的顶面和第一侧墙并延伸覆盖漂移区,

7、其中,法拉第结构包括至少两层法拉第层,至少两层法拉第层部分互补,以共同至少覆盖栅极的顶面。

8、进一步地,法拉第层包括梳状插指结构,梳状插指结构包括第一主干部和多个分支部,第一主干部至少覆盖漂移区并沿第一方向延伸,分支部的一端连接在第一主干部朝向栅极的一侧并沿第二方向延伸,且多个分支部沿第一方向间隔排列;至少两层法拉第层的分支部互补,以共同覆盖栅极的顶面,或者共同覆盖栅极的顶面和第一侧墙;

9、其中,第一方向为栅宽方向,第二方向为栅长方向。

10、进一步地,法拉第层的分枝部包括弧形板和条形板,弧形板的一端连接在第一主干部朝向栅极的一侧,弧形板的另一端与条形板的一端连接;

11、至少两层法拉第层的弧形板互补,以共同覆盖第一侧墙;至少两层法拉第层的条形板互补,以共同覆盖栅极的顶面。

12、进一步地,至少两个法拉第层的分支部在半导体基板上的正投影重叠,重叠面积不超过法拉第结构的分支部在半导体基板上正投影总面积的10%;或者,

13、至少两个法拉第层的分支部在半导体基板上的正投影之间留有间隙,间隙面积不超过法拉第结构的分支部在半导体基板上正投影总面积的10%。

14、进一步地,法拉第结构包括层叠设置的第一法拉第层和第二法拉第层,第一法拉第层相对更靠近栅极和漂移区。

15、进一步地,沿第一方向,第一法拉第层的分枝部的宽度小于第二法拉第层的分枝部的宽度。

16、进一步地,第一法拉第层还包括第二主干部,第二主干部沿第一方向延伸,且第二主干部朝向漏区的一侧与多个分支部的另一端连接。

17、进一步地,在相邻两层法拉第层中,底部的法拉第层覆盖漂移区的部分被顶部的法拉第层部分覆盖。

18、进一步地,至少一层法拉第层朝向源区的一侧的部分区域沿第二方向延伸至第二侧墙和源区上方,形成延伸部;延伸部与第二侧墙、源区之间以介质层分隔,且延伸部上设有导电结构以将该至少一层法拉第层引出。

19、进一步地,半导体基板为衬底片,或者,半导体基板为外延片,外延片包括衬底和外延层,沟道区和漂移区位于外延层中。

20、本实用新型提供的ldmos器件,其法拉第结构包括至少两层法拉第层,至少两层法拉第层部分互补,从而能够共同覆盖栅极的顶面,或者共同覆盖栅极顶面以及栅极靠近漏区的第一侧墙,从而可以充分屏蔽来自漏区的干扰信号,并且不会增加ldmos器件的输入电容,提升ldmos器件的频率特性。

21、在优选的实施例中,法拉第结构包括叠设的第一法拉第层和第二法拉第层,两个法拉第层均采用梳状插指结构,相较于现有的法拉第结构,既可以降低第一法拉第层与栅极之间的重叠面积,又可以增加第二法拉第层与栅极之间的距离,从而能够进一步降低ldmos器件的输入电容。

22、在更为优选的实施例中,两个法拉第层均包括第一主干部和分支部,分支部结构互补,通过控制两个法拉第层的分支部的尺寸等条件,能够进一步降低ldmos器件的输入电容,进而提升ldmos器件的频率特性。

技术特征:

1.一种ldmos器件,其特征在于,包括:

2.根据权利要求1所述的ldmos器件,其特征在于,所述法拉第层包括梳状插指结构,所述梳状插指结构包括第一主干部和多个分支部,所述第一主干部至少覆盖漂移区并沿第一方向延伸,所述分支部的一端连接在所述第一主干部朝向栅极的一侧并沿第二方向延伸,且多个分支部沿第一方向间隔排列;所述至少两层法拉第层的分支部互补,以共同覆盖所述栅极的顶面,或者共同覆盖所述栅极的顶面和所述第一侧墙;

3.根据权利要求2所述的ldmos器件,其特征在于,所述法拉第层的分枝部包括弧形板和条形板,所述弧形板的一端连接在所述第一主干部朝向栅极的一侧,所述弧形板的另一端与所述条形板的一端连接;

4.根据权利要求2所述的ldmos器件,其特征在于,

5.根据权利要求2-4任一项所述的ldmos器件,其特征在于,所述法拉第结构包括层叠设置的第一法拉第层和第二法拉第层,所述第一法拉第层相对更靠近所述栅极和所述漂移区。

6.根据权利要求5所述的ldmos器件,其特征在于,沿第一方向,所述第一法拉第层的分枝部的宽度小于所述第二法拉第层的分枝部的宽度。

7.根据权利要求5所述的ldmos器件,其特征在于,所述第一法拉第层还包括第二主干部,所述第二主干部沿第一方向延伸,且所述第二主干部朝向所述漏区的一侧与所述分支部的另一端连接。

8.根据权利要求1-4任一项所述的ldmos器件,其特征在于,在相邻两层法拉第层中,底部的法拉第层覆盖漂移区的部分被顶部的法拉第层部分覆盖。

9.根据权利要求1-4任一项所述的ldmos器件,其特征在于,至少一层法拉第层朝向所述源区的一侧的部分区域沿第三方向延伸至所述第二侧墙和源区上方,形成延伸部;所述延伸部与所述第二侧墙、所述源区之间以介质层分隔,且所述延伸部上设有导电结构以将所述至少一层法拉第层引出。

10.根据权利要求1-4任一项所述的ldmos器件,其特征在于,所述半导体基板为衬底片,

技术总结

本技术公开了一种LDMOS器件,包括:衬底;位于半导体基板中的沟道区和漂移区,沟道区中设有源区,漂移区中设有漏区;位于半导体基板上且层叠设置的栅极介质层和栅极,栅极朝向漏区的一侧设有第一侧墙,栅极朝向源区的一侧设有第二侧墙;以及法拉第结构,覆盖栅极的顶面和第一侧墙并延伸覆盖漂移区,其中,法拉第结构包括至少两层法拉第层,至少两层法拉第层部分互补,以共同至少覆盖栅极的顶面。本技术提供的LDMOS器件,通过对其法拉第结构进行改进可以充分屏蔽来自漏区的干扰信号,且不增加输入电容,从而能够提升LDMOS器件的频率特性。

技术研发人员:邢岳,周源,刘园园

受保护的技术使用者:北京燕东微电子科技有限公司

技术研发日:20230717

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!