一种高速开关通道结构的制作方法

本技术涉及高速开关,更具体的说是涉及一种高速开关通道结构。

背景技术:

1、目前,高速开关集成电路是在移动便携式设备中广泛用到的一类集成电路,例如移动处理器接口开关,高速usb3.0,usb3.1开关等等,这一类电路的主要性能指标就是可通过的有效信号的带宽频率,在高速信号开关通道上的任何对地电容都会对高速信号产生衰减,降低可通过信号的带宽。这就要求在信号通路上,需要尽量降低对地寄生电容。

2、但是,现有的降低该寄生电容的办法通常是高速通道互联线采用顶层金属,通过增加芯片互联金属层数,例如采用5层或6层金属,这样使得最顶层的金属互联线到衬底地之间的层间介质厚度增加,就可实现电容的降低,但是这样带来了较大的工艺成本增加,因为每增加一层金属就要额外增加两个工艺层次,10%以上的晶圆工艺成本,急剧增加芯片成本,而每增加一层金属产生的降低寄生电容的效果又会随着总介质厚度的增加变得也会越来越小。

3、因此,如何提供一种能够解决上述问题的高速开关通道结构是本领域技术人员亟需解决的问题。

技术实现思路

1、有鉴于此,本实用新型提供了一种高速开关通道结构,通过在高速电路的通道金属下方的衬底地上,形成多个pn结,通过反向偏置各个pn结,形成串联pn结电容,实现降低高速通道金属对地寄生电容,从而降低高频信号传输衰减,工艺过程不需要增加额外的工艺光罩层次,可低成本地有效解决金属互联线对高速芯片带来的寄生电容问题。

2、为了实现上述目的,本实用新型采用如下技术方案:

3、一种高速开关通道结构,包括:开关mos管、顶层金属层、p阱层、深n阱层及衬底;

4、所述衬底上依次设置有所述深n阱层及所述p阱层,所述顶层金属层设置在所述p阱层远离所述深n阱层的一侧,且所述开关mos管设置在所述衬底上。

5、优选的,还包括:第一金属层间介质层,所述第一金属层间介质层设置于所述顶层金属层及所述p阱层之间。

6、优选的,还包括:第二金属层间介质层及第三金属层间介质层,所述第二金属层间介质层及所述第三金属层间介质层依次设置于所述第一金属层间介质层之上。

7、优选的,所述第一金属层间介质层及所述第二金属层间介质层之间设置有金属一,所述第二金属层间介质层及所述第二金属层间介质层之间设置有金属二。

8、优选的,还包括:浅槽介质层,所述浅槽介质层设置于所述p阱层及所述第一金属层间介质层之间。

9、优选的,还包括:顶层金属层沿开关通道方向边界图形包含在p阱层图形中,p阱层边界包含顶层金属层的包边尺寸为0-10μm。

10、优选的,还包括:深n阱偏置电位引出端及阱偏置电位引出端,所述深n阱偏置电位引出端设置于所述深n阱层上,所述阱偏置电位引出端设置于所述p阱层上。

11、进一步,本实用新型还提供一种高速通道结构的制备工艺,其特征在于,包括:

12、步骤s1:在所述衬底上热生长一层初始氧化层,在初始氧化层上旋涂深n阱光刻胶,用深n阱进行光刻形成深n阱图形注入窗口;

13、步骤s2:进行深n阱掺杂注入并移除光刻胶,清洗并进入炉管热扩散;

14、步骤s3:进行标准cmos集成电路前道工艺,形成所述p阱层和n阱。

15、优选的,还包括:

16、步骤s4:进入金属后道工艺,在所述p阱层的表面上淀积形成浅槽介质层,光刻出有源区接触孔,金属填充通孔,淀积形成所述第一金属层间介质层,接着淀积所述金属一和所述金属二之间的所述第二金属层间介质层,并化学机械研磨到指定厚度;

17、步骤s5:光刻出金属通孔,金属填充通孔,淀积所述金属二,光刻刻蚀出第二层金属图形,淀积形成所述第三金属层间介质层,并化学机械研磨到指定厚度。

18、步骤s6:淀积钝化层,做钝化层焊盘窗口光刻并刻蚀出钝化层窗口,露出焊盘所述顶层金属层,合金后完成晶圆工艺过程。

19、经由上述的技术方案可知,与现有技术相比,本实用新型公开提供了一种高速开关通道结构,通过对顶层高速信号通道互联金属对地之间串联工艺本身包含的反偏多层嵌套的pn结电容来有效降低芯片级封装中高速通道的金属互联线对地寄生电容,降低高频信号传输衰减,而且工艺过程不需要增加额外的工艺层次,可低成本地降低高速信号通道金属互联的对地寄生电容。

技术特征:

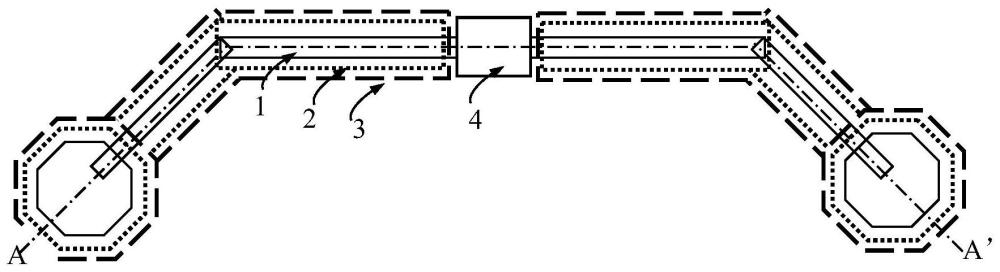

1.一种高速开关通道结构,包括一开关mos管(4),其特征在于,还包括:顶层金属层(1)、p阱层(2)、深n阱层(3)及衬底(11);

2.根据权利要求1所述的一种高速开关通道结构,其特征在于,还包括:第一金属层间介质层(6),所述第一金属层间介质层(6)设置于所述顶层金属层(1)及所述p阱层(2)之间。

3.根据权利要求2所述的一种高速开关通道结构,其特征在于,还包括:第二金属层间介质层(7)及第三金属层间介质层(8),所述第二金属层间介质层(7)及所述第三金属层间介质层(8)依次设置于所述第一金属层间介质层(6)之上。

4.根据权利要求3所述的一种高速开关通道结构,其特征在于,所述第一金属层间介质层(6)及所述第二金属层间介质层(7)之间设置有金属一(12),所述第二金属层间介质层(7)及所述第二金属层间介质层(7)之间设置有金属二(13)。

5.根据权利要求2所述的一种高速开关通道结构,其特征在于,还包括:浅槽介质层(5),所述浅槽介质层(5)设置于所述p阱层(2)及所述第一金属层间介质层(6)之间。

6.根据权利要求1所述的一种高速开关通道结构,其特征在于,还包括:顶层金属层(1)沿开关通道方向边界图形包含在p阱层(2)图形中,p阱层(2)边界包含顶层金属层(1)的包边尺寸范围为0-10μm。

7.根据权利要求1所述的一种高速开关通道结构,其特征在于,还包括:深n阱偏置电位引出端(17)及阱偏置电位引出端(18),所述深n阱偏置电位引出端(17)设置于所述深n阱层(3)上,所述阱偏置电位引出端(18)设置于所述p阱层(2)上。

技术总结

本技术公开了一种高速开关通道结构,包括:开关MOS管、顶层金属层、P阱层、深N阱层及衬底;所述衬底上依次设置有所述深N阱层及所述P阱层,所述顶层金属层设置在所述P阱层远离所述深N阱层的一侧,且所述开关MOS管设置在所述衬底上;本技术通过在高速电路的通道金属下方的衬底地上,形成多个PN结,通过反向偏置各个PN结,形成串联PN结电容,实现降低高速通道金属对地寄生电容的效果。

技术研发人员:吕宇强,鞠建宏,倪胜中

受保护的技术使用者:江苏帝奥微电子股份有限公司

技术研发日:20230718

技术公布日:2024/2/8

- 还没有人留言评论。精彩留言会获得点赞!