一种埋入式芯片封装结构的制作方法

本技术涉及芯片封装加工制造,更具体的是涉及一种埋入式芯片封装结构。

背景技术:

1、芯片封装是指安装半导体集成电路芯片时采用的外壳,是电路集成术语,是把集成电路装配为芯片最终产品的过程,其主要用于保护芯片、增强芯片电热性能的作用。现有的部分针对多芯片进行封装的工艺,将若干芯片自下而上罗列并逐一进行连接的封装方式,易造成上方芯片与基板之间的电阻阻值过大,从而导致较大的功率消耗并影响封装结构的效能,不满足电子产品轻薄化的发展方向。

技术实现思路

1、本实用新型的目的在于,提供一种埋入式芯片封装结构,用以解决现有的部分封装结构将若干数量的芯片自下而上罗列并逐一进行连接的封装方式,使得功率消耗过大并影响封装结构效能的问题。

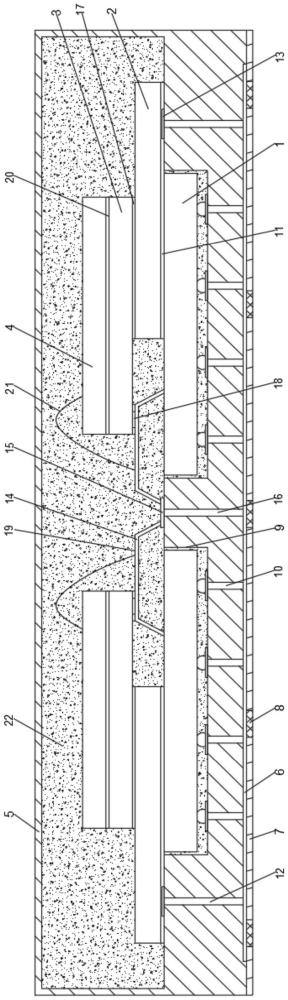

2、为实现上述目的,本实用新型提供一种埋入式芯片封装结构,包括预设空腔的基板以及若干第一芯片,每个第一芯片的上表面依次设有一个第二芯片、一个第三芯片和一个第四芯片,基板的底面依次设有第一布线层和绝缘层;

3、基板空腔的底面开设有若干与每个第一芯片相适配的凹槽,每个凹槽内开设有若干第一通孔,每个第一通孔内均设有一个第一导电连接件,每个第一导电连接件的一端均与所在凹槽内的第一芯片电性连接,每个第一导电连接件的另一端均与第一布线层之间电性连接,绝缘层上开设有若干通槽,每个通槽内分别固接有一个与第一布线层电性连接的第四导电连接件。

4、优选的,每个第二芯片的下表面通过第一粘接层分别与每个第一芯片及基板空腔的底面固接,基板空腔的底面且位于每个第二芯片的下方分别开设有一个第二通孔,每个第二通孔内均设有一个与第一布线层电性连接的第二导电连接件,每个第二芯片分别通过设于每个第一粘接层内的第一间隔件与每个第二导电连接件之间电性连接。

5、优选的,每个第三芯片的下表面均设有一个支撑板,每个支撑板的一侧底面与第一芯片的上表面固接,另一侧底面共同固接有一个与基板空腔底面固接的第二间隔件,基板空腔底面且位于第二间隔件的下方开设有第三通孔,第三通孔内设有两端分别与第二间隔件以及第一布线层电性连接的第三导电连接件。

6、优选的,每个第三芯片与支撑板及第二芯片之间通过第二粘接层固接,每个第三芯片与支撑板之间的第二粘接层内均设有一个与第三芯片电性连接的第三间隔件,每个支撑板上均设有与第三间隔件电性连接的第二布线层,每个第二布线层均与第二间隔件之间电性连接。

7、优选的,每个第四芯片的下表面分别通过第三粘接层与第三芯片之间固接,每个第四芯片均通过焊线与其下端第三芯片所固接支撑板上的第二布线层电性连接。

8、优选的,基板空腔内填充有填充胶。

9、本实用新型与现有技术相比,其显著优点是:

10、1、相较于现有的部分封装结构将若干芯片自下而上罗列并逐一进行连接的封装方式,易造成上方芯片与基板间的电阻阻值较大,致使较大的功率消耗;而本实用新型通过将第一芯片、第二芯片、第三芯片及第四芯片分别与第一布线层之间进行电性连接,则缩短了封装结构上的连接路径,以此避免了最上方芯片与基板间较大的电阻值,降低功率消耗的同时也降低了对封装结构效能的影响,从而实现电子产品轻薄化与小型化。

11、2、相较于现有的部分直接采用液态胶封装的方式,涂胶量很难控制,易产生溢胶的情况,同时在放置芯片时,胶因挤压而致使芯片产生位移或倾斜,而本实用新型中,通过凹槽对第一芯片进行限位,随即通过第一粘接层、第二粘接层和第三粘接层分别对第二芯片、第三芯片与第四芯片进行初步的限位、固定,从而降低了封装过程中发生位移或倾斜的情况。

技术特征:

1.一种埋入式芯片封装结构,其特征在于,包括:预设空腔的基板(5)以及若干第一芯片(1),每个所述第一芯片(1)的上表面依次设有一个第二芯片(2)、一个第三芯片(3)和一个第四芯片(4),所述基板(5)的底面依次设有第一布线层(6)和绝缘层(7);

2.根据权利要求1所述的一种埋入式芯片封装结构,其特征在于:每个所述第二芯片(2)的下表面通过第一粘接层(11)分别与每个第一芯片(1)及基板(5)空腔的底面固接,所述基板(5)空腔的底面且位于每个第二芯片(2)的下方分别开设有一个第二通孔,每个第二通孔内均设有一个与第一布线层(6)电性连接的第二导电连接件(12),每个第二芯片(2)分别通过设于每个第一粘接层(11)内的第一间隔件(13)与每个第二导电连接件(12)之间电性连接。

3.根据权利要求2所述的一种埋入式芯片封装结构,其特征在于:每个所述第三芯片(3)的下表面均设有一个支撑板(14),每个支撑板(14)的一侧底面与第一芯片(1)的上表面固接,另一侧底面共同固接有一个与基板(5)空腔底面固接的第二间隔件(15),所述基板(5)空腔底面且位于第二间隔件(15)的下方开设有第三通孔,所述第三通孔内设有两端分别与第二间隔件(15)以及第一布线层(6)电性连接的第三导电连接件(16)。

4.根据权利要求3所述的一种埋入式芯片封装结构,其特征在于:每个所述第三芯片(3)与支撑板(14)及第二芯片(2)之间通过第二粘接层(17)固接,每个所述第三芯片(3)与支撑板(14)之间的第二粘接层(17)内均设有一个与第三芯片(3)电性连接的第三间隔件(18),每个所述支撑板(14)上均设有与第三间隔件(18)电性连接的第二布线层(19),每个所述第二布线层(19)均与第二间隔件(15)之间电性连接。

5.根据权利要求4所述的一种埋入式芯片封装结构,其特征在于:每个所述第四芯片(4)的下表面分别通过第三粘接层(20)与第三芯片(3)之间固接,每个所述第四芯片(4)均通过焊线(21)与其下端第三芯片(3)所固接支撑板(14)上的第二布线层(19)电性连接。

6.根据权利要求1或5所述的一种埋入式芯片封装结构,其特征在于:所述基板(5)空腔内填充有填充胶(22)。

技术总结

本技术涉及一种埋入式芯片封装结构,该埋入式芯片封装结构包括预设空腔的基板以及若干第一芯片,每个第一芯片上表面依次设有一个第二芯片、第三芯片和第四芯片,基板的底面依次设有第一布线层和绝缘层;相较于现有的部分封装结构将若干芯片进行罗列的方式易造成上方芯片与基板间电阻阻值过大,从而导致较大的功率消耗;本技术的第一芯片、第二芯片、第三芯片和第四芯片分别通过第一导电连接件、第二导电连接件、第三导电连接件与第一布线层之间电性连接,以此降低同一平面上封装结构的体积;同时缩短了封装结构上的连接路径,降低功率消耗。

技术研发人员:陈一杲,王春华,陈诚,苏玉燕,汤勇

受保护的技术使用者:天芯电子科技(南京)有限公司

技术研发日:20230802

技术公布日:2024/2/1

- 还没有人留言评论。精彩留言会获得点赞!