一种半导体场效应管器件的制作方法

本技术涉及于功率半导体器件,特别是屏蔽栅沟槽型场效应管器件的结构及其制造方法。

背景技术:

1、以下将对现有的屏蔽栅沟槽型场效应管的相关技术背景进行说明。需指出的是,本文件中所述的对应位置词如“上”、“下”、“左”、“右”、“前”、“后”、“垂直”、“水平”、“竖直”是对应于参考图示的相对位置。具体实施中并不限制固定方向。需指出,附图中的器件并不一定按具体比例绘画。附图中的掺杂区和沟槽的边界所示的直线,以及由该边界所形成的尖角,在实际应用中一般并非直线和精确的角。

2、屏蔽栅沟槽型场效应管,作为一种新型的功率器件,具有导通电阻低,开关速度快的特点。屏蔽栅沟槽型场效应管的结构特点是在沟槽内有相互隔离的栅电极和屏蔽栅电极,其中,屏蔽栅电极位于栅电极下方,并且需要连接到上表面金属。

3、场效应管器件在开关过程中,尤其是多个场效应管并联使用的场合下,提高栅源电容(cgs)与栅漏电容(cgd)的比值,有利于防止器件误开通导致的器件损坏。传统设计中,栅源电容(cgs)与栅漏电容(cgd)的比值通常由器件的结构确定。

4、高可靠性应用如汽车、轨道交通等,需要确保场效应管器件参数在长时间使用中保持稳定,确保电路安全。但在实际应用过程中,水汽或者外来污染物离子可能侵入到场效应管器件芯片中,影响阈值电压、漏电、击穿电压等参数。因此,需要设置高可靠性的器件终端区域,防止外来污染或可动离子进入芯片有源区域。

5、在屏蔽栅沟槽型场效应管中,深沟槽结构可能导致芯片表面应力较严重,热胀冷缩下终端区域的表面氧化层和钝化层容易产生龟裂或者分层,导致水汽或者外来污染物离子更容易入侵半导体内部,导致器件失效。

6、另外,部分高可靠性对器件的栅电极的静电防护性能有一定的要求,需要在场效应管的栅极和源极之间设置钳位保护电路,例如并联齐纳二极管结构。上述集成静电保护电路的场效应管,总的工艺流程通常需要八到十个光刻步骤,工艺成本较为高昂,有必要提出减少光刻步骤的制造工艺以节省成本。

技术实现思路

1、针对上文中所提到的现有屏蔽栅沟槽型场效应管器件的问题,有需要提出一种高可靠性的工艺简单的屏蔽栅沟槽型场效应管结构及工艺流程。

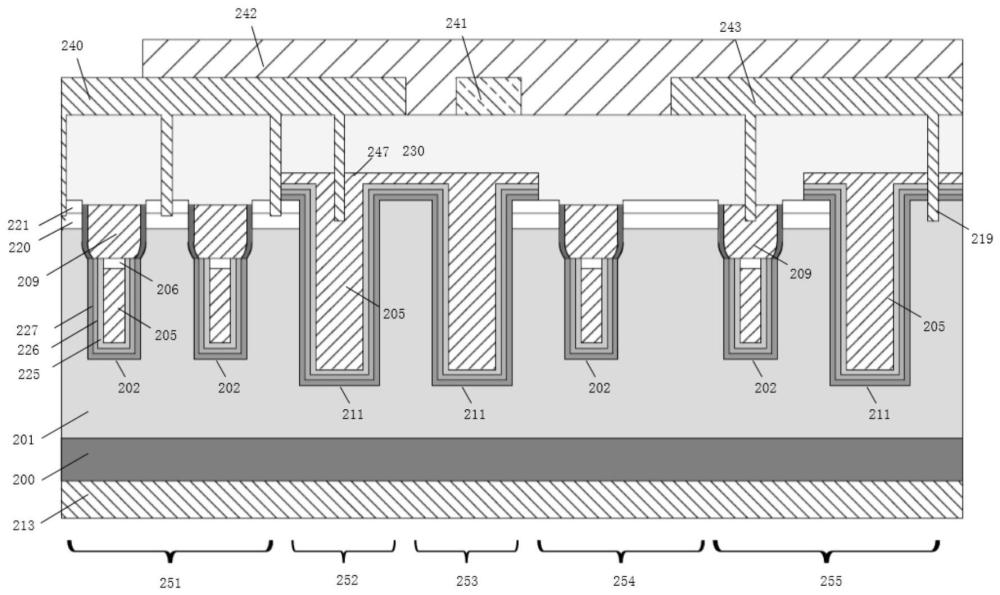

2、一种半导体场效应管器件,所述的器件包括有位于器件底部的漏极金属层、位于漏极金属层之上的第一导电型重掺杂衬底层和位于第一导电型重掺杂衬底层之上的第一导电型外延层;位于器件上表面的第二导电型掺杂体区和第一导电型重掺杂源区;位于器件顶部的氧化层、源极金属层和栅极金属层;位于器件边缘且位于源极金属层和栅极金属层上方的钝化层;所述的器件上表面向下延伸有第一类沟槽和第二类沟槽,所述的第一类沟槽包含有第一屏蔽栅电极和栅电极,所述的第二类沟槽包含有第二屏蔽栅电极和由所述的第二屏蔽栅电极向上延伸形成的表面多晶硅层;所述的器件至少包括用于在器件开通时提供电流导通区域的有源区域、使反偏时源极-漏极之间的电场位于有源区域内以防止器件外围区域击穿的终端沟槽区域、为器件提供额外的cgs并改善开关性的栅-源电容区域、用于减少器件周期排列的沟槽所产生应力的应力释放区域和电场截止区域。

3、其中所述的有源区域由一系列的第一类沟槽构成;所述的终端沟槽区域由一段以上相互平行的第二类沟槽构成,该区域中的第二类沟槽中的第二屏蔽栅电极和所述的源极金属层相连;所述的栅-源电容区域包含一段以上相互平行的第二类沟槽,该区域中的第二屏蔽栅电极和所述的源极金属层相连,位于该区域的栅极金属和该区域的表面多晶硅层形成竖直方向的栅-源电容;所述的应力释放区域最少包含一段围绕栅-源电容区域的第一类沟槽;所述的电场截止区域至少包括一段围绕所述应力释放区域的第一类沟槽、围绕该区域的第一类沟槽的第二类沟槽、围绕该区域第二类沟槽的用于连接器件外围的半导体区域和该区域的第二类沟槽中的第二屏蔽栅电极的接触孔。

4、作为优选的,屏蔽栅电极和沟槽侧壁之间依次设有第一隔离层、第二隔离层和第三隔离层,其中第二隔离层的组成材料和第一、三隔离层不同。

5、更进一步的,第三类沟槽介质层在沟槽下方的厚度比沟槽上方的厚度宽。

6、作为优选的,所述的电场截止区域还包括位于上方的电场截止金属层,该电场截止金属层通过接触孔连接到电场截止区域内的第一类沟槽中的栅电极中,且和外围接触孔相连。

7、作为优选的,终端沟槽区域中的第二类沟槽的正下方有第二导电型注入离子区域。

8、作为优选的,所述的栅-源电容区域中的氧化层内设有栅极多晶硅层,所述的栅极多晶硅层和该区域的表面多晶硅层形成竖直方向的栅-源电容。

9、作为优选的,应力释放区域内的第一类沟槽外围设有多段无效沟槽。

10、更进一步的,所述的无效沟槽为第一类沟槽且沟槽内栅极电极和第一屏蔽栅电极未连接到外部电极且为浮空电位,或者所述的无效沟槽为绝缘物填充沟槽。

11、作为优选的,所述的器件还包括有和终端沟槽区域相邻的静电保护区域以及和所述的静电保护区域相邻的栅极沟槽区域;所述的静电保护区域包含有一层位于半导体上方的表面多晶硅层,该多晶硅层分别连接到终端沟槽区域和栅极沟槽区域内的第二屏蔽栅电极;该多晶硅层内设有水平方向设置的齐纳二极管结构。

12、作为优选的,所述的静电保护区域内还设有第二类沟槽,用于限定静电保护区域的位置。

13、作为优选的,位于器件上方的栅极金属和多晶硅层形成竖直方向的电容结构。

14、作为优选的,所述的器件包括有两个以上的有源区域,各有源区域中的沟槽方向平行或者垂直,有源区域通过静电保护区域连接到栅极沟槽区域。

15、本实用新型的有益效果在于:提出一种新型屏蔽栅沟槽型场效应管器件结构及制造工艺流程,比起传统结构和工艺,可以提高的栅源电容-栅漏电容比值,以及提供高可靠性的器件终端结构。

16、此外,在上述结构基础下提出一种集成有静电保护的器件结构。

17、此外,提出上述结构的制造方法,能够至少节省两道光刻步骤,有效降低制造成本。

技术特征:

1.一种半导体场效应管器件,所述的器件包括有位于器件底部的漏极金属层、位于漏极金属层之上的第一导电型重掺杂衬底层和位于第一导电型重掺杂衬底层之上的第一导电型外延层;位于器件上表面的第二导电型掺杂体区和第一导电型重掺杂源区;位于器件顶部的氧化层、源极金属层和栅极金属层;位于器件边缘且位于源极金属层和栅极金属层上方的钝化层;所述的器件上表面向下延伸有第一类沟槽和第二类沟槽,所述的第一类沟槽包含有第一屏蔽栅电极和栅电极,所述的第二类沟槽包含有第二屏蔽栅电极和由所述的第二屏蔽栅电极向上延伸形成的表面多晶硅层;

2.如权利要求1所述的半导体场效应管器件,其特征在于,

3.如权利要求1所述的半导体场效应管器件,其特征在于,屏蔽栅电极和沟槽侧壁之间依次设有第一隔离层、第二隔离层和第三隔离层,其中第二隔离层的组成材料和第一、三隔离层不同。

4.如权利要求3所述的半导体场效应管器件,其特征在于,第三类沟槽介质层在沟槽下方的厚度比沟槽上方的厚度宽。

5.如权利要求1所述的半导体场效应管器件,其特征在于,所述的电场截止区域还包括位于上方的电场截止金属层,该电场截止金属层通过接触孔连接到电场截止区域内的第一类沟槽中的栅电极中,且和外围接触孔相连。

6.如权利要求1所述的半导体场效应管器件,其特征在于,终端沟槽区域中的第二类沟槽的正下方有第二导电型注入离子区域。

7.如权利要求1所述的半导体场效应管器件,其特征在于,所述的栅-源电容区域中的氧化层内设有栅极多晶硅层,所述的栅极多晶硅层和该区域的表面多晶硅层形成竖直方向的栅-源电容。

8.如权利要求1所述的半导体场效应管器件,其特征在于,应力释放区域内的第一类沟槽外围设有多段无效沟槽。

9.如权利要求8所述的半导体场效应管器件,其特征在于,所述的无效沟槽为第一类沟槽且沟槽内栅极电极和第一屏蔽栅电极未连接到外部电极且为浮空电位,或者所述的无效沟槽为绝缘物填充沟槽。

10.如权利要求1所述的半导体场效应管器件,其特征在于,所述的器件还包括有和终端沟槽区域相邻的静电保护区域以及和所述的静电保护区域相邻的栅极沟槽区域;所述的静电保护区域包含有一层位于半导体上方的表面多晶硅层,该多晶硅层分别连接到终端沟槽区域和栅极沟槽区域内的第二屏蔽栅电极;该多晶硅层内设有水平方向设置的齐纳二极管结构。

11.如权利要求10所述的半导体场效应管器件,其特征在于,所述的静电保护区域内还设有第二类沟槽,用于限定静电保护区域的位置。

12.如权利要求10所述的半导体场效应管器件,其特征在于,位于器件上方的栅极金属和多晶硅层形成竖直方向的电容结构。

13.如权利要求10所述的半导体场效应管器件,其特征在于,所述的器件包括有两个以上的有源区域,各有源区域中的沟槽方向平行或者垂直,有源区域域通过静电保护区域连接到栅极沟槽区域。

技术总结

一种半导体场效应管器件及其制造方法,本技术涉及于功率半导体器件,所述半导体器的还包括用于在器件开通时提供电流导通区域的有源区域、使反偏时源极‑漏极之间的电场位于有源区域内以防止器件外围区域击穿的终端沟槽区域、为器件提供额外的Cgs并改善开关性的栅‑源电容区域、用于减少器件周期排列的沟槽所产生应力的应力释放区域和电场截止区域,比起传统结构和工艺,可以提高的栅源电容‑栅漏电容比值,以及提供高可靠性的器件终端结构。

技术研发人员:何梓维,梁嘉进,伍震威,单建安

受保护的技术使用者:安建科技有限公司

技术研发日:20230816

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!