一种VRDB测试结构的制作方法

本技术涉及半导体测试领域,特别涉及一种针对vrdb(voltage rampdielectric breakdown,电压斜坡介电击穿)测试结构。

背景技术:

1、对于量产芯片在出厂前都需要进行可靠性相关测试,而vrdb测试则是用来评估栅极氧化层质量的一种测试,vrdb测试是在加速条件下对样品芯片进行测试,以评估制程的可靠性。对于vrdb测试失败的样品经常会表现出burn out(熔融)的现象。针对这类样品,分析人员需要了解造成熔融的击穿点在vrdb测试结构中的具体位置,从而分析出击穿点位置与制程的相关性,并辅助厂内进行制程改善。但是,由于vrdb测试结构的表面覆盖了dummymetal(虚置金属块),从而无法从pv层(绝缘层)直接确定击穿点在test pattern(测试图形)的位置,所以需要先移除该测试pattern上面覆盖的dummy metal,并露出下方的测试图形。

2、但是,目前的处理方法存在以下两个问题:

3、1、因为击穿点已经呈现融熔的状态,使得该位置存在过研磨现象,而熔融点已经扩散导致目标结构受损,从而无法确定击穿点起始点的真正位置;

4、2、为应对一些平台制程需求,vrdb测试结构会有一些差异,目前在有源区的面积小于多晶硅栅极结构的面积的vrdb测试结构中,由于有源区被多晶硅栅极结构覆盖,当击穿点在poly pattern edge(多晶硅栅极图形边缘)时,尤其是aa pattern edge(有源区图形边缘)时,很难通过测试分析设备(例如top view sem)对击穿点的位置进行确认。

技术实现思路

1、本实施例提供一种vrdb测试结构,通过常规的测试分析设备在确认vrdb测试时可以准确地确认出击穿点的位置。

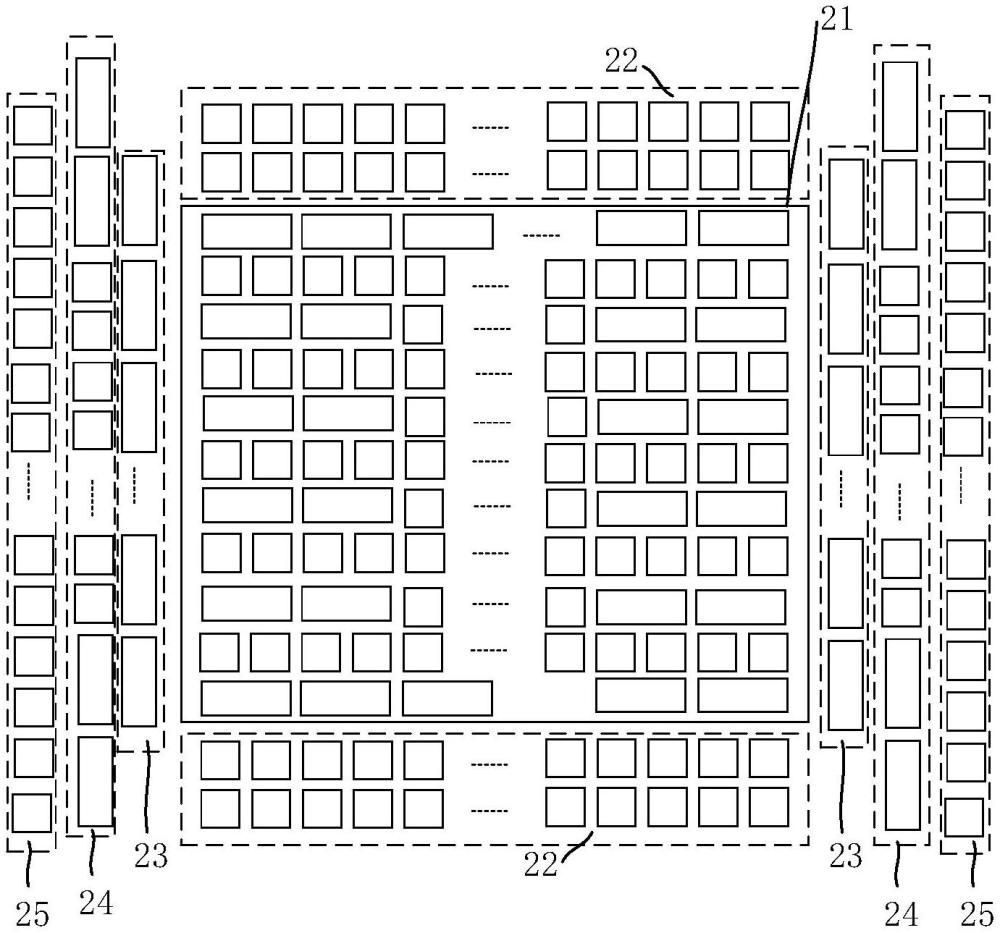

2、为了解决上述问题,本实用新型提供一种vrdb测试结构,包括形成于一衬底内的呈条状且平行间隔设置的第一个有源区至第m个有源区,依次位于所有所述有源区上的多晶硅栅极结构和金属层,所述金属层包括第一区块,所述第一区块的上侧和下侧均设置有一第二区块,所述第一区块的左侧和右侧由内向外均依次设置有一第三区块和一第四区块,其中,所述第一区块包括第一部分和第二部分,

3、所述第一部分位于所有所述有源区上方,且所述第一部分在所述有源区所在平面的投影位于所有所述有源区内,且与所述第一有源区的上侧边缘及所述第m有源区的下侧边缘重叠,所述第二部分位于相邻所述有源区之间的间隙上方;

4、两个所述第三区块分别位于所有所述有源区的左侧上方和右侧上方,且在所述有源区所在平面的投影分别与所有所述有源区的左侧边缘和右侧重叠;以及

5、所述第二区块和第四区块均设置在所述多晶硅栅极结构的外侧上方,且在所述多晶硅栅极结构所在平面的投影与所述多晶硅栅极结构的边缘重叠。

6、可选的,所述第一区块包括n行组合结构,且所述第一区块的每一行仅包括第一组合结构、第二组合结构或第三组合结构;

7、其中,所述第一部分包括第一组合结构和第三组合结构,每个所述有源区上方均设置有一第一组合结构或一第三组合结构,且所述第一个所述有源区和第m个所述有源区中均设置有所述第一组合结构;

8、所述第二部分包括第二组合结构,所述第二组合结构位于相邻所述有源区之间的间隙上方。

9、进一步的,所述第一区块的第一行、第10k+1行和第n行均设置有一所述第一组合结构,其中,k≥1,10k+1<n,n-10k-1<10,k为正整数;

10、所述第二组合结构中设置有多列间隔设置的虚拟孔,所有所述虚拟孔均位于相邻所述有源区之间的间隙上方。

11、进一步的,所述第一区块的第2i行上方均设置有一所述第二组合结构,

12、其中,2i<n,i≥1且为正整数。

13、进一步的,所述金属层由第一虚拟金属块、第二虚拟金属块和第三虚拟金属块组合形成,所述第一虚拟金属块的形状为正方形,所述第二虚拟金属块和第三虚拟金属块均为长方形,所述第二虚拟金属块的长边方向与x方向平行,所述第三虚拟金属块的长边方向与y方向平行,

14、其中,x方向和y方向相互垂直,所述第一虚拟金属块的边长为a,两两虚拟金属块之间的间隔固定且为b,所述第二虚拟金属块和第三虚拟金属块的长均为2a+b,宽均为a。

15、进一步的,所述第一组合结构由多个所述第二虚拟金属块沿x方向间隔设置,所述第二组合结构由多个所述第一虚拟金属块沿x方向间隔设置,所述第三组合结构由多个所述第一虚拟金属块和偶数个所述第二虚拟金属块沿x方向间隔设置;

16、在所述第三组合结构中,所有所述第一虚拟金属块沿x方向依次间隔设置,且沿x方向的两侧设置有等数量的所述第二虚拟金属块。

17、进一步的,所述第二区块包括第一子组合结构和第二子组合结构,所述第一子组合结构和第二子组合结构均由多个所述第一虚拟金属块沿x方向间隔设置;

18、所述第三区块由多个所述第三虚拟金属块沿y方向间隔设置;

19、所述第四区块由偶数个所述第三虚拟金属块和多个所述第一虚拟金属块组成,所有所述第一虚拟金属块沿y方向依次间隔设置,且沿y方向的两侧设置有等数量的所述第三虚拟金属块。

20、进一步的,在所述多晶硅栅极结构所在平面的投影上,每个所述第二区块的第一子组合结构位于所述多晶硅栅极结构和第二子组合结构之间,且每个所述第一子组合结构在所述多晶硅栅极结构所在平面上的投影与所述多晶硅栅极结构的上侧边缘或下侧边缘重叠。

21、可选的,两个所述第四区块分别位于所述多晶硅栅极结构的左侧上方和右侧上方,且每个所述第四区块在所述多晶硅栅极结构所在平面的投影与所述多晶硅栅极结构的左侧边缘或右侧边缘重叠;

22、所述有源区的左侧和右侧的衬底内均形成有第一体接触区,所述有源区的上侧和下侧的衬底内均形成有第二体接触区;

23、每个所述第一体接触区上方均设置有一第五区块,每个所述第二区块位于一所述第二体接触区上方,在所述第一区块的左侧或右侧,所述第四区块位于所述第五区块和第三区块之间。

24、进一步的,所述第五区块由多个所述第一虚拟金属块沿y方向间隔设置,所述第五区块在所述第一体接触区所在平面的投影与所述第一体接触区具有重叠区;

25、每个所述第二区块的第二子组合结构位于一所述第二体接触区的上方,且在所述第二体接触区所在平面的投影与所述第二体接触区具有交叠区域。

26、与现有技术相比,本实用新型具有以下有益效果:

27、本实用新型提供一种vrdb测试结构,包括形成于一衬底内的呈条状且平行间隔设置的第一个有源区至第m个有源区,依次位于所有所述有源区上的多晶硅栅极结构和金属层,所述金属层包括第一区块,所述第一区块的上侧和下侧均设置有一第二区块,所述第一区块的左侧和右侧由内向外均依次设置有一第三区块和一第四区块,其中,所述第一区块包括第一部分和第二部分,所述第一部分位于所有所述有源区上方,且所述第一部分在所述有源区所在平面的投影位于所有所述有源区内,且与所述第一有源区的上侧边缘及所述第m有源区的下侧边缘重叠,所述第二部分位于相邻所述有源区之间的间隙上方;两个所述第三区块分别位于所有所述有源区的左侧上方和右侧上方,且在所述有源区所在平面的投影分别与所有所述有源区的左侧边缘和右侧重叠;以及所述第二区块和第四区块均设置在所述多晶硅栅极结构的外侧上方,且在所述多晶硅栅极结构所在平面的投影与所述多晶硅栅极结构的边缘重叠,以取得意想不到的技术效果:在不接入电路的情况下,从绝缘层或者顶层金属层,通过第四区块快速准确地定位多晶硅栅极结构的边缘处的击穿点(即击穿点a)的位置,通过第一区块和第三区块快速准确地定位有源区的边缘处的击穿点(即击穿点b和c)的位置。

28、另外,本实用新型通过虚拟孔定位位于相邻有源区之间或者相邻子结构之间的击穿点(即击穿点d)的位置;通过第五区块快速准确地定位位于第一体接触区和/或第二体接触区处的击穿点(即击穿点e)的位置。

- 还没有人留言评论。精彩留言会获得点赞!