一种深沟槽隔离结构的改善方法与流程

本发明涉及微电子半导体,特别涉及一种深沟槽隔离结构的改善方法。

背景技术:

1、化学机械研磨(chemical mechanical polish,简称cmp)工艺是半导体制造工艺中非常关键的工艺之一,其可用于半导体结构中深沟槽隔离结构的制备。

2、目前,深槽隔离结构的制备过程具体为,在衬底内形成深槽,以化学气相沉积方式沉积氧化硅,再以多晶硅为堆积材料,用化学机械研磨(cmp)去除深槽外多余的多晶硅,并以氧化硅作为cmp的抛光停止层,在抓到终点后过抛一段时间,以去除多晶硅的残留。

3、然而,由于衬底上不同区域图形密度,对cmp工艺研磨速率的影响,导致利用现有工艺所形成的深沟槽隔离结构容易发生蚀坑或碟形坑的问题。

技术实现思路

1、本发明的目的在于提供一种深沟槽隔离结构的改善方法,以在将多晶硅层和第二硬掩膜层全部去除的同时,减少过研磨步骤的研磨时长,改善图形密集区和图形稀疏区的硬掩膜的厚度差,避免形成的深沟槽隔离结构表面发生蚀坑或碟形坑缺陷。

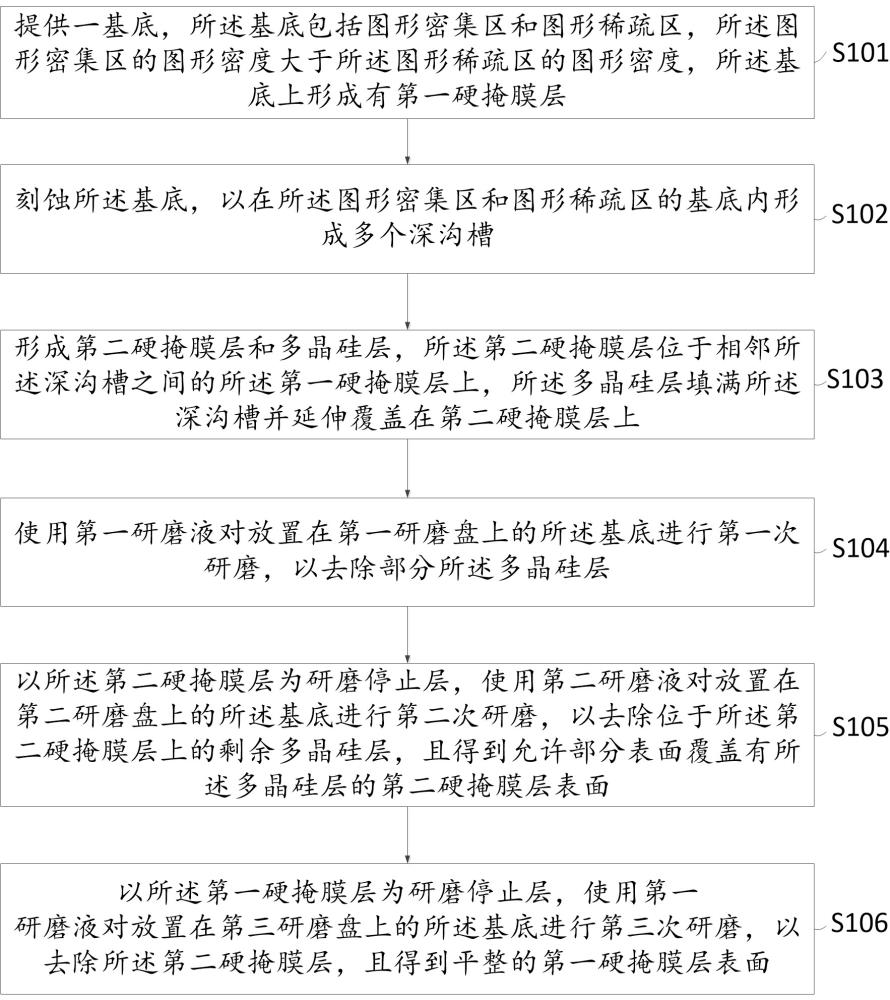

2、为解决上述技术问题,本发明提供一种深沟槽隔离结构的改善方法,至少可包括如下步骤:

3、提供一基底,所述基底包括图形密集区和图形稀疏区,所述图形密集区的图形密度大于所述图形稀疏区的图形密度,所述基底上形成有第一硬掩膜层。

4、刻蚀所述基底,以在所述图形密集区和图形稀疏区的基底内形成多个深沟槽。

5、形成第二硬掩膜层和多晶硅层,所述第二硬掩膜层位于相邻所述深沟槽之间的所述第一硬掩膜层上,所述多晶硅层填满所述深沟槽并延伸覆盖在第二硬掩膜层上。

6、以所述第二硬掩膜层为研磨停止层,使用第二研磨液对放置在第二研磨盘上的所述基底进行第二次研磨,以去除位于所述第二硬掩膜层上的剩余多晶硅层,并同时允许所述第二硬掩膜层的部分表面残留有部分所述多晶硅层,即得到较为平整的第二硬掩膜层表面,所述第二次研磨包括过研磨步骤,该过研磨步骤的研磨时长为:10s~20s。

7、以所述第一硬掩膜层为研磨停止层,使用所述第一研磨液对放置在第三研磨盘上的所述基底进行第三次研磨,以去除所述第二硬掩膜层,且得到平整的第一硬掩膜层表面,所述第三次研磨包括过研磨步骤,该过研磨步骤的研磨时长为:8s~12s;

8、其中,在进行所述研磨时,所述第一研磨盘的压力等于第二研磨盘的压力,且所述第二研磨盘的压力大于所述第三研磨盘的压力。

9、在其中一些可选的示例中,所述第一硬掩膜层的材料包括氮化硅,所述第二硬掩膜层的材料包括氧化硅。

10、在其中一些可选的示例中,所述第一研磨液的材料包括二氧化硅。

11、在其中一些可选的示例中,进行所述第一次研磨时,所述第一研磨盘的压力为:3psi~4psi。

12、在其中一些可选的示例中,所述第二研磨液的材料包括二氧化硅,且所述第二研磨液对所述多晶硅层和所述第二硬掩膜层的研磨选择比为:50~70。

13、在其中一些可选的示例中,进行所述第二次研磨时,所述第二研磨盘的压力为:3psi~4psi。

14、在其中一些可选的示例中,使用所述第一研磨液对放置在第三研磨盘上的所述基底进行第三次研磨时,且所述第一研磨液对所述第二硬掩膜层和所述第一硬掩膜层的研磨选择比为:2~4。

15、在其中一些可选的示例中,进行所述第三次研磨时,所述第三研磨盘的压力为:1.4psi~1.8psi。

16、在其中一些可选的示例中,所述第二次研磨包括研磨主步骤和过研磨步骤,其中所述研磨主步骤中采用与所述第二硬掩膜层适配的第二研磨液对所述多晶硅层进行研磨,并通过终点检测方法完成研磨主步骤,所述过研磨步骤用于在所述研磨主步骤完成后,继续对所述第二硬掩膜层进行研磨去除,以在将所述图形密集区和图形稀疏区内的所述多晶硅层去除的同时允许所述第二硬掩膜层的部分表面残留有部分所述多晶硅层,即得到一个较为平整的第二硬掩膜层界面。

17、在其中一些可选的示例中,所述第三次研磨包括研磨主步骤和过研磨步骤,其中所述研磨主步骤中采用与所述第一硬掩膜层适配的第一研磨液对所述第二硬掩膜层进行研磨,并通过终点检测方法完成研磨主步骤,所述过研磨步骤用于在所述研磨主步骤完成后,继续对所述第一硬掩膜层进行研磨去除,以在将所述图形密集区和图形稀疏区内的所述第二硬掩膜层全部去除的同时得到一个平整的第一硬掩膜层界面。

18、在其中一些可选的示例中,在形成所述第二硬掩膜层的过程中,所述第二硬掩膜层还延伸覆盖在每一所述深沟槽的内表面上。

19、在其中一些可选的示例中,在形成所述第二硬掩膜层的过程中,所述第二硬掩膜层还延伸覆盖在每一所述深沟槽的侧壁上。

20、在其中一些可选的示例中,在所述基底上形成第一硬掩膜层之前,所述制备方法还包括:在所述基底上形成线性氧化硅层的步骤。

21、基于相同的发明构思,本发明还提供了一种深沟槽隔离结构,其具体可采用如上所述的深沟槽隔离结构的改善方法具体制备而成,这里将不再累述。

22、基于相同的构思,本发明还提供了一种半导体工艺,具体可包括如上所述的深沟槽隔离结构的改善方法,但不限于此。

23、基于相同的发明构思,本发明还提供了一种电子设备,具体包括处理器、通信接口、存储器和通信总线,其中,处理器,通信接口,存储器通过通信总线完成相互间的通信。

24、存储器,用于存放计算机程序。

25、处理器,用于执行存储器上所存放的程序时,实现如上所述的深沟槽隔离结构的改善方法步骤。

26、基于相同的发明构思,本发明还提供了一种计算机可读存储介质,所述计算机可读存储介质内存储有计算机程序,所述计算机程序被一处理器执行时实现如上所述的深沟槽隔离结构的改善方法的各个步骤。

27、与现有技术相比,本发明技术方案至少具有如下有益效果之一:

28、本发明提供了一种深沟槽隔离结构的改善方法,先在基底上形成多个深沟槽,以通过不同区域深沟槽的数量不同,将所述基底划分为图形密集区和图形稀疏区,之后在形成填充在该基底上的深沟槽隔离结构的膜层结构,即第一硬掩膜层、第二硬掩膜层和多晶硅层,之后再对所述深沟槽隔离结构的膜层结构进行化学机械研磨工艺,并具体将该化学机械研磨工艺分成三个采用两种研磨液的研磨盘进行,可得到意想不到的效果是:利用第一研磨盘的氧化硅研磨液对基底上沉积的大块多晶硅层进行去除,利用第二研磨盘的多晶硅研磨液对基底上剩余的多晶硅层进行部分去除,并通过终点检测,仅利用较短时长的过研磨步骤即可得到一个部分表面允许残留部分多晶硅层的较为平整的第二硬掩膜层界面,然后再利用第三研磨盘的氧化硅研磨液对基底上的第二硬掩膜层进行全部去除,并再次通过终点检测,仅利用较短时长的过研磨步骤亦可得到一个表面未发生蚀坑或碟形坑缺陷的深沟槽隔离结构,以及在包括图形密集区和图形稀疏区的整个基底上表面平整的第一硬掩膜层界面,即实现了在将多晶硅层和第二硬掩膜层全部去除的同时,减少了过研磨步骤的研磨时长,改善了图形密集区和图形稀疏区之间的硬掩膜层的厚度差,且避免了形成的深沟槽隔离结构表面发生蚀坑或碟形坑缺陷等问题的目的。

- 还没有人留言评论。精彩留言会获得点赞!