碳化硅衬底的位错缺陷的处理方法与流程

本申请涉及把半导体元件加工领域,特别是涉及一种能够转变碳化硅衬底的位错缺陷的类型的处理方法,基于该方法获得的碳化硅衬底,基于该碳化硅衬底制备的碳化硅外延片,以及基于该碳化硅外延片获得的半导体器件。

背景技术:

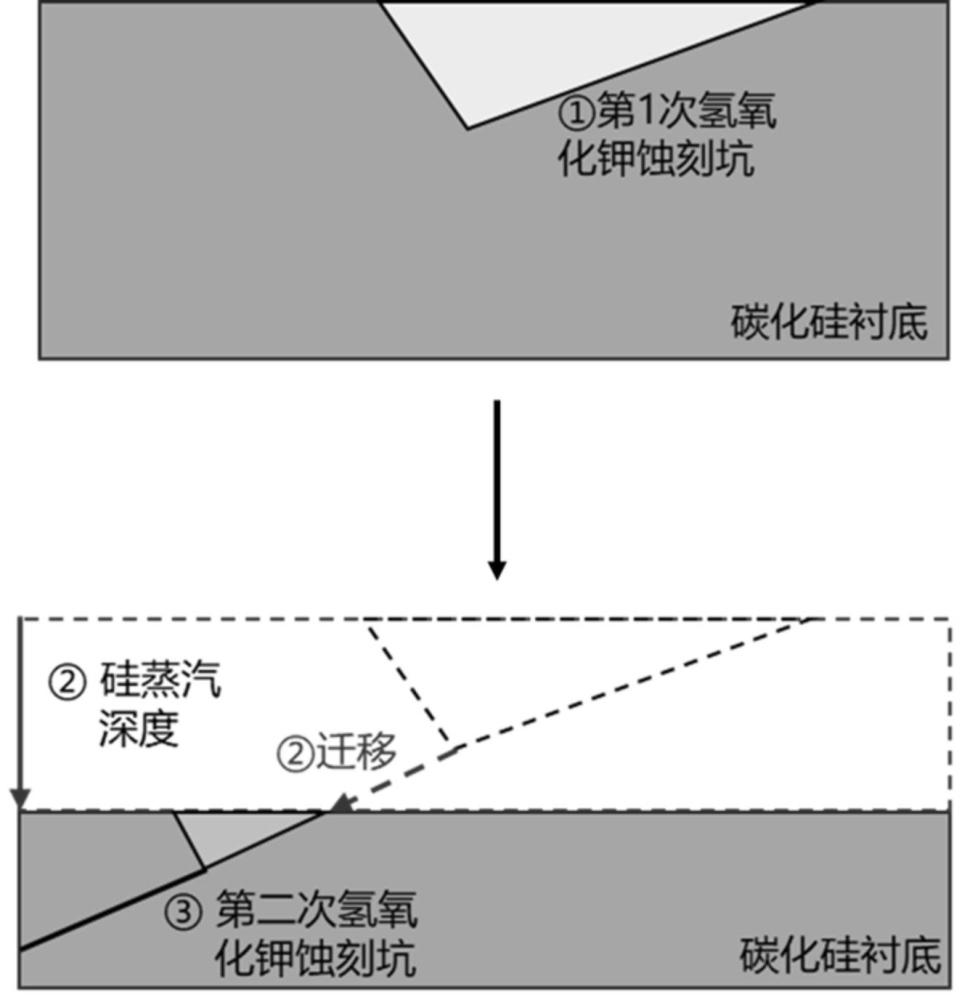

1、碳化硅(sic)是一种宽禁带半导体材料,具有高临界击穿场强、高热导率、高电子饱和漂移速度和大禁带宽度等特点,也有着优异的高温抗氧化性和化学稳定性能。这些优良的物理和电学性能使sic在应用上具有较多优势。在军用和航天领域的高温、高频、大功率电力电子、光电器件方面具有优越的应用价值,极大地扩展了功率器件的能量处理能力,能够满足下一代电力电子装备对功率器件更大功率、更小体积和更恶劣条件下工作的要求。可见,碳化硅材料在诸多领域有着广泛的使用和发展前景。但是碳化硅外延层的位错严重制约着碳化硅器件的制作。碳化硅外延层中的位错大多源于衬底位错,衬底位错主要包括tsd(螺型位错),ted(刃型位错)及bpd(基平面位错)。碳化硅外延的ted和tsd基本不影响最终的碳化硅器件的性能,而bpd会引发器件性能的退化,双极型器件,例如三极管、igbt,对bpd的敏感程度更高,因此降低碳化硅的bpd缺陷从而提高器件制作的可靠性是十分迫切的。

技术实现思路

1、本申请所要解决的技术问题在于,如何实现提升碳化硅衬底的生产良率并降低半导体器件的生产成本。

2、为了解决上述问题,本申请公开了一种碳化硅衬底的位错缺陷的处理方法。所述处理方法能够将影响最终半导体器件性能的位错类型转变为不影响最终半导体器件性能的位错类型,从而提升碳化硅衬底的产品良率,并由此降低整体的半导体器件的生产成本。

3、本申请一方面公开一种碳化硅衬底的位错缺陷的处理方法。所述处理方法可以包括对所述碳化硅衬底进行硅蒸汽刻蚀,以转变所述碳化硅衬底的位错缺陷的类型。

4、在一些可行的实施方式中,所述硅蒸汽刻蚀可以包括:利用第一气体对刻蚀反应空间进行气体置换;向所述刻蚀反应空间内通入硅源,并控制所述刻蚀反应空间内部达到目标反应压力和目标反应温度并维持;对所述碳化硅衬底进行硅蒸汽刻蚀。

5、在一些可行的实施方式中,所述第一气体可以包括惰性气体;或者,所述第一气体可以为氩气。

6、在一些可行的实施方式中,所述目标反应压力可以为10-3pa-20kpa。

7、在一些可行的实施方式中,所述目标反应温度可以为1800℃-2200℃。

8、在一些可行的实施方式中,所述硅蒸汽刻蚀完成后,所述方法还可以包括:利用第二气体调整所述刻蚀反应空间的气体氛围,并控制所述刻蚀反应空间内部达到取片温度;利用第三气体对所述刻蚀反应空间进行气体置换,并控制所述刻蚀反应空间内部达到取片压力;将所述目标碳化硅衬底转移出所述刻蚀反应空间。

9、在一些可行的实施方式中,所述第二气体可以包括氢气,所述第三气体可以包括惰性气体;或者,所述第三气体为氩气。

10、在一些可行的实施方式中,所述取片温度可以由为20℃,所述取片压力可以为1个大气压。

11、在一些可行的实施方式中,所述方法还可以包括对处理过后的碳化硅衬底进行外延生长。

12、本申请另一方面提供一种碳化硅衬底。所述碳化硅衬底经过如上所述的处理方法处理后得到。

13、本申请另一方面提供一种碳化硅外延片。所述碳化硅外延片可以基于如上所述的碳化硅衬底制备。

14、本申请另一方面提供一种半导体器件。所述半导体器件可以基于如上所述的碳化硅外延片制备。

15、本申请所披露的处理方法,能够将影响最终半导体器件性能的位错类型转变为不影响最终半导体器件性能的位错类型,提升产品良率,降低半导体器件的生产成本。

技术特征:

1.一种碳化硅衬底的位错缺陷的处理方法,其特征在于,所述处理方法包括:对所述碳化硅衬底进行硅蒸汽刻蚀,以转变所述碳化硅衬底的位错缺陷的类型。

2.根据权利要求1所述的处理方法,其特征在于,所述硅蒸汽刻蚀,包括:

3.根据权利要求2所述的处理方法,其特征在于,所述第一气体包括惰性气体;或者,所述第一气体为氩气。

4.根据权利要求2所述的处理方法,其特征在于,所述目标反应压力为10-3pa-20kpa。

5.根据权利要求2所述的处理方法,其特征在于,所述目标反应温度为1800℃-2200℃。

6.根据权利要求2所述的处理方法,其特征在于,所述硅蒸汽刻蚀完成后,所述方法还包括:

7.根据权利要求6所述的处理方法,其特征在于,所述第二气体包括氢气,所述第三气体包括惰性气体;或者,所述第三气体为氩气。

8.根据权利要求6所述的处理方法,其特征在于,所述取片温度为20℃,所述取片压力为1个大气压。

9.根据权利要求1所述的处理方法,其特征在于,所述方法还包括:

10.一种碳化硅衬底,所述碳化硅衬底利用如权利要求1-9中任一项所述的处理方法处理后得到。

11.一种碳化硅外延片,所述碳化硅外延片基于如权利要求10所述的碳化硅衬底制备。

12.一种半导体器件,所述半导体器件基于如权利要求11所述的碳化硅外延片制备。

技术总结

本申请公开一种碳化硅衬底的位错缺陷的处理方法。所述处理方法可以包括对所述碳化硅衬底进行硅蒸汽刻蚀,以转变所述碳化硅衬底的位错缺陷的类型。该方法能够将影响最终半导体器件性能的位错类型转变为不影响最终半导体器件性能的位错类型,提升产品良率,降低半导体器件的生产成本。

技术研发人员:柳坤鹏

受保护的技术使用者:希科半导体科技(苏州)有限公司

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!