一种基于4H-SiC衬底的高性能CMOS器件

本发明涉及半导体器件,特别涉及一种基于4h-sic衬底的高性能cmos器件。

背景技术:

1、cmos(互补金属氧化物半导体)是现阶段大规模集成电路的主流工艺技术,具有功耗低、电源电压低、速度快、抗干扰能力强、集成度高等众多优点,因此cmos器件被广泛应用于温度传感器、图像传感器和射频功率放大器等诸多领域。现阶段,随着高精尖技术产业飞速发展,一些基础性行业如冶金化工、石油勘探需要在高温环境中进行,对电子设备性能提出了更高的要求,所以能在高温下保持稳定的电子器件尤为重要。除此以外,硅芯片工艺自问世以来,晶体管沟道随着器件尺寸的不断缩小也在不断缩短。然而,当沟道缩短到一定程度之后,量子隧穿极易发生,因此需要合适的结构提供更小泄露电流。

技术实现思路

1、本发明要解决的技术问题是提供一种基于4h-sic衬底的高性能cmos器件,通过在同一4h-sic衬底上制备出耐高温高性能cmos器件,且该器件是通过利用finfet结构提供更小的泄露电流和更小的栅极延迟以及更大的电流驱动能力。

2、为了解决上述技术问题,本发明的技术方案为:

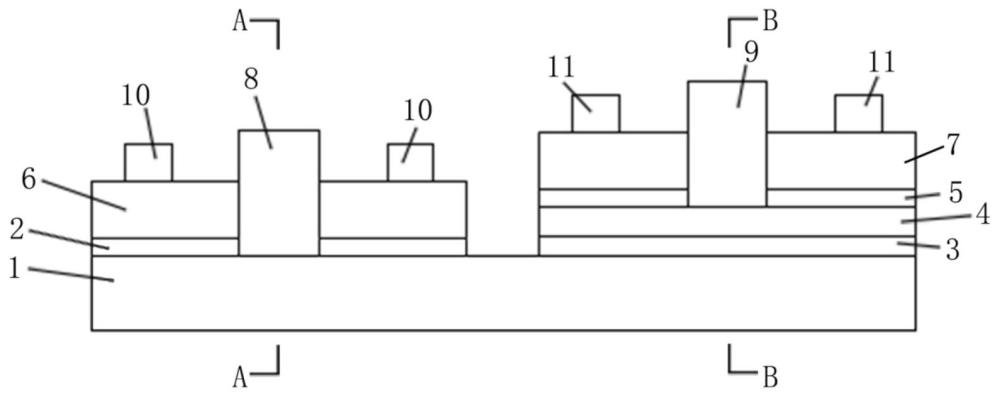

3、第一方面,本发明提供一种基于4h-sic衬底的高性能cmos器件,包括4h-sic衬底1、nmos沟道、pmos外延层、pmos沟道、nmos欧姆电极10和pmos欧姆电极11,4h-sic衬底1与nmos沟道和pmos外延层相连接,pmos外延层上方设有pmos沟道,nmos沟道上方设有nmos肖特基栅电极8,pmos沟道上方设有pmos肖特基栅电极9,nmos沟道的顶部两侧设有nmos欧姆电极10,pmos沟道的顶部两侧设有pmos欧姆电极11;所述nmos沟道包括nmos鳍片2和nmos隔离层6,nmos隔离层6设置在nmos鳍片2顶部;所述pmos沟道包括pmos鳍片5和pmos隔离层7,pmos隔离层7设置在pmos鳍片5顶部;所述pmos外延层包括外延层一3和外延层二4,外延层二4设置在外延层一3顶面。

4、优选的,所述nmos鳍片2包括2个鳍片,所述pmos鳍片5包括2个鳍片,所述nmos肖特基栅电极8和pmos肖特基栅电极9为鳍状结构。

5、优选的,所述nmos鳍片2的鳍片和所述pmos鳍片5的鳍片顶部为圆角状,所述nmos鳍片2的鳍片和所述pmos鳍片5的鳍片厚度为10-50nm,所述nmos鳍片2的鳍片和所述pmos鳍片5的鳍片高度为100-200nm。

6、优选的,所述nmos鳍片2和pmos鳍片5的鳍片厚度为30nm,所述nmos鳍片2的鳍片和所述pmos鳍片5的鳍片高度为150nm。

7、优选的,所述外延层一3和所述外延层二4为非掺杂半导体,外延层一3的厚度为100-300nm,外延层二4的厚度为200-500nm。

8、优选的,所述外延层一3的厚度为200nm,所述外延层二4的厚度为300nm。

9、优选的,所述外延层一3的材料为gan,所述外延层二4的材料为gan或algan中的任意一种。

10、优选的,所述外延层一3的离子掺杂浓度为1×1018-1×1020cm-3。

11、优选的,所述nmos隔离层6和所述pmos隔离层7的厚度为10-50nm。

12、优选的,所述nmos隔离层6和所述pmos隔离层7的厚度为20nm。

13、优选的,所述nmos隔离层6和所述pmos隔离层7的材料为sio2、si3n4中的任意一种或sio2、si3n4的组合。

14、优选的,所述nmos鳍片2的材料为4h-sic或sic中的任意一种,所述pmos鳍片5的材料为algan,所述nmos肖特基栅电极8的材料为ni金属或ni-ti-au金属叠层中的任意一种,所述pmos肖特基栅电极9的材料为ni-au金属叠层、pt-au金属叠层中的任意一种,所述nmos欧姆电极10的材料为ti-al-ni-au金属叠层,所述pmos欧姆电极11的材料为ni金属。

15、更优选的,所述pmos鳍片5的离子掺杂浓度为1×1016-1×1017cm-3。

16、更优选的,所述ni-ti-au金属叠层为自底端面至顶端面依次为ni、ti、au的金属叠层,所述ni-au金属叠层为自底端面至顶端面依次为ni、au的金属叠层。

17、第二方面,本发明提供一种基于4h-sic衬底的高性能cmos器件的制备方法,包括以下步骤:

18、1、采用热氧化法沉积在4h-sic衬底上生长nmos鳍片层和外延层一、外延层二和pmos鳍片层;

19、2、采用光刻显影法和干法刻蚀法,实现nmos鳍片层与外延层一、外延层二、pmos鳍片层的电隔离;

20、3、对nmos鳍片层采用干法刻蚀得到nmos鳍片,在高温氢气氛围中退火;

21、4、对pmos鳍片层采用干法刻蚀得到pmos鳍片,在高温氢气氛围中退火;

22、5、在nmos鳍片上方氧化沉积nmos隔离层,退火,得到nmos沟道;

23、6、在pmos鳍片上方氧化沉积pmos隔离层,退火,得到pmos沟道;

24、7、采用氧化沉积法或电子束蒸发法,在nmos沟道上方形成nmos肖特基栅电极,在pmos沟道上方形成pmos肖特基栅电极;

25、8、采用电子束蒸发法或磁控溅射法在nmos沟道上方的两侧形成nmos欧姆电极,pmos沟道上方的两侧形成pmos欧姆电极,得到一种基于4h-sic衬底的高性能cmos器件。

26、优选的,步骤4中,高温的温度为1100℃-1200℃。

27、优选的,步骤5中,高温的温度为1100℃-1200℃。

28、采用上述技术方案,具有以下的有益效果:

29、(1)本发明提供一种基于4h-sic衬底的高性能cmos器件,采用了finfet结构,不仅抑制短沟道效应,提升载流子迁移率,栅控能力更强,具有更广阔的应用领域;

30、(2)本发明提供一种基于4h-sic衬底的高性能cmos器件,采用具有较大禁带宽度的4h-sic材料作为衬底,并且由于4h-sic具有较高的热导率可以散热,因此可以缓解cmos器件的散热压力,使得4h-sic衬底的cmos器件具有了在高温下稳定工作的能力;

31、(3)本发明提供一种基于4h-sic衬底的高性能cmos器件,nmos鳍片和pmos鳍片的鳍片顶部为圆角状,有利于器件提升器件的亚阈值性能。

技术特征:

1.一种基于4h-sic衬底的高性能cmos器件,其特征在于,包括4h-sic衬底(1)、nmos沟道、pmos外延层、pmos沟道、nmos欧姆电极(10)和pmos欧姆电极(11),4h-sic衬底(1)与nmos沟道和pmos外延层相连接,pmos外延层上方设有pmos沟道,nmos沟道上方设有nmos肖特基栅电极(8),pmos沟道上方设有pmos肖特基栅电极(9),nmos沟道的顶部两侧设有nmos欧姆电极(10),pmos沟道的顶部两侧设有pmos欧姆电极(11);

2.根据权利要求1所述的基于4h-sic衬底的高性能cmos器件,其特征在于,所述nmos鳍片(2)包括2个鳍片,所述pmos鳍片(5)包括2个鳍片,所述nmos肖特基栅电极(8)和所述pmos肖特基栅电极(9)为鳍状结构。

3.根据权利要求2所述的基于4h-sic衬底的高性能cmos器件,其特征在于,所述nmos鳍片(2)的鳍片和所述pmos鳍片(5)的鳍片顶部为圆角状,所述nmos鳍片(2)的鳍片和所述pmos鳍片(5)的鳍片厚度为10-50nm,所述nmos鳍片(2)的鳍片和所述pmos鳍片(5)的鳍片高度为100-200nm。

4.根据权利要求3所述的基于4h-sic衬底的高性能cmos器件,其特征在于,所述nmos鳍片(2)和所述pmos鳍片(5)的鳍片厚度为30nm,所述nmos鳍片(2)的鳍片和所述pmos鳍片(5)的鳍片高度为150nm。

5.根据权利要求1~4任意一项所述的基于4h-sic衬底的高性能cmos器件,其特征在于,所述外延层一(3)和所述外延层二(4)为非掺杂半导体,所述外延层一(3)的厚度为100-300nm,所述外延层二(4)的厚度为200-500nm。

6.根据权利要求5所述的基于4h-sic衬底的高性能cmos器件,其特征在于,所述外延层一(3)的厚度为200nm,所述外延层二(4)的厚度为300nm。

7.根据权利要求5所述的基于4h-sic衬底的高性能cmos器件,其特征在于,所述外延层一(3)的材料为gan,所述外延层二(4)的材料为gan或algan中的任意一种。

8.根据权利要求5所述的基于4h-sic衬底的高性能cmos器件,其特征在于,所述nmos隔离层(6)和所述pmos隔离层(7)的厚度为10-50nm。

9.根据权利要求1所述的基于4h-sic衬底的高性能cmos器件,其特征在于,所述nmos鳍片(2)的材料为4h-sic或sic中的任意一种,所述pmos鳍片(5)的材料为gan,所述nmos隔离层(6)和所述pmos隔离层(7)的材料为sio2、si3n4中的任意一种或sio2、si3n4的组合,所述nmos肖特基栅电极(8)的材料为ni金属或ni-ti-au金属叠层中的任意一种,所述pmos肖特基栅电极(9)的材料为ni-au金属叠层、pt-au金属叠层中的任意一种,所述nmos欧姆电极(10)的材料为ti-al-ni-au金属叠层,所述pmos欧姆电极(11)的材料为ni金属。

10.一种根据权利要求1~9任意一项所述的基于4h-sic衬底的高性能cmos器件的制备方法,其特征在于,包括以下步骤:

技术总结

本发明涉及半导体器件技术领域,具体公开了一种基于4H‑SiC衬底的高性能CMOS器件,包括4H‑SiC衬底、NMOS沟道、PMOS外延层、PMOS沟道、NMOS欧姆电极和PMOS欧姆电极,本发明的基于4H‑SiC衬底的高性能CMOS器件,以具有较高热导率的4H‑SiC作为衬底,同时采用具有圆角状鳍片的FinFET结构,一方面可以缓解器件的散热压力,使其可以在高温下稳定工作,另一方面抑制短沟道效应,提升载流子迁移率,栅控能力更强,具有更广阔的应用领域。

技术研发人员:李彦庆,孙守红,余毅,何锋赟

受保护的技术使用者:中国科学院长春光学精密机械与物理研究所

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!