具有低功率部件的线路放电电路的制作方法

具有低功率部件的线路放电电路

1.相关专利申请

2.本专利申请要求2019年2月15日提交的美国临时专利申请号62/806,663的优先权,该申请的内容据此全文并入。

技术领域

3.本公开涉及在电子设备中提供功率,并且更具体地讲,涉及具有低功率部件的线路放电电路(line discharge circuit)。

背景技术:

4.许多电子设备使用电源。此类电源可位于电子设备的外部或内部。电源可包括稳压器。稳压器可被配置为生成恒定输出电压。该输出电压可以是直流(dc)电压。可使用输入电压来生成该输出电压。稳压器可被配置为,即使输入电压或附接到稳压器的负载发生变化,也尝试保持恒定输出电压。如果输出电压小于输入电压,则稳压器可以说是作为降压转换器实现或在降压模式下运行。如果输出电压大于输入电压,则稳压器可以说是作为升压转换器实现或在升压模式下运行。稳压器可被实现为升降压转换器,其中该稳压器可在降压模式、升压模式下运行,或者在其中降压部件和升压部件两者均处于运行中的升降压模式下运行。

5.电容可形成在电源的输入端或输出端上。一些解决方案可通过线性解决方案(诸如恒流放电或电阻器放电)来耗散该电容中积聚的电荷。然而,此类解决方案会产生大量热能,从而需要额外的热耗散解决方案来处理由经耗散的电容所产生的热能。其他解决方案可包括复原式解决方案,其中使累积在输出电容中的电荷放电的电流从输出电容被引导至输入电容,或反之亦然。然而,由于基于电容的输入电压可能存在较大变化,此类解决方案是比较复杂的。再其他的解决方案可包括损耗切换(loss switching),其中可接通和关断升降压稳压器的低侧输出开关以耗散累积在输出电容中的电荷。然而,此类解决方案可能需要非常低的频率以允许稳压器的电感器在不变得饱和的情况下充电和放电。

6.如上所述,本公开的实施方案克服了使稳压器的输入和/或输出电容中累积的电荷放电的其他解决方案的各种缺点。本公开的实施方案可包括功率调节器,该功率调节器减小管芯上耗散功率所需的面积。本公开的实施方案可避免对紧密耦接的热保护的需求。本公开的实施方案可避免输入电压的显著增加,在不使电感器饱和的情况下进行操作。本公开的实施方案可在不需要位于实现功率调节器的半导体器件上的附加引脚的情况下操作。

技术实现要素:

7.本公开的实施方案包括一种控制电路。该控制电路可包括放电电路。该放电电路可由模拟和数字电路的任何合适的组合来实现。该控制电路可包括控制逻辑部件。该控制电路可通过模拟电路、数字电路或由处理器执行的指令的任何合适的组合来实现。该控制

电路可包括第一输出端,该第一输出端通信地耦接到第一功率晶体管的控制端子。该第一功率晶体管可包括该控制端子、第一端子和第二端子。该第一功率晶体管可由任何合适的晶体管实现。该控制电路还可包括输入端,该输入端通信地耦接到该第一功率晶体管的该第二端子。该控制逻辑部件被配置为在放电操作模式下,经由该第一输出端向该第一功率晶体管的该控制端子提供第一控制端子电压。该第一控制端子电压可被配置为在线性运行区域中运行该第一功率晶体管以耗散存储在连接至该第一功率晶体管的该第一端子的第一电容中的能量。该放电电路可被配置为在放电操作模式下,从该第一功率晶体管的该第二端子接收放电电流,并且耗散未被该第一功率晶体管耗散的剩余能量。

8.结合上述实施方案中的任一个实施方案,该第一功率晶体管可位于包括该控制电路的管芯的外部。

9.结合上述实施方案中的任一个实施方案,该第一功率晶体管的该第二端子可以是该第一功率晶体管的源极。

10.结合上述实施方案中的任一个实施方案,该放电电路可被配置为耗散比该第一功率晶体管被配置为在运行期间在该线性区域中耗散的能量少的能量。

11.结合上述实施方案中的任一个实施方案,该放电电路可包括电流源和一对晶体管,该一对晶体管被配置为对参考电流进行镜像以耗散该剩余能量。该电流源可通过开关连接至该对晶体管。该开关可由来自该控制逻辑部件的放电信号驱动。该对晶体管可包括第三晶体管和第四晶体管。该第三晶体管可包括第一端子和连接至该电流源的控制端子,以及接地的第三端子。该第四晶体管可包括连接至该放电电路的输入端的第一端子、连接至该电流源的控制端子以及接地的第二端子。

12.结合上述实施方案中的任一个实施方案,该放电电路可包括被配置为耗散剩余能量的电阻器。该电阻器可连接至该放电电路的输入端。该电阻器可通过开关连接至该放电电路的输入端。该开关可由来自该控制逻辑部件的放电信号驱动。

13.结合上述实施方案中的任一个实施方案,该控制电路可包括通信地耦接到第二功率晶体管的控制端子的第二输出端,该第二功率晶体管包括控制端子、第一端子和第二端子。

14.该输入端还可通过电感器通信地耦接到该第二功率晶体管的该第二端子。

15.该控制逻辑部件还可被配置为在放电操作模式下,向该第二功率晶体管的该控制端子提供第二控制端子电压,该第二控制端子电压被配置为在该线性运行区域中运行该第二功率晶体管以耗散存储在连接至该第二功率晶体管的第一端子的第二电容中的能量。所接收的放电电流可包括来自该第一功率晶体管的输出端和来自该第二功率晶体管的输出端的分量,该放电电路还可被配置为耗散未被该第二功率晶体管耗散的剩余能量。

16.结合上述实施方案中的任一个实施方案,该控制电路可包括电压源。该控制端子电压可由该控制逻辑部件提供为源自该电压源。该电压源可以是与提供待由该控制电路转换或调节的电压的电压源不同的单独的电压源。在另一个实施方案中,该控制电路可包括两个单独的此类电压源,其中不同的电压源用于为该第一功率晶体管和第二功率晶体管施加单独的控制端子电压。

17.结合上述实施方案中的任一项实施方案,该控制电路可包括在系统中。该系统可以是例如微控制器、功率调节器、稳压器、电压源、电压控制器、计算机、移动设备、平板电脑

或任何其他合适的电子设备。该系统可包括电压源或可通信地耦接到电压源。该控制电路可包括在该系统内的功率调节器电路中。该功率调节器可被配置为输出指定电压并且保持该指定电压。该第一功率晶体管可以是连接至该功率调节器的电压输出的输出晶体管,或者可以是连接至该功率调节器的该电压源的输入晶体管。该输出电压可被提供给该系统的各个部分,诸如微控制器上的外围设备、系统外部、或提供给任何合适的负载。该电容可以是由与该功率调节器的输入电压或输出电压并联连接的电容器实现的输入电容或输出电容。

18.结合上述实施方案中的任一个实施方案,该控制电路可连接至第五功率晶体管和第六功率晶体管。该控制电路的输出端可连接至该第五功率晶体管和第六功率晶体管的控制端子。第五功率晶体管的第一端子可连接至待调节的输入电压。该第五功率晶体管的第一端子可连接至已调节的输出电压。该第五功率晶体管和第六功率晶体管的第二端子可连接在一起并且连接至该控制电路的输入端。

附图说明

19.图1是根据本公开的实施方案的系统的图示,该系统被配置为使用具有低功率部件的线路放电电路来提供功率调节。

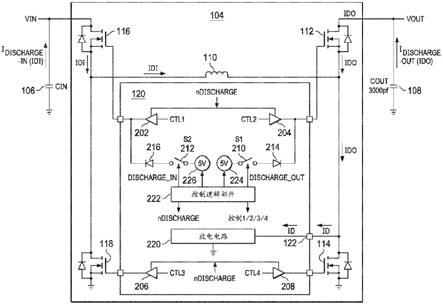

20.图2是根据本公开的实施方案的系统的更详细的图示,该系统被配置为使用具有低功率部件的线路放电电路来提供功率调节。

21.图3是根据本公开实施方案的放电电路的具体实施的图示。

22.图4是根据本公开的实施方案的另一个放电电路的具体实施的图示。

23.图5是根据本公开的实施方案的另一个系统的图示,该系统被配置为使用具有低功率部件的线路放电电路来提供功率调节。

24.图6是根据本公开的实施方案的方法的图示,该方法使用具有低功率部件的线路放电电路来提供功率调节。

具体实施方式

25.图1是根据本公开的实施方案的系统100的图示,该系统被配置为使用具有低功率部件的线路放电电路来提供功率调节。系统100可实现为例如微控制器、移动设备、计算机、服务器或任何其他合适的电子设备或在例如微控制器、移动设备、计算机、服务器或任何其他合适的电子设备中实现。系统100可被配置为从源(诸如v源102)向各种外围设备106提供功率。v源102可包括(例如)直流电压源。v源102的电压可以是固定的或可编程的。外围设备106可由需要电源的任何合适的电路、电子设备或子系统来实现。给定外围设备106所需的电压可与可从v源102获得的电压不同。因此,系统100可包括功率调节器104,该功率调节器被配置为将来自v源102的在该功率调节器的输入端处的电压电平vin转换为该功率调节器的输出端处的不同的电压电平vout。可将来自vout的电压提供给外围设备106。可由系统100的任何合适的电源或任何其他合适的部分提供vin。

26.稳压器104可被配置为使连接至该稳压器的输入电容或输出电容放电。稳压器104可包括线路放电电路,该线路放电电路被配置为使与其连接的输入电容或输出电容放电。放电电路可在稳压器104的硅树脂或管芯内实现。稳压器104可实现(例如)四开关升降压功

率控制器或调节器、通用串行总线(usb)功率控制器、另外的usb应用程序或开关模式电源(smps)。

27.稳压器104可被实现为升降压转换器,并且可被配置为提供高于或低于vin的vout,这取决于外围设备106的需要。稳压器104可包括电感器110、高侧输出晶体管112、低侧输出晶体管114、高侧输入晶体管116和低侧输入晶体管118。晶体管112、114、116、118可被实现为例如n沟道功率金属氧化物半导体场效应晶体管(mosfet)、n沟道垂直mosfet、双极型晶体管(bjt)或任何其他合适的晶体管或器件。在一个实施方案中,稳压器104可包括控制电路120。

28.高侧输出晶体管112的漏极或第一端子可连接至vout,高侧输出晶体管112的源极或第二端子可连接至低侧输出晶体管114的漏极、连接至电感器110的第一侧并且连接至控制电路120的输入端122。高侧输出晶体管112的栅极(或控制端子)可连接至控制电路120的相应的输出端。低侧输出晶体管114的源极可接地,并且低侧输出晶体管114的栅极(或控制端子)可连接至控制电路120的相应的输出端。高侧输入晶体管116的漏极或第一端子可连接至vout,高侧输入晶体管116的源极或第二端子可连接至低侧输入晶体管118的漏极和电感器110的第二侧,并且高侧输入晶体管116的栅极(或控制端子)可连接至控制电路120。低侧输入晶体管118的源极可接地,并且低侧输入晶体管118的栅极(或控制端子)可连接至控制电路120的相应的输出端。在一个实施方案中,高侧输入晶体管116的源极或第二端子可连接至控制电路120的另一个输入端124。

29.系统100可包括连接在功率调节器104的vin与地之间的输入电容cin 106。在一个实施方案中,cin 106可被包括在功率调节器104内。在另一个实施方案中,cin 106可在功率调节器104外部实现。系统100可包括连接在功率调节器104的vout与地之间的输出电容cout 108。在一个实施方案中,cout 108可被包括在功率调节器104内。在另一个实施方案中,cout 108可在功率调节器104外部实现。

30.在一个实施方案中,功率调节器104可被配置为耗散cin 106中的功率或电荷。在另一个实施方案中,功率调节器104可被配置为耗散cout108中的功率或电荷。尽管被示出为单个实体,但功率调节器104可以单个实体或多于一个实体实现,以单独地或组合地耗散cin 106和cout 108中的功率或电荷。

31.由于其他解决方案可能需要额外的功率元件(诸如可能耗散较大功率的电阻器或专用晶体管),与其他解决方案相比,功率调节器104可被配置为减小功率耗散所需的较大面积。此类附加功率元件需要半导体管芯上用于功率调节器104的空间才能实现,并且可能需要附加的热量耗散元件或热量消减元件。此外,与其他解决方案相比,功率调节器104可被配置为在不显著增加输入电压或不存在使电感器110饱和的风险的情况下耗散功率。此外,与其他解决方案相比,功率调节器104可被配置为在没有额外引脚的情况下耗散功率。例如,在其他解决方案中,其中要耗散功率的电阻器或专用晶体管可能不被包括在功率调节器104内,但可从外部连接至功率调节器104。

32.在一个实施方案中,控制电路120可被配置为操作功率调节器104以耗散功率调节器104的高侧晶体管(诸如高侧晶体管112、116)中的功率。控制电路120可被配置为操作功率调节器104以耗散来自高侧输出晶体管112中cout 108的功率。此外,控制电路120可被配置为操作功率调节器104以耗散来自高侧输入晶体管116中cin 106的功率。由于控制电路

120被配置为使存在于功率调节器104的输入线路或输出线路上的电容放电,因此控制电路120可以是线路放电电路。控制电路120可被配置为通过将高侧晶体管112、116的相应的栅极(或控制端子)连接至合适的低电压源来使电容耗尽功率。连接至高侧晶体管112、116的相应的栅极(或控制端子)的低电压源可导致从连接至高侧晶体管112、116的相应漏极或第一端子的电容汲取电流。相应的电流可流动穿过高侧晶体管112、116中的相应的一个高侧晶体管的沟道以放电。因此,大部分待耗散的能量在高侧晶体管112、116中耗散,而能量的剩余部分则在控制电路120中通过输入端122或输入端124耗散。

33.在一个实施方案中,来自cin 106的能量可以在高侧晶体管116中耗散,而能量的剩余部分则在通过电感器110之后,在控制电路120中通过输入端122耗散。在另一个实施方案中,来自cin 106的能量可在高侧晶体管116中耗散,而能量的剩余部分则在控制电路120中通过输入端124耗散。

34.在一个实施方案中,来自cout 108的能量可在高侧晶体管112中耗散,而能量的剩余部分则在通过电感器110之后在控制电路120中通过输入端124耗散。在另一个实施方案中,来自cout 108的能量可在高侧晶体管112中耗散,而能量的剩余部分则在控制电路120中通过输入端122耗散。

35.尽管在上文中晶体管112、114、116、118被论述为由n沟道功率mosfet实现,但晶体管112、114、116、118可由任何合适的晶体管实现。当晶体管112、114、116、118由其他类型的晶体管实现时,到例如漏极引脚的给定连接可替代地为到源极引脚。在不脱离本公开的范围和教导内容的情况下晶体管112、114、116、118的其他具体实施可为图1中的元件的特定布置带来其他改变。

36.功率调节器104的示例性具体实施在以下图2至图4的上下文中示出。

37.图2是根据本公开的实施方案的系统100的更详细图示。具体地,图2中示出了系统100的控制电路120的进一步细节和放电操作模式期间的电流流动。放电模式可包括其中使cin 106或cout 108放电的操作。系统100可在任何合适的时间或根据任何合适的标准进入放电模式。cout 108的放电可在功率调节器104的功率传送停止时开始。功率调节器104的功率传送可自动停止或通过外部控制器停止。cin 106的放电可在v源102不再可用时(诸如在由usb供电的系统中在断开之后)开始。在放电模式中,可使cin 106、cout 108或两者放电。即使cin 106和cout 108都要放电,也可使这两者单独地放电。在这种情况下,cin 106和cout 108可以任何合适的顺序单独地放电。

38.可以任何合适的方式生成用于控制电路120的控制信号。在一个实施方案中,控制电路120可包括控制逻辑部件222以生成控制信号。控制逻辑部件222可被配置为基于任何合适的标准生成控制信号。控制逻辑部件222可以任何合适的方式诸如由模拟电路、数字电路、用于由处理器执行的指令或它们的任何组合来实现。控制逻辑部件222可被配置为生成控制信号,诸如ctl1、ctl2、ctl3、ctl4、discharge(未示出)、ndischarge、discharge_out和discharge_in。

39.控制电路120可包括分别连接至晶体管116、112、118、114的栅极(或控制端子)的驱动器202、204、206、208。驱动器202、204、206、208可分别由各自由控制逻辑部件222生成的控制信号ctl1、ctl2、ctl3、ctl4驱动。ctl1、ctl2、ctl3、ctl4可在功率调节器104的正常(非放电)模式或操作期间被启用以交替地激活(或闭合)和去激活(或打开)晶体管116、

112、118、114以提供连续vout。在放电操作模式期间,可将驱动器202、204、206、208关闭、使其不可操作或以其他方式被忽略。控制电路120可包括用于使由驱动器202、204、206、208生成的控制信号被关断、无法操作或以其他方式被忽略的任何合适的机构。例如,控制电路120可包括控制信号ndischarge,其可为discharge控制信号的逻辑逆反(如上所述,discharge未在图2中示出)。当逻辑高或连通时,discharge控制信号可指定控制电路120将在放电操作模式下运行作以使cout 108或cin 106耗尽功率。当逻辑低或关断时,discharge控制信号可指定控制电路120将在正常操作模式下运行以控制晶体管116、112、118、114提供vout。因此,当逻辑高或接通时,ndischarge控制信号可用于启用、供电或以其他方式允许驱动器202、204、206、208向晶体管116、112、118、114发出控制信号。此外,当控制电路120将进入放电操作模式时,ndischarge控制信号可为逻辑低或关断,并且禁用驱动器202、204、206、208。

40.在放电操作模式期间,低侧晶体管118、114可响应于ndischarge控制信号的关断状态而关断。然而,在放电操作模式期间,高侧晶体管116、112可处于各种操作状态,这取决于由控制电路120提供的控制信号。控制电路120可被配置为在放电操作模式期间发出控制信号以控制高侧晶体管116、112的栅极(或控制端子)。控制电路120可包括任何合适数量和种类的元件,以便控制高侧晶体管116、112的栅极。

41.例如,控制电路120可包括第一电压源224。第一电压源224可被配置为生成逻辑高信号。此类逻辑高信号可为例如五伏。由第一电压源224生成的信号可以是最初生成的并且在通过二极管(诸如二极管214)之后的逻辑高信号。在一个实施方案中,控制电路120可包括电压源(诸如第一电压源224)的单个实例,该电压源被配置为向高侧晶体管112、116两者提供栅极(或控制端子)电压。在另一个实施方案中,如图2所示,控制电路120可包括第二电压源226。第二电压源226可被配置为生成逻辑高信号。此类逻辑高信号可为例如五伏。由电压源224生成的信号可以是最初生成的并且在通过二极管(诸如二极管216)之后的逻辑高信号。在此类实施方案中,第一电压源224可被配置为向高侧输出晶体管112提供栅极(或控制端子)电压,并且第二电压源226可被配置为向高侧输入晶体管116提供栅极(或控制端子)电压。第一电压源224和第二电压源226的电压可相同或不同,并且可独立地由控制逻辑部件222控制。

42.控制电路120可包括第二电压源226与高侧输入晶体管116的栅极(或控制端子)之间的开关s2 212,其中当开关s2 212闭合时,电压源226与高侧输入晶体管116的栅极(或控制端子)之间的连接通过二极管216。开关s2 212可由控制信号discharge_in控制。当cin 106将在给定放电模式下放电时,可由控制逻辑部件222启用discharge_in。控制电路120可包括第一电压源224与高侧输出晶体管112的栅极(或控制端子)之间的开关s1 210,其中当开关s1 210闭合时,电压源224与高侧输出晶体管112的栅极(或控制端子)之间的连接通过二极管214。开关s1210可由控制信号discharge_out控制。当cout 108将以给定放电模式放电时,可由控制逻辑部件222启用discharge_out。当discharge_in被启用或逻辑高时,开关s2 212可被启用,并且因此将电压从第二电压源226通过二极管216引导至高侧输入晶体管116的栅极(或控制端子)。当discharge_out被启用或逻辑高时,开关s1 210可被启用,并且因此将电压从第一电压源224通过二极管214引导至高侧输出晶体管112的栅极(或控制端子)。在放电模式期间,当通过施加来自第二电压源226的电压来启用高侧输入晶体管116

时,可使电容器cin106放电。在放电模式期间,当通过施加来自第一电压源224的电压来启用高侧输入晶体管112时,可使电容器cout 108放电。

43.控制电路120可使用任何合适的一种或多种放电模式。在一个实施方案中,可使cin 106在第一放电模式期间放电。在另一个实施方案中,可使cout 108在第二放电模式期间放电。在另一个实施方案中,可使cin106和cout 108两者在第三放电模式期间放电。

44.在cout 108的放电期间,电流可从cout 108的顶板流入高侧输出晶体管112的漏极或第一端子。该放电电流可表示为ido。ido可通过输入端122引导至包含在控制电路120内的放电电路220中。在cin 106放电期间,电流可以从cin 106的顶板流入高侧输入晶体管116的漏极或第一端子。该放电电流可表示为idi。idi可通过电感器110然后通过输入端122引导至放电电路220中。通过输入端122引导至放电电路220中的电流被示为id。如果由控制电路120使用的放电模式是仅使cout 108放电,则id可以等于ido。如果控制电路120使用的放电模式是仅使cin 106放电,则id可以等于idi。如果控制电路120使用的放电模式是使cin 106和cout 108放电,则id可以等于idi和ido的总和。另选地,通过电路的对称性,放电电路220可仅连接至高侧输入晶体管116的源极。然后,cout 108的放电电流ido随后可流动穿过晶体管112、电感器110进入放电电路220。

45.在放电模式期间,相对大量的能量可在高侧晶体管112、116中耗散。可根据高侧晶体管112、116中的每个相应的高侧晶体管的漏极(或第一端子)和源极(或第二端子)处的预期电压来选择待施加到高侧晶体管112、116的栅极的电压。具体地讲,要将电压选择为使得高侧晶体管112、116在线性运行区域内运行。线性区域内的运行可耗散在高侧晶体管112、116上的大量放电能量。线性运行区域的具体范围可取决于用于实现高侧晶体管112、116的晶体管的具体类型和型号。因此,要被选择为使得高侧晶体管112、116在线性运行区域内运行的电压可取决于用于实现高侧晶体管112、116的晶体管的特定类型和型号。为了提供待施加到高侧晶体管112、116的栅极的此类电压,可使用任何合适的机制。例如,电压源224、226可以是5v,其可以由一个或多个二极管(诸如二极管214、216)进一步衰减,使得待施加到高侧晶体管112、116的特定栅极(或控制端子)电压将导致高侧晶体管112、116根据其漏极电压和源极电压在线性运行区域内运行。

46.在相应的放电模式期间将由高侧晶体管112、116耗散的能量与将由放电电路220耗散的能量的量相比可以是较大的。通过利用高侧晶体管112、116耗散来自电容器cout 108、cin 106的大量能量,可使用更少的部件来实现放电电路220。放电电路220可以任何合适的方式并且通过任何合适数量、种类的部件和合适的部件组合来实现。放电电路220的示例性非限制性具体实施在图3和图4中示出。可以任何固定或可调节的具体实施来实现放电电路220。

47.然而,与其他解决方案相比,可用相对较少的部件实现放电电路220。具体地讲,可利用将不会在功率调节器104或控制电路120内生成过多热量的耗散元件来实现放电电路220。与现有技术解决方案相比,这可能是有利的;现有技术解决方案可能需要添加具有高硅面积、额外的散热、额外的热保护的线路电容放电块(line capacitance discharge block),或其他同样会增加设备成本和尺寸的元件。

48.例如,在图2中,vout可以是20v。cout 108可以是3000pf。在cout 108的放电模式期间,ido可以是110ma。因此,待耗散的电压可为2.2w。通过在高侧输出晶体管112的线性运

行区域中对其进行操作,高侧输出晶体管112可被配置为耗散1.925w。因此,高侧输出晶体管112的源极处的电压和输入端122处的电压可为2.5v。因此,放电电路220可能仅需要耗散275mw。因此,放电电路220可被配置为耗散比在高侧输出晶体管112的线性操作期间高侧输出晶体管112少的能量。施加到高侧输出晶体管112的栅极(或控制端子)电压可以是第一电压源224的电压,5v,减去在二极管214上的电压降,0.7v,从而导致4.3v施加到高侧输出晶体管112的栅极(或控制端子)。栅极(或控制端子)电压为4.3v和源极电压为2.5v的组合可导致高侧输出晶体管112在线性运行区域中运行。可执行类似的操作以使cin 106放电,以耗散在高侧输入晶体管116上的放电能量的一部分。二极管214、216以及下文进一步示出的图5的二极管518可以是可选的。这些二极管可降低放电电路220的设计和生产成本。

49.图3是根据本公开的实施方案的放电电路300的具体实施的图示。放电电路300可实现放电电路220。在一个实施方案中,放电电路300可通过输入端122从高侧晶体管112、116中的一个或多个接收id。在另一个实施方案中,放电电路300可通过输入端124(未示出)从高侧晶体管中的一个或多个接收id。id可以表示在电容器的能量的一些部分已经被高侧晶体管112、116中的一个或多个耗散之后待耗散的电流。放电电路可包括晶体管布置。晶体管布置可包括晶体管306、308。

50.输入id可连接至第一晶体管308的漏极。第一晶体管308的源极可接地。放电电路300可包括第二晶体管306。第一晶体管308的栅极(或控制端子)、第一晶体管306的栅极(或控制端子)和第二晶体管306的漏极可各自可切换地连接至电流源302。电流源302可以是由值iref表示的恒流基准源。当控制电路120在放电模式下运行时,电流源302可被施加到晶体管306、308。因此,放电电路300可包括开关s3 304。开关s3 304可由discharge信号控制。放电电路300可被配置为,当控制电路120在放电模式下运行时,耗散由晶体管306、308的电压降限定的能量。晶体管306、308可被配置为在放电模式期间,在线性区域中操作。电流源302可流动穿过第二晶体管306并在充当镜像晶体管的第一晶体管308中倍增。在该示例中,如果放电模式是使cout 108单独放电,则流动穿过第一晶体管308的电流可近似110ma,与id相同。高侧输出晶体管112和第一晶体管308的组合可形成共源共栅结构。

51.放电电路300的该示例性具体实施可仅使用低功率部件并因此耗散少量功率。因此,放电电路300的该示例性具体实施可更易于集成在用于控制电路120的管芯的较小硅区域或较小具体实施中。放电电路300可能不需要热保护,而在多种情况下仍然有效地使线路电压放电。例如,在usb应用中,usb功率传送可具有如下最坏情况条件:充电至20v的3000pf电容器必须在小于600毫秒内放电至低于0.5v。放电电路300的其他具体实施,诸如使用电阻器来耗散能量,可能仅使用放电电路300就能够耗散6w的峰值。使用恒流放电的再另一个具体实施可能能够耗散2.2w的热量。然而,由于系统100中的高侧晶体管112、116的能量耗散,晶体管306、308在放电电路300中的在200mw至300mw范围内的能量耗散可能是足够的。在一些情况下,在放电模式期间高侧晶体管112、116的能量耗散可以是比由稳压器104提供功率的正常操作少的能量,因而可能不需要附加的热方面的考虑。

52.然而,如果在与放电电路300相同的半导体器件或管芯上实现高侧晶体管112、116,则在放电模式下的能量耗散可能需要额外的热保护。

53.图4是根据本公开的实施方案的另一个放电电路400的具体实施的图示。放电电路400可实现放电电路220。放电电路400可与放电电路300类似地操作。放电电路400可包括连

接至电阻器404的开关s4 402。开关s4402可由discharge信号控制。

54.返回图2,可根据控制电路120的需要调节电压源224、226。可通过(例如)控制逻辑部件222调节电压源224、226。可动态地调节电压源224、226来改善放电电流id的准确性,以便耗散放电电路200中特定量的能量。此外,电压源224、226可被配置为当放电电路220由放电电路300实现时,被动态地调节以改变晶体管308的能量耗散。电压源224、226的此类调节可响应于温度变化、干扰或控制电路120的其他非理想变化或操作来执行。

55.在图2中,示出了放电电路220的单个实例,该放电电路可被配置为耗散cin 106和cout 108两者中的能量。然而,在各种实施方案中,可将放电电路220的单独实例设置在控制电路120中以单独地耗散来自cin106和cout 108的能量,该cin和cout中的每个都具有到控制电路120的相应输入端。对于低频率(诸如可能在放电期间经历的那些),电感器110可具有可忽略不计的电压降。因此,放电电路220能够通过电感器110耗散cin 106的能量,如上所述。

56.因此,控制电路120被配置为使连接至电源或其他器件的电源线的电容放电。控制电路120可利用已存在于功率调节解决方案中的高侧功率开关(诸如高侧晶体管112、116中的一者)。控制电路120可被配置为通过使用此类高侧晶体管112、116作为线性功率耗散器来利用已存在的高侧晶体管112、116。该技术可通过减小以放电电路220的形式专用于放电功能的硅面积来降低具体实施的成本。该解决方案降低了被耗散的放电电路220的功率,因此通常消除了对专用热保护的需要。这可增加控制电路120的耐用性。这还可通过以下方式避免其他放电电路的缺点:减小耗散功率所需的大面积,避免需要紧密耦接的热保护,消除输入电压不可控地升高的风险,消除电感器110饱和的风险,并且不需要额外的引脚来与外部元件进行接合。

57.图5是根据本公开的实施方案的另一个系统500的图示,该系统被配置为使用具有低功率部件的线路放电电路来提供功率。系统500可包括向usb元件或器件提供功率的应用。系统500可包括来自电压源(未示出)的将作为vout施加到usb元件或器件的vin。usb功率开关可由晶体管506、508提供和实现。vin可施加到晶体管506的漏极。vout可由晶体管508的漏极提供。晶体管506、508的源极可彼此连接。晶体管506、508的栅极可连接至控制电路510的输出端。晶体管506、508的源极可继而连接至控制电路510的输入端。输入电容器502可形成在输入电源线上,并且输出电容器504可形成在输出电源线上。控制电路510可被配置为在放电模式下耗尽电容器502、504中的一者或多者。

58.控制电路510可以与控制电路120类似的方式来实现。控制电路510可包括被配置为向控制电路510的各个部分发出控制信号的控制逻辑部件522。控制逻辑522被配置为发出discharge信号、ndischarge信号和控制信号ctl。当控制电路510处于放电模式时,discharge信号可为高。当控制电路510处于常规操作模式时,ndischarge信号可为高。当控制电路510处于常规操作模式时,ctl信号可为高。

59.在常规操作模式期间,ctl信号可被发布到缓冲器512的输入,该缓冲器的输出继而可被引导至晶体管506、508的栅极。缓冲器512还可在其控制输入端处接收ndischarge信号,该ndischarge信号在常规操作模式期间(即,当ndischarge信号为高时)可使能缓冲器512向晶体管506、508的栅极提供其输出。在常规操作模式期间,discharge信号可为未激活、低或逻辑零,并且因此断开开关s1 516,该开关否则将经由二极管518将电压源514连接

至晶体管506、508的栅极。

60.在放电操作模式期间,ctl信号可被关断(即,设置为低)。此外,ndischarge信号可为低或逻辑零(即有效低电平(active low))并且因此停用缓冲器512。因此,在放电操作模式下,晶体管506、508的栅极将不会从缓冲器512接收其输入。相反,discharge信号可为有效、高、或逻辑一并且闭合开关s1 516。电压源514可被配置为当开关s1 516闭合时,向晶体管506、508的栅极提供其值(减去在二极管518上的电压降,该二极管可用作隔离二极管)。可执行对电压源514的值的选择以及对一个或多个二极管(诸如二极管518)的选择,以便在放电模式期间在线性运行区域中操作晶体管506、508。这可导致晶体管506、508中的功率耗散,其中剩余功率由通过输入端525接收的控制电路510的放电电路520耗散。放电电路520可由(例如)放电电路220、300或400实现。

61.例如,假定vin为20v并且vout也为20v。电容器502可为3000μf并且电容器504可为10μf。从电容器502流动穿过晶体管506的电流可被给定为idi。从电容器504流动穿过晶体管508的电流可被给定为ido。放电电流id可以是idi和ido的总和。放电电流id可通过输入端525引导至控制电路510中的放电电路520。当电容器502、504被充电到给定电压时,idi和ido之和可等于id,对于不匹配的晶体管506、508,不可能辨别每个晶体管中的电流的单独的值。一旦电容器502、504中的一者放电,对应晶体管上的电压就减小,直到其大致为源极的电压,并且随后rds阻止ids流动。随后,另一个晶体管的vgs增大(当其源极被下拉时),从而增大其电流,直到在放电结束时,电流趋于分开,诸如502和504两者具有类似的电压,并且以自匹配方式继续放电。如果电源514被配置为提供5v并且二极管518提供0.7v电压降,则晶体管506、508处的栅极(或控制端子)电压将为4.3v,晶体管506、508的电压降可为17.5v,这意味着id以2.5v施加到放电电路520。在大约100ma下,晶体管506、508的栅极电压可为4.3v,晶体管506、508的vgs可为1.8v。因此,晶体管506、508的源极可处于2.5v,并且vds可因此为17.5v。栅极(或控制端子)和源极电压可使得晶体管506、508在线性运行区域中运行。要从电容器502、504耗散的功率的组合可为2.2w。晶体管506、508可耗散1.925w。放电电路520可耗散0.275w。

62.图6是根据本公开的实施方案的方法600的图示,该方法使用具有低功率部件的线路放电电路来提供功率。方法600可使用任何合适的机制实现,诸如图1至图5的系统和电路。方法600可在任何合适的点开始,诸如在步骤605处。方法600可使用比图6中所示更多或更少的步骤来执行。方法600的各种步骤可省略,可重复,或可与方法600的其他步骤并行地执行。例如,步骤640和635可同时执行。方法600可任选地根据任何合适的标准或控制机制重复或终止。

63.在步骤605处,可确定该方法是在功率调节器中执行放电操作还是正常功率操作。正常操作可包括转换功率或向负载提供恒定功率水平。放电操作可包括耗尽或耗散在输入端、输出端或这两者处在线路电容上形成的能量。如果使用正常操作,则方法600可前进至步骤610。如果使用放电操作,则方法600可前进至步骤615。

64.在步骤610处,可从源极向负载提供功率。可以任何合适的方式或模式诸如降压、升压或降压

‑

升压来提供功率。可继续提供功率直至满足标准(诸如时间、累积的功率或指示操作模式应改变的外部信号)。方法600可返回至步骤605。

65.在步骤615处,可向稳压器中的功率开关栅极(或控制端子)选择器发出禁用信号。

该禁用信号可导致从输入端向输出端提供功率的正常操作停止。在一个实施方案中,如上文关于图2和图5所述,可通过将ndischarge设定为低电平来实现禁用信号。

66.在步骤620处,可将电压源引导至功率调节器的一个或多个高侧开关的栅极。可选择电压源以便在线性运行区域内操作开关。可通过例如使电压源电压通过一个或多个二极管然后将结果施加到开关的栅极来衰减电压源值。在一个实施方案中,如上文关于图2和图5所述,电压源可响应于有效高discharge信号而被引导。

67.在步骤625处,可在线性区域中操作将电压源接收到其相应栅极的高侧开关。

68.在步骤630处,输入端、输出端或两者上的线路电容可通过在其线性区域中运行的相应的高侧开关耗尽。

69.在步骤635处,可根据线性区域操作在高侧开关中耗散功率。

70.在步骤640处,待耗散的任何剩余功率可在内部放电电路中耗散。

71.在步骤645处,如有必要,可调节电压源的输出值。可对此类值进行调节以便确保将来在线性区域中操作开关,或考虑到由干扰、温度变化或其他非理想条件引起的变化。

72.方法600可返回到步骤605,或者可任选地基于任何合适的标准而终止。

73.尽管上文已描述了示例实施方案,但在不脱离这些实施方案的实质和范围的情况下,可由本公开进行其他变型和实施方案。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1