静电放电电路及其防止集成电路因电源反接而故障的方法与流程

1.本发明涉及一种静电放电(electrostatic discharge,esd)电路,尤其涉及一种esd电路及其防止集成电路(integrated circuit,ic)因电源反接而故障(failed)的方法。

背景技术:

2.ic内会设有esd电路来避免ic因受esd而损坏,但ic在生产过程中也会因连接的外部电源反接而故障,尤其是外部电源反接产生通过esd电流路径(current path)的瞬间大电流将烧坏ic与外部电源耦接的引脚或接线而造成ic故障,或者进一步造成esd电路或ic的内部电路损坏。因此,如何设计出一种esd电路及其防止ic因电源反接而故障的方法则成为本领域的一项重要课题。

技术实现要素:

3.有鉴于此,本发明实施例提供一种esd电路,适用于ic中,并通过第一引脚和第二引脚耦接外部电源,且外部电源反接是指第一引脚和第二引脚分别耦接外部电源的负极和正极。所述esd电路包括至少一金氧半场效晶体管和控制电路,所述至少一金氧半场效晶体管用来提供esd电流路径,以避免esd电流流入ic的内部电路而造成损坏。控制电路则耦接所述至少一金氧半场效晶体管,用来当外部电源反接时,改变所述至少一金氧半场效晶体管的基极电位,使得关闭所述至少一金氧半场效晶体管,以防止外部电源反接产生通过所述至少一金氧半场效晶体管的电流而造成ic故障。

4.本发明实施例另提供一种防止ic因电源反接而故障的方法,执行于ic的esd电路中。esd电路通过第一引脚和第二引脚耦接外部电源,且外部电源反接是指第一引脚和第二引脚分别耦接外部电源的负极和正极,所述方法包括如下步骤。当外部电源反接时,利用控制电路改变用来提供esd电流路径的至少一金氧半场效晶体管的基极电位,使得关闭所述至少一金氧半场效晶体管,以防止外部电源反接产生通过所述至少一金氧半场效晶体管的电流而造成ic故障。

5.为使能更进一步了解本发明的特征及技术内容,请参阅以下有关本发明的详细说明与图式,然而所提供的图式仅用于提供参考与说明,并非用来对本发明加以限制。

附图说明

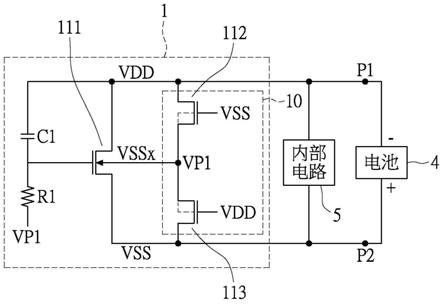

6.图1是本发明第一实施例所提供的esd电路的电路示意图。

7.图2是本发明第二实施例所提供的esd电路的电路示意图。

8.图3是本发明第三实施例所提供的esd电路的电路示意图。

9.图4是本发明实施例所提供防止ic因电源反接而故障的方法的步骤流程图。

具体实施方式

10.以下是通过特定的具体实施例来说明本发明的实施方式,本领域技术人员可由本

说明书所提供的内容了解本发明的优点与效果。本发明可通过其他不同的具体实施例加以施行或应用,本说明书中的各项细节也可基于不同观点与应用,在不悖离本发明的构思下进行各种修改与变更。另外,本发明的附图仅为简单示意说明,并非依实际尺寸的描绘,事先声明。以下的实施方式将进一步详细说明本发明的相关技术内容,但所提供的内容并非用以限制本发明的保护范围。

11.应当理解的是,虽然本文中可能会使用到“第一”、“第二”、“第三”等术语来描述各种组件或者信号,但这些组件或者信号不应受这些术语的限制。这些术语主要是用以区分一组件与另一组件,或者一信号与另一信号。另外,本文中所使用的术语“或”,应视实际情况可能包括相关联的列出项目中的任一个或者多个的组合。

12.值得一提的是,本发明实施例所提供的esd电路,可以是适用于任何ic中,总而言之,本发明并不限制ic的具体实现方式,本领域技术人员应可依据实际需求或应用来进行设计。

13.请参阅图1,图1是本发明第一实施例所提供的esd电路的电路示意图。esd电路1通过第一引脚p1和第二引脚p2耦接外部电源4,尤其第一引脚p1和第二引脚p2通常是以打线接合(wire bonding)的方式与外部电源4连接。在本实施例中,外部电源4可例如为电池,但本发明并不以此为限制,且外部电源4反接是指第一引脚p1和第二引脚p2分别耦接电池的负极和正极,如图1所示。

14.esd电路1包括控制电路10和用来提供esd电流路径的金氧半场效晶体管111,以避免esd电流流入ic的内部电路5而造成损坏。也就是说,本实施例的ic包含内部电路5和esd电路1,且内部电路5和esd电路1以并联方式耦接于接收电源电压vdd的第一引脚p1和接收接地电压vss的第二引脚p2间。

15.另外,控制电路10耦接金氧半场效晶体管111,用来当外部电源4(电池)反接时,改变金氧半场效晶体管111的基极电位,使得关闭金氧半场效晶体管111,以防止外部电源4(电池)反接产生通过金氧半场效晶体管111的瞬间大电流而造成ic故障。如前所述,本实施例的ic故障可以是指该瞬间大电流烧坏ic与外部电源4(电池)耦接的第一引脚p1、第二引脚p2或接线。

16.为了方便以下说明,图1用来提供esd电流路径的金氧半场效晶体管111可先例如为一个n型金氧半场效晶体管,但本发明并不以此为限制,且既然是在使用n型金氧半场效晶体管提供esd电流路径的情况下,esd电路1更可包括电容c1和电阻r1。电容c1的第一端与金氧半场效晶体管111的漏极(d)共同耦接接收电源电压vdd的第一引脚p1,且电容c1的第二端则耦接金氧半场效晶体管111的栅极(g)。

17.请注意,本发明亦不限制电容c1的具体实现方式,在其它实施例中,电容c1也可为有极性电容,且电容c1的第一端和第二端就分别是指有极性电容的正端和负端。另外,电阻r1的第一端与电容c1的第二端可共同耦接金氧半场效晶体管111的栅极(g),且电阻r1的第二端则耦接变压节点vp1。

18.如此一来,当esd发生在第一引脚p1时,即第一引脚p1收到正的静电电压,由于其高电压特性,会在电容c1上产生电压差,且由于这电压差的存在,会对金氧半场效晶体管111产生约数百毫秒的导通时间,因此寄生的二极管(diode)会导通来排放esd电流,且导通后的金氧半场效晶体管111也会提供连通的通道,即esd电流路径来共同排放esd电流,以达

成esd防护的效果。由于有关金氧半场效晶体管111、电容c1和电阻r1的运作原理已皆为本领域技术人员所习知,因此其细节就不再多加赘述。

19.需说明的是,为了能够当外部电源4(电池)反接时,改变金氧半场效晶体管111的基极电位,使得关闭金氧半场效晶体管111,以防止外部电源4(电池)反接产生通过金氧半场效晶体管111的电流而造成ic故障,图1的控制电路10可包括n型金氧半场效晶体管112和n型金氧半场效晶体管113。在本实施例中,n型金氧半场效晶体管112的漏极(d)耦接接收电源电压vdd的第一引脚p1,且n型金氧半场效晶体管112的栅极(g)则接收接地电压vss。

20.另外,n型金氧半场效晶体管113的源极(s)与n型金氧半场效晶体管112的源极(s)共同通过变压节点vp1耦接金氧半场效晶体管111的基极,n型金氧半场效晶体管113的栅极(g)则接收电源电压vdd,且n型金氧半场效晶体管113的漏极(d)与金氧半场效晶体管111的源极(s)共同耦接接收接地电压vss的第二引脚p2。由于有关n型金氧半场效晶体管112和n型金氧半场效晶体管113的运作原理也已为本领域技术人员所习知,因此其细节就不再多加赘述。

21.由此可见,不同于现有技术可能是在外部电源4(电池)反接时改变电流路径,图1的esd电路1是利用n型金氧半场效晶体管112和n型金氧半场效晶体管113来让金氧半场效晶体管111的基极收到一个低电压,例如vssx,且由于电阻r1的第二端耦接变压节点vp1,会使得电阻r1的第二端和金氧半场效晶体管111的基极具有相同电位,即电压vssx,因此寄生的二极管将不会导通,且金氧半场效晶体管111也不会导通,以达成防止外部电源4(电池)反接产生通过金氧半场效晶体管111的电流而造成ic故障。另外,请参阅图2,图2是本发明第二实施例所提供的esd电路的电路示意图,且图2中部分与图1相同的元件以相同的符号表示,故于此就不再详述其细节。

22.如图2所示,内部电路5和esd电路2同样以并联方式耦接于第一引脚p1和第二引脚p2间,且esd电路2通过第一引脚p1和第二引脚p2耦接外部电源4(电池)。但不同于图1的金氧半场效晶体管111,图2用来提供esd电流路径的金氧半场效晶体管121则例如为一个p型金氧半场效晶体管,但本发明亦不以此为限制,且既然是在使用p型金氧半场效晶体管提供esd电流路径的情况下,esd电路2更可包括电阻r2和电容c2。

23.电阻r2的第一端耦接变压节点vp2,且电阻r2的第二端则耦接金氧半场效晶体管121的栅极(g)。另外,电容c2的第一端与电阻r2的第二端可共同耦接金氧半场效晶体管121的栅极(g),且电容c2的第二端与p型金氧半场效晶体管121的漏极(d)共同耦接接收接地电压vss的第二引脚p2。如前所述,在其它实施例中,电容c2也可为有极性电容,且电容c2的第一端和第二端就分别是指有极性电容的正端和负端,但本发明并不以此为限制。

24.如此一来,当esd发生在第一引脚p1时,即第一引脚p1收到正的静电电压,由于其高电压特性,会在电容c2上产生电压差,且由于这电压差的存在,会对金氧半场效晶体管121产生约数百毫秒的导通时间,因此寄生的二极管会导通来排放esd电流,且导通后的金氧半场效晶体管121也会提供连通的通道,即esd电流路径来共同排放esd电流,以达成esd防护的效果。由于有关金氧半场效晶体管121、电阻r2和电容c2的运作原理也已为本领域技术人员所习知,因此其细节就不再多加赘述。

25.类似地,为了能够当外部电源4(电池)反接时,改变金氧半场效晶体管121的基极电位,使得关闭金氧半场效晶体管121,以防止外部电源4(电池)反接产生通过金氧半场效

晶体管121的电流而造成ic故障,图2的控制电路10可包括p型金氧半场效晶体管122和p型金氧半场效晶体管123。在本实施例中,p型金氧半场效晶体管122的漏极(d)与金氧半场效晶体管121的源极(s)共同耦接接收电源电压vdd的第一引脚p1,且p型金氧半场效晶体管122的栅极(g)则接收接地电压vss。

26.另外,p型金氧半场效晶体管123的源极(s)与p型金氧半场效晶体管122的源极(s)共同通过变压节点vp2耦接金氧半场效晶体管121的基极,p型金氧半场效晶体管123的栅极(g)则接收电源电压vdd,且p型金氧半场效晶体管123的漏极(d)耦接接收接地电压vss的第二引脚p2。由于有关p型金氧半场效晶体管122和p型金氧半场效晶体管123的运作原理也已为本领域技术人员所习知,因此其细节就不再多加赘述。

27.由此可见,不同于现有技术可能是在外部电源4(电池)反接时改变电流路径,图2的esd电路2是利用p型金氧半场效晶体管122和p型金氧半场效晶体管123来让金氧半场效晶体管121的基极收到一个低电压,例如vddx,且由于电阻r2的第一端耦接变压节点vp2,会使得电阻r2的第一端和金氧半场效晶体管121的基极具有相同电位,即电压vddx,因此寄生的二极管将不会导通,且金氧半场效晶体管121也不会导通,以达成防止外部电源4(电池)反接产生通过金氧半场效晶体管121的电流而造成ic故障。

28.最后,请参阅图3,图3是本发明第三实施例所提供的esd电路的电路示意图,且图3中部分与图1或图2相同的元件以相同的符号表示,故于此就不再详述其细节。如图3所示,内部电路5和esd电路3同样以并联方式耦接于第一引脚p1和第二引脚p2间,且esd电路3通过第一引脚p1和第二引脚p2耦接外部电源4(电池)。但不同于图1的金氧半场效晶体管111或图2的金氧半场效晶体管121,图3用来提供esd电流路径的金氧半场效晶体管114和124则例如为一个n型金氧半场效晶体管和一个p型金氧半场效晶体管,但本发明亦不以此为限制。

29.在本实施例中,金氧半场效晶体管114的漏极(d)耦接金氧半场效晶体管124的漏极(d),且既然是在使用一个n型金氧半场效晶体管和一个p型金氧半场效晶体管提供esd电流路径的情况下,esd电路3更可包括电容c3、电阻r3、电阻r4和电容c4。电容c3的第一端与金氧半场效晶体管124的源极(s)共同耦接接收电源电压vdd的第一引脚p1,且电容c3的第二端则耦接金氧半场效晶体管114的栅极(g)。

30.另外,电阻r3的第一端与电容c3的第二端可共同耦接金氧半场效晶体管114的栅极(g),且电阻r3的第二端耦接变压节点vp3。电阻r4的第一端则耦接变压节点vp4,且电阻r4的第二端耦接金氧半场效晶体管124的栅极(g)。电容c4的第一端与电阻r4的第二端可共同耦接金氧半场效晶体管124的栅极(g),且电容c4的第二端与金氧半场效晶体管114的源极(s)共同耦接接收接地电压vss的第二引脚p2。

31.如此一来,当esd发生在第一引脚p1时,即第一引脚p1收到正的静电电压,由于其高电压特性,会在电容c3和c4上产生电压差,且由于这两个电压差的存在,会对金氧半场效晶体管114和124产生约数百毫秒的导通时间,因此寄生的二极管会导通来排放esd电流,且导通后的金氧半场效晶体管114和124也会提供连通的通道,即esd电流路径来共同排放esd电流,以达成esd防护的效果。由于运作细节已如同前述内容所述,故于此就不再多加赘述。

32.类似地,为了能够当外部电源4(电池)反接时,改变金氧半场效晶体管114和124的基极电位,使得关闭金氧半场效晶体管114和124,以防止外部电源4(电池)反接产生通过金

氧半场效晶体管114和124的电流而造成ic故障,图3的控制电路10可包括n型金氧半场效晶体管115~118和p型金氧半场效晶体管125~128。

33.在本实施例中,n型金氧半场效晶体管115的漏极(d)耦接接收电源电压vdd的第一引脚p1,且n型金氧半场效晶体管115的栅极(g)则接收接地电压vss。另外,n型金氧半场效晶体管116的源极(s)与n型金氧半场效晶体管115的源极(s)共同通过变压节点vp3耦接金氧半场效晶体管114的基极,n型金氧半场效晶体管116的栅极(g)则接收电源电压vdd,且n型金氧半场效晶体管116的漏极(d)耦接接收接地电压vss的第二引脚p2。

34.相对地,p型金氧半场效晶体管125的漏极(d)耦接接收电源电压vdd的第一引脚p1,且p型金氧半场效晶体管125的栅极(g)则接收接地电压vss。另外,p型金氧半场效晶体管126的源极(s)与p型金氧半场效晶体管125的源极(s)共同通过变压节点vp4耦接金氧半场效晶体管124的基极,p型金氧半场效晶体管126的栅极(g)则接收电源电压vdd,且p型金氧半场效晶体管126的漏极(d)耦接接收接地电压vss的第二引脚p2。

35.再者,n型金氧半场效晶体管117串联于第一引脚p1与n型金氧半场效晶体管115间。n型金氧半场效晶体管117的漏极(d)耦接接收电源电压vdd的第一引脚p1,n型金氧半场效晶体管117的栅极(g)则接收一个遮蔽电压vsh,且n型金氧半场效晶体管117的源极(s)耦接n型金氧半场效晶体管115的漏极(d)。

36.n型金氧半场效晶体管118串联于第二引脚p2与n型金氧半场效晶体管116间。n型金氧半场效晶体管118的漏极(d)耦接接收接地电压vss的第二引脚p2,n型金氧半场效晶体管118的栅极(g)则接收遮蔽电压vsh,且n型金氧半场效晶体管118的源极(s)耦接n型金氧半场效晶体管116的漏极(d)。

37.相对地,p型金氧半场效晶体管127串联于第一引脚p1与p型金氧半场效晶体管125间。p型金氧半场效晶体管127的漏极(d)耦接接收电源电压vdd的第一引脚p1,p型金氧半场效晶体管127的栅极(g)则接收遮蔽电压vsh,且p型金氧半场效晶体管127的源极(s)耦接p型金氧半场效晶体管125的漏极。

38.p型金氧半场效晶体管128串联于第二引脚p2与p型金氧半场效晶体管126间。p型金氧半场效晶体管128的漏极(d)耦接接收接地电压vss的第二引脚p2,p型金氧半场效晶体管128的栅极(g)则接收遮蔽电压vsh,且p型金氧半场效晶体管128的源极(s)耦接p型金氧半场效晶体管126的漏极。由于有关n型金氧半场效晶体管115~118和p型金氧半场效晶体管125~128的运作原理也已为本领域技术人员所习知,因此其细节就不再多加赘述。

39.实作上,遮蔽电压vsh可例如为电源电压vdd减去接地电压vss后再除以2的电压,但本发明并不以此为限制,总而言之,不同于现有技术可能是在外部电源4(电池)反接时改变电流路径,图3的esd电路3是利用n型金氧半场效晶体管115~118和p型金氧半场效晶体管125~128来让金氧半场效晶体管114和124的基极分别收到一个低电压,例如vssx和vddx,并使得电阻r3的第二端和金氧半场效晶体管114的基极具有相同电位,即电压vssx,也使得电阻r4的第一端和金氧半场效晶体管124的基极具有相同电位,即电压vddx,导致寄生的二极管将不会导通,且金氧半场效晶体管114和124也不会导通,以达成防止外部电源4(电池)反接产生通过金氧半场效晶体管114和124的电流而造成ic故障。

40.另一方面,请参阅图4,图4是本发明实施例所提供防止ic因电源反接而故障的方法的步骤流程图。需说明的是,图4的方法可以是执行于图1的esd电路1、图2的esd电路2或

图3的esd电路3中,因此请一并参照图1~图3以利理解,但本发明并不限制图4的方法仅能够执行于esd电路1、2或3中。

41.如图4所示,当外部电源4(电池)反接时,在步骤s410中,esd电路1、2或3可利用控制电路10改变用来提供esd电流路径的至少一金氧半场效晶体管的基极电位,使得关闭所述至少一金氧半场效晶体管,以防止外部电源4(电池)反接产生通过所述至少一金氧半场效晶体管的电流而造成ic故障。由于细节已如同前述内容所述,故于此就不再多加赘述。

42.综上所述,本发明实施例提供一种esd电路及其防止ic因电源反接而故障的方法。所述esd电路包括用来提供esd电流路径的至少一金氧半场效晶体管,以及耦接所述至少一金氧半场效晶体管的控制电路。当外部电源反接时,控制电路用来改变所述至少一金氧半场效晶体管的基极电位,使得关闭所述至少一金氧半场效晶体管,以防止外部电源反接产生通过所述至少一金氧半场效晶体管的电流而造成ic故障。

43.以上所公开的内容仅为本发明的优选可行实施例,并非因此局限本发明的申请专利范围,所以凡是运用本发明说明书及图式内容所做的等效技术变化,均包含于本发明的申请专利范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1