涌浪电流抑制电路的制作方法

1.本发明涉及一种保护电路,特别涉及一种涌浪电流抑制电路。

背景技术:

2.对于电子装置的内部电路而言,为了抑制输入涌浪电流,通常会设置电流抑制电路于电子装置的输入端。现有的电流抑制电路,例如包含电阻及与所述电阻并联的开关如继电器。于电子装置开机启动时,输入电源信号所产生的涌浪电流由电流抑制电路的电阻来限制。当电流抑制电路进入稳态后,电流抑制电路的开关将会开启,从而使输入电源信号通过开关进入电子装置的内部电路(或称系统负载)以减少损耗。

3.然而,于电子装置开机启动后,当提供输入电源信号的源头(例如市电)因不稳而造成输入电源信号异常时,涌浪电流会再次产生,并通过开关进入电子装置的内部电路。一旦开关的瞬间耐流不足以耐受涌浪电流时,开关将会损毁。为解决此问题,可采用瞬间耐流较高的开关。虽可避免开关损毁,但仍无法抑制涌浪电流流至电子装置的内部电路,而造成电子装置的内部电路瞬间所需的电流升高,造成保险丝熔断或断路器断开的状况,进而影响电路安全性。换句话说,现有的电流抑制电路仅能抑制电子装置开机启动时,初始输入电源信号所产生的涌浪电流;而无法抑制电子装置开机启动后,输入电源信号异常所产生的涌浪电流。

4.是以,为了提升电子装置在初始输入电源信号输入时及输入电源信号异常时的电路安全性,目前的电流抑制技术仍有待改善。

技术实现要素:

5.本发明的目的在于提出一种涌浪电流抑制电路,其通过主动开关单元以及电流检测单元的协同运作以抑制涌浪电流,能够提升电子装置在输入电源信号异常时的电路安全性。

6.为达至少上述目的,本发明提出一种涌浪电流抑制电路,用以与电容性装置串联,且与电容性装置耦接于第一电源输入端与第二电源输入端之间,涌浪电流抑制电路包括:主动开关单元以及电流检测单元。主动开关单元与电容性装置串联,且具有控制端,其中控制端用以接收控制电压信号。电流检测单元与主动开关单元串联,且用以根据流经的第一电流产生检测电压信号。当第一电流自第一电源输入端流入并通过电流检测单元时,电流检测单元产生检测电压信号,当检测电压信号大于或等于检测电压门槛值时,主动开关单元关闭,从而抑制第一电流。

7.在涌浪电流抑制电路的一些实施例中,主动开关单元还具有第一端及第二端,电容性装置耦接于第一电源输入端与主动开关单元的第一端之间,电流检测单元耦接于主动开关单元的第二端与第二电源输入端之间。

8.在涌浪电流抑制电路的一个实施例中,涌浪电流抑制电路,还包含单向导通单元,单向导通单元与电流检测单元并联,其中当第二电流自第二电源输入端流入时,第二电流

依序通过单向导通单元、主动开关单元及电容性装置而流向第一电源输入端。

9.在涌浪电流抑制电路的一些实施例中,当检测电压信号大于或等于检测电压门槛值时,主动开关单元的控制端与第二端之间的跨压无法达到主动开关单元的导通电压门槛值,以使主动开关单元关闭,从而抑制第一电流。

10.在涌浪电流抑制电路的一个实施例中,控制端所接收的控制电压信号通过将控制端耦接至第二电源输入端来获得。

11.在涌浪电流抑制电路的一些实施例中,主动开关单元还具有第一端及第二端,电流检测单元耦接于第一电源输入端与主动开关单元的第二端之间,电容性装置耦接于主动开关单元的第一端与第二电源输入端与之间。

12.在涌浪电流抑制电路的一些实施例中,涌浪电流抑制电路还包含单向导通单元,单向导通单元与电流检测单元并联,其中当第二电流自第二电源输入端流入时,第二电流依序通过电容性装置、主动开关单元及单向导通单元而流向第一电源输入端。

13.在涌浪电流抑制电路的一些实施例中,当检测电压信号大于或等于检测电压门槛值时,主动开关单元的第二端与控制端之间的跨压无法达到主动开关单元的导通电压门槛值,以使主动开关单元关闭,从而抑制第一电流。

14.在涌浪电流抑制电路的一实施例中,控制端所接收的控制电压信号通过将控制端耦接至第一电源输入端来获得。

15.在涌浪电流抑制电路的一些实施例中,涌浪电流抑制电路进一步包括开关控制单元用以提供所述控制电压信号,其中于所述控制电压信号的大小大于所述主动开关单元的所述控制端与所述第二端之间的跨压的大小时,所述主动开关单元开启,当所述第一电流自所述第一电源输入端流入并通过所述电流检测单元时,所述电流检测单元产生所述检测电压信号,当所述检测电压信号大于或等于所述检测电压门槛值时,所述主动开关单元关闭。

16.在涌浪电流抑制电路的一些实施例中,涌浪电流抑制电路进一步包括开关控制单元,开关控制单元用以提供控制电压信号;开关控制单元耦接于主动开关单元的控制端与电流检测单元之间,当第一电流自第一电源输入端流入并通过电流检测单元时,电流检测单元产生检测电压信号,当检测电压信号大于或等于检测电压门槛值时,开关控制单元根据检测电压信号控制主动开关单元关闭,从而抑制第一电流。

17.在涌浪电流抑制电路的一些实施例中,涌浪电流抑制电路还包含单向导通单元,单向导通单元与电流检测单元并联;当第二电流自第二电源输入端流入时,第二电流依序通过单向导通单元、主动开关单元及电容性装置而流向第一电源输入端。

18.在涌浪电流抑制电路的一些实施例中,涌浪电流抑制电路还包含单向导通单元,单向导通单元与电流检测单元并联;当第二电流自第二电源输入端流入时,第二电流依序通过电容性装置、主动开关单元及单向导通单元而流向第一电源输入端。

19.如上多个实施例,涌浪电流抑制电路通过主动开关单元以及电流检测单元的协同运作,从而抑制第一电流。相较于在开机启动后,上述现有的电流抑制电路因开关(如继电器)开启而不能产生抑制涌浪电流的作用的状况,本发明的涌浪电流抑制电路的实施例,不受输入电源信号异常的影响,在初始输入电源信号输入时及输入电源信号异常时皆能产生抑制涌浪电流的作用,故能提升电子装置在输入电源信号异常时的电路安全性。

附图说明

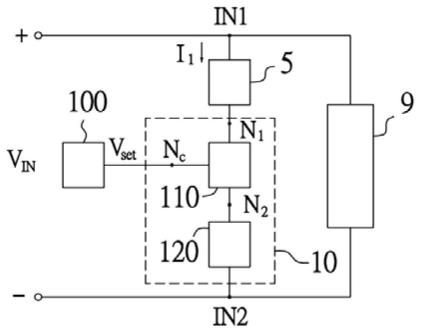

20.图1为涌浪电流抑制电路的一种实施方式的应用情景的示意框图。

21.图2a为基于图1的涌浪电流抑制电路的一个实施例的示意框图。

22.图2b为基于图2a的涌浪电流抑制电路的实施例的波形示意图。

23.图3a为基于图1的涌浪电流抑制电路的一个实施例的示意框图。

24.图3b为基于图1的涌浪电流抑制电路的另一个实施例的示意框图。

25.图4为涌浪电流抑制电路的另一种实施方式的应用情景的示意框图。

26.图5a为基于图4的涌浪电流抑制电路的一个实施例的示意框图。

27.图5b为基于图5a的涌浪电流抑制电路的实施例的波形示意图。

28.图6a为基于图4的涌浪电流抑制电路的一个实施例的示意框图。

29.图6b为基于图4的涌浪电流抑制电路的另一个实施例的示意框图。

30.图7为基于图1的涌浪电流抑制电路的另一个实施例的示意框图。

31.图8为基于图4的涌浪电流抑制电路的另一个实施例的示意框图。

32.附图标记:

33.5电容性装置

34.9内部电路

35.10、11、10a~10f涌浪电流抑制电路

36.10b1、10d1涌浪电流抑制电路

37.100、100a~100f开关控制单元

38.110、110a~110f、110p主动开关单元

39.120、120a~120f电流检测单元

40.130a~130d单向导通单元

41.i1第一电流

42.i2第二电流

43.ir流经电阻的电流

44.in1第一电源输入端

45.in2第二电源输入端

46.n1第一端

47.n2第二端

48.nc控制端

[0049]vset

控制电压信号

[0050]vin

输入电源信号

[0051]vgs

控制端nc与第二端n2之间的跨压

[0052]vsg

第二端n2与控制端nc之间的跨压

[0053]vr

检测电压信号

具体实施方式

[0054]

为充分了解本发明的目的、特征及功效,现在通过下述具体的实施例,并配合所附的图式,对本发明做详细说明,说明如后。

[0055]

请参考图1,其为涌浪电流抑制电路的一种实施方式的应用情景的示意框图。如图1所示,涌浪电流抑制电路10可应用于一种电子装置以抑制电子装置输入电容(如电容性装置5)的电流大小。举例而言,电子装置例如是电源转换装置、电子测试装置或其他装置等,且具有第一电源输入端in1与第二电源输入端in2以接收输入电源信号vin,并包含电容性装置5及内部电路9。内部电路9是后级电路或系统负载,例如对应的电源转换电路、电子测试电路或其他电路等。然而,本发明的实现并不受此应用情景限制。

[0056]

如图1所示,涌浪电流抑制电路10用以与电容性装置5串联,涌浪电流抑制电路10耦接于电容性装置5与第二电源输入端in2之间。涌浪电流抑制电路10包括主动开关单元110以及电流检测单元120。

[0057]

主动开关单元110与电容性装置5串联,且具有控制端nc,其中控制端nc耦接开关控制单元100,且用以接收控制电压信号v

set

。举例而言,主动开关单元110可以包含一个或多个晶体管来实现,例如金属氧化物半导体场效晶体管(mosfet)。控制电压信号v

set

例如可以由开关控制单元100来提供。

[0058]

电流检测单元120与主动开关单元110串联,且用以根据流经的第一电流i1产生检测电压信号。当第一电流i1自第一电源输入端in1流入并通过电流检测单元120时,电流检测单元120产生检测电压信号。当检测电压信号大于或等于检测电压门槛值时,主动开关单元110关闭,从而抑制第一电流i1。举例而言,电流检测单元120可以利用各种能依据流过电流检测单元120的电流而产生对应的电压信号以反应电流大小的元件来实现,例如电阻或其他元件。

[0059]

此外,控制电压信号v

set

的产生方式不限于开关控制单元100。又开关控制单元100可被视为环境元件,或被视为涌浪电流抑制电路10的的一个元件。

[0060]

图1为适用于利用n型晶体管来实现主动开关单元的电路架构。以下基于图1的涌浪电流抑制电路10的电路架构,提出涌浪电流抑制电路的各种实施例。

[0061]

图2a为基于图1的涌浪电流抑制电路10的一实施例的示意框图。如图2a所示,涌浪电流抑制电路10a包括开关控制单元100a、主动开关单元110a以及电流检测单元120a。举例而言,开关控制单元100a可以实现为包含电源电路或其他合适电路,以提供控制电压信号v

set

,其中控制电压信号v

set

例如为固定值。主动开关单元110a具有控制端nc、第一端n1及第二端n2。电容性装置5耦接于第一电源输入端in1与主动开关单元110a的第一端n1之间。电流检测单元120a耦接于主动开关单元110a的第二端n2与第二电源输入端in2之间。在图2a中,主动开关单元110a可以包含一个n型晶体管,例如n型mosfet(或简称nmos),如增强型nmos,故图2a为利用nmos来实现主动开关单元110a时的电路架构的实施例。此外,电流检测单元120a例如包含一个电阻来实现,且根据流经的第一电流i1产生检测电压信号vr,其中vr=ir*r,ir为流经电阻的电流,r为电阻的电阻值。在第一电流i1流经电阻的情况下,电流ir等于第一电流i1。

[0062]

在图2a的涌浪电流抑制电路10a的实施例中,利用nmos来实现主动开关单元110a,故当检测电压信号大于或等于检测电压门槛值时,主动开关单元110a的控制端nc与第二端n2之间的跨压(如晶体管的栅极及源极之间的电压v

gs

)无法达到主动开关单元110a的导通电压门槛值(如晶体管的导通电压门槛值v

th

),以使主动开关单元110a关闭,从而抑制第一电流i1。

[0063]

以下进一步说明主动开关单元110a的开启及关闭条件。在电路启动的瞬间,主动开关单元110a为导通的状态,此时会有第一电流i1对电容性装置5(如电容)充电。由图2a的电路可知,v-set

、v

gs

、vr之间的关系为:

[0064]vset

=v

gs

+vr。

ꢀꢀ

(公式1)

[0065]

在控制电压信号v

set

为固定值且大于v

gs

的状况下,随着第一电流i1的变大,vr也变大,相对之下v

gs

变小;当v

gs

《v

th

时,主动开关单元110a关闭。故在实现本实施例时,可通过调整电流检测单元120a中电阻的电阻值来限制最大电流(如记作i

max

),从而达到限流的功能。详细来说,在图2a中,晶体管关闭的条件为:

[0066]vgs

《v

th

。

ꢀꢀ

(条件式1)

[0067]

由公式1可知v

gs

=v

set-vr,其中vr=ir*r,故由条件式1可得出:

[0068]vset-vr《v

th

;

[0069]vset-ir*r《v

th

;

[0070]

由此可推导出电流ir的大小能够令晶体管关闭的条件为:

[0071]

ir》(v

set-v

th

)/r。

ꢀꢀ

(条件式2)

[0072]

由条件式2可知,当电流ir大小符合条件式2时,则晶体管关闭。就抑制涌流电流的目的来说,欲限制电流ir小于最大电流i

max

,则调整电阻r的大小即可。借此,可进一步设定v

max

=i

max

*r,其中v

max

为检测电压门槛值。是以,当检测电压信号vr大于或等于检测电压门槛值(v

max

)时,主动开关单元110a的控制端nc与第二端n2之间的跨压(如晶体管的栅极及源极之间的电压v

gs

)将无法达到主动开关单元110a的导通电压门槛值(如晶体管的导通电压门槛值v

th

),从而使主动开关单元110关闭,以抑制第一电流i1。

[0073]

请参考图2b,其为基于图2a的涌浪电流抑制电路10a的实施例的波形示意图。于图2b的上方的波形示意当第一电源输入端in1与第二电源输入端in2接收的输入电源信号v

in

从零电位上升到一个电压位准(电压大小)(如约380v)并维持定值时的波形。从上述涌浪电流抑制电路10a的主动开关单元110a的关闭条件的说明可知,依据公式1,如前所述在控制电压信号v

set

为固定值且大于v

gs

的状况下,随着第一电流i1的变大,流经电阻的电流ir变大(如图2b的中间的波形所示),因此vr也变大,相对之下v

gs

变小(如图2b的下方的波形所示)。当v

gs

《v

th

时,使主动开关单元110关闭,以抑制第一电流i1,如图2b的中间的波形所示,流经电阻的电流ir被抑制在预定的电流值(如23a)以下。

[0074]

再次回到图2a的实施例中,涌浪电流抑制电路10a还包含单向导通单元130a,且单向导通单元130a与电流检测单元120a并联。单向导通单元130a具有提供电流路径的作用。举例来说,当图1的内部电路9需要自电容性装置5汲取电流而使电容性装置5放电时,有与上述第一电流i1的电流方向相反的第二电流i2自第二电源输入端in2流入,且第二电流i2依序通过单向导通单元130a、主动开关单元110a及电容性装置5而流向第一电源输入端in1。单向导通单元130a例如包含一个二极管。此外,单向导通单元130a也具有保护主动开关单元110a的作用。当第二电流i

2-产生时,电流检测单元120a会产生反向电压。由于电流检测单元120a与单向导通单元130a并联,故单向导通单元130a将电流检测单元120a的反向电压限制为与二极管的跨压相同,从而使主动开关单元110a能避免承受过大的跨压而损坏的状况发生。再者,由于第二电流i2主要(或理想中完全)经由单向导通单元130a而流向第一电源输入端in1,从而减少了第二电流i2通过涌浪电流抑制电路10a时的功耗。

[0075]

如上,当图2a的涌浪电流抑制电路10a应用于如图1所述的电子装置中,当电子装置开启而使输入电源信号v

in

由零电位升至预定的电压位准时,第一电流i1将自第一电源输入端in1流入,且第一电流i1依序通过电容性装置5、主动开关单元110a及电流检测单元120a而流向第二电源输入端in2,此时电容性装置5将开始充电,此第一电流i1的电流路径可定义为充电电流路径。反过来说,当图1的内部电路9需要自电容性装置5汲取电流时,第二电流i2将自第二电源输入端in2流入,且第二电流i2依序通过单向导通单元130a、主动开关单元110a及电容性装置5而流向第一电源输入端in1,此时电容性装置5将开始放电,此第二电流i2的电流路径可定义为放电电流路径。如此,图2a的涌浪电流抑制电路10a能因应电容性装置5充电或放电而提供合适的电流路径,使设置涌浪电流抑制电路10a的电子装置能得以正常的运作。

[0076]

图3a为基于图1的涌浪电流抑制电路10的一个实施例的示意框图。相较于图2a的涌浪电流抑制电路10a,图3a的涌浪电流抑制电路10b与图2a的涌浪电流抑制电路10a的差异在于,图3a的涌浪电流抑制电路10b使用空乏型nmos来实现主动开关单元110b。如图3a所示,涌浪电流抑制电路10b包括开关控制单元100b、主动开关单元110b、电流检测单元120b。开关控制单元100b可以实现为包含电源电路或其他合适电路,以提供控制电压信号v

set

,例如控制电压信号v

set

大于v

gs

。主动开关单元110b具有控制端nc、第一端n1及第二端n2,电容性装置5耦接于第一电源输入端in1与主动开关单元110b的第一端n1之间,电流检测单元120b耦接于主动开关单元110b的第二端n2与第二电源输入端in2之间。在图3a中,主动开关单元110b包含空乏型nmos,电流检测单元120b包含电阻。

[0077]

以下进一步说明主动开关单元110b的开启及关闭条件。在电路启动的瞬间,空乏型nmos为导通的状态,此时会有第一电流i1对电容性装置5充电。由于v

set

=v

gs

+vr,随着第一电流i1的变大,vr也变大,相对之下v

gs

变小。当检测电压信号vr大于或等于检测电压门槛值时,主动开关单元110b的控制端nc与第二端n2之间的跨压(如晶体管的栅极及源极之间的电压v

gs

)将无法达到主动开关单元110b的导通电压门槛值(如晶体管的导通电压门槛值-v

th

),即使得则空乏型nmos的关闭条件v

gs

《-v

th

得以满足,从而使主动开关单元110b关闭,以抑制第一电流i1。在一示例中,当控制电压信号v

set

为与第二电源输入端in2的电位相同(如v

set

为零电位,v

set

=0)时,则v

gs

+vr=0;随着第一电流i1的变大,vr也变大,相对之下v

gs

变小;当空乏型nmos的关闭条件v

gs

《-v

th

得以满足时,则会使主动开关单元110b关闭,从而抑制第一电流i1。

[0078]

此外,图3b为基于图1的涌浪电流抑制电路10的另一个实施例的示意框图,其中图3b也是利用空乏型nmos来实现主动开关单元。相较于图3a的涌浪电流抑制电路10b,图3b的涌浪电流抑制电路10b1与图3a的涌浪电流抑制电路10b的差异在于,图3b的涌浪电流抑制电路10b1中不需使用开关控制单元来提供控制电压信号v

set

,控制端nc所接收的控制电压信号v

set

通过将控制端nc耦接至第二电源输入端in2来获得。如此一来,控制端nc所接收的控制电压信号v

set

即为第二电源输入端in2的电位。此时,控制电压信号v

set

为与第二电源输入端in2的电位相同(如v

set

为零电位,v

set

=0)时,则v

gs

+vr=0;随着第一电流i1的变大,vr也变大,相对之下v

gs

变小;当空乏型nmos的关闭条件v

gs

《-v

th

得以满足时,则会使主动开关单元110b关闭,从而抑制第一电流i1。

[0079]

再者,图3a的涌浪电流抑制电路10b或图3b的涌浪电流抑制电路10b1还包含单向

导通单元130b,单向导通单元130b例如包含二极管。在图3a或图3b中,单向导通单元130b提供的放电电流路径,其电路运作方式与图2a的涌浪电流抑制电路10a的单向导通单元130a的实施例相似,故不再赘述。

[0080]

又上述图2a、图3a、图3b中显示基于图1的涌浪电流抑制电路10的电路架构且主动开关单元为nmos时,涌浪电流抑制电路的各种实施例。然而,本发明的实现并不受此等示例限制。

[0081]

请参考图4,其为涌浪电流抑制电路的另一种实施方式的应用情景的示意框图。图4的涌浪电流抑制电路11与图1的涌浪电流抑制电路10同样可应用于一种电子装置以抑制电子装置输入电容(如电容性装置5)的电流大小。图4的涌浪电流抑制电路11与图1的涌浪电流抑制电路10的实施方式的差异在于,图4的涌浪电流抑制电路11耦接于第一电源输入端in1与电容性装置5之间,而且图4的涌浪电流抑制电路11所包括的主动开关单元110p以及电流检测单元120的排列方式与图1的涌浪电流抑制电路10中对应的元件的排列方式不同,尤其是电流检测单元120耦接于第一电源输入端in1与主动开关单元110p之间。

[0082]

电流检测单元120与主动开关单元110p串联,且用以根据流经的第一电流i1产生检测电压信号。当第一电流i1自第一电源输入端in1流入并通过电流检测单元120时,电流检测单元120产生检测电压信号。当检测电压信号大于或等于检测电压门槛值时,主动开关单元110p关闭,从而抑制第一电流i1。举例而言,电流检测单元120可以利用各种能依据流过电流检测单元120的电流而产生对应的电压信号以反应电流大小的元件来实现,例如电阻或其他元件。

[0083]

图4为适用于利用p型晶体管来实现主动开关单元的电路架构。以下基于图4的涌浪电流抑制电路11的电路架构,提出涌浪电流抑制电路的各种实施例。

[0084]

图5a为基于图4的涌浪电流抑制电路11的一个实施例的示意框图。如图5a所示,涌浪电流抑制电路10c包括开关控制单元100c、主动开关单元110c以及电流检测单元120c。举例而言,开关控制单元100c可以实现为包含电源电路或其他合适电路,以提供控制电压信号v

set

,其中控制电压信号v

set

例如为固定值。主动开关单元110c具有控制端nc、第一端n1及第二端n2。电容性装置5则耦接于主动开关单元110c的第一端n1与第二电源输入端in2与之间。电流检测单元120c耦接于第一电源输入端in1与主动开关单元110c的第二端n2之间。在图5a中,主动开关单元110c可以包含一个p型晶体管,例如p型mosfet(或简称pmos),如增强型pmos,故图5a为利用pmos来实现主动开关单元110c时的电路架构的实施例。此外,电流检测单元120c例如包含一个电阻来实现。

[0085]

在图5a的涌浪电流抑制电路10c的实施例中,利用pmos来实现主动开关单元110c,故当检测电压信号大于或等于检测电压门槛值时,主动开关单元110c的第二端n2与控制端nc之间的跨压(如晶体管的源极及栅极之间的电压v

sg

)无法达到主动开关单元110c的导通电压门槛值(如晶体管的导通电压门槛值-v

th

),以使主动开关单元110c关闭,从而抑制第一电流i1。

[0086]

此外,在图5a的涌浪电流抑制电路的实施例中,可通过调整电流检测单元120c中电阻的电阻值来限制最大电流,从而达到限流的功能。当检测电压信号vr大于或等于检测电压门槛值时,主动开关单元110c的第二端n2与控制端nc之间的跨压(如晶体管的源极及栅极之间的电压v

sg

)将无法达到主动开关单元110c的导通电压门槛值(如晶体管的导通电压

门槛值-v

th

),即使得增强型pmos的关闭条件v

sg

≤-v

th

得以满足,从而使主动开关单元110c关闭,以抑制第一电流i1。

[0087]

请参考图5b,其为基于图5a的涌浪电流抑制电路10c的实施例的波形示意图。于图5b的上方的波形示意当第一电源输入端in1与第二电源输入端in2接收的输入电源信号v

in

从零电位上升到一电压位准(如约380v)并维持定值时的波形。从上述涌浪电流抑制电路10c的主动开关单元110c的关闭条件的说明可知,在控制电压信号v

set

为固定值且大于v

sg

的状况下,随着第一电流i1的变大,流经电阻的电流ir变大(如图5b的中间的波形所示),因此vr也变大,相对之下v

sg

变小(如图2b的下方的波形为v

gs

,其相反为v

sg

)。当v

sg

《-v

th

时,使主动开关单元110c关闭,以抑制第一电流i1,如图5b的中间的波形所示,流经电阻的电流ir被抑制在预定的电流值(如23a)以下,从而提升电子装置在启动时的电路安全性。

[0088]

再次回到图5a的实施例中,涌浪电流抑制电路10c还包含单向导通单元130c,且单向导通单元130c与电流检测单元120c并联。单向导通单元130c具有提供电流路径的作用。具体来说,当电容性装置5放电时,有与上述第一电流i1的电流方向相反的第二电流i2将自第二电源输入端in2流入,且第二电流i2依序通过电容性装置5、主动开关单元110c及单向导通单元130c而流向第一电源输入端in1。单向导通单元130c例如包含一个二极管。此外,单向导通单元130c也具有保护主动开关单元110c的作用。当第二电流i

2-产生时,电流检测单元120c会产生反向电压。由于电流检测单元120c与单向导通单元130c并联,故单向导通单元130c将电流检测单元120c的反向电压限制为与二极管的跨压相同,从而使主动开关单元110c能避免承受过大的跨压而损坏的状况发生。再者,单向导通单元130c提供电流路径,使第二电流i2主要(或理想中完全)经由单向导通单元130c而流向第一电源输入端in1,从而减少了第二电流i2通过涌浪电流抑制电路10c时的功耗。

[0089]

如上,当图5a的涌浪电流抑制电路10c应用于如图4所述的电子装置中,当电子装置开启而使输入电源信号v

in

由零电位上升至预定的电压位准时,第一电流i1将自第一电源输入端in1流入,且第一电流i1依序通过电流检测单元120c、主动开关单元110c及电容性装置5而流向第二电源输入端in2,此时电容性装置5将开始充电,此第一电流i1的电流路径可定义为充电电流路径。反过来说,当图4的内部电路9需要自电容性装置5汲取电流时,第二电流i2将自第二电源输入端in2流入,且第二电流i2依序通过电容性装置5、主动开关单元110c及单向导通单元130c而流向第一电源输入端in1,此时电容性装置5将开始放电,此第二电流i2的电流路径可定义为放电电流路径。如此,图5a的涌浪电流抑制电路10c能因应电容性装置5充电或放电而提供合适的电流路径,从而使设置涌浪电流抑制电路10c的电子装置能得以正常的运作,也能提升电子装置在输入电源信号v

in

异常时的电路安全性。

[0090]

图6a为基于图4的涌浪电流抑制电路11的一个实施例的示意框图。图6a为利用空乏型pmos来实现主动开关单元时的电路架构的实施例。相较于图5a的涌浪电流抑制电路10c,图5a的涌浪电流抑制电路10c与图6a的涌浪电流抑制电路10d的差异在于,图6a的涌浪电流抑制电路10d使用空乏型pmos来实现主动开关单元110d。如图6a所示,涌浪电流抑制电路10d包括开关控制单元100d、主动开关单元110d、电流检测单元120d、单向导通单元130d。开关控制单元100d可以实现为包含电源电路或其他合适电路,以提供控制电压信号v

set

,例如控制电压信号v

set

大于v

sg

。主动开关单元110d具有控制端nc、第一端n1及第二端n2,电容性装置5耦接于第二电源输入端in2与主动开关单元110d的第一端n1之间,电流检测单元120d

耦接于主动开关单元110d的第二端n2与第二电源输入端in2之间。在图6a中,主动开关单元110d包含空乏型pmos,电流检测单元120d包含电阻。

[0091]

此外,在图6a的涌浪电流抑制电路10d的实施例中,可通过调整电流检测单元120d中电阻的电阻值来限制最大电流,从而达到限流的功能。当检测电压信号大v-r

于或等于检测电压门槛值时,主动开关单元110d的第二端n2与控制端nc之间的跨压(如晶体管的源极及栅极之间的电压v

sg

)将无法达到主动开关单元110d的导通电压门槛值(如晶体管的导通电压门槛值v

th

),即使得空乏型pmos的关闭条件v

sg

《v

th

得以满足,从而使主动开关单元110d关闭,以抑制第一电流i1。在一示例中,当控制电压信号v

set

为与第一电源输入端的电位相同时,则v

sg

+vr=0;随着第一电流i1的变大,vr也变大,相对之下v

sg

变小;当空乏型pmos的关闭条件v

sg

《v

th

得以满足时,则会使主动开关单元110d关闭,从而抑制第一电流i1。

[0092]

此外,图6b为基于图4的涌浪电流抑制电路11的另一个实施例的示意框图,其中图6b也是利用空乏型pmos来实现主动开关单元。相较于图6a的涌浪电流抑制电路10d,图6b的涌浪电流抑制电路10d1与图6a的涌浪电流抑制电路10d的差异在于,图6b的涌浪电流抑制电路10d1中不需使用开关控制单元来提供控制电压信号v

set

,控制端nc所接收的控制电压信号v

set

通过将控制端nc耦接至第一电源输入端in1来获得。如此一来,控制端nc所接收的控制电压信号v

set

即为第一电源输入端in1的电位。当控制电压信号v

set

为与第一电源输入端的电位相同时,则v

sg

+vr=0;随着第一电流i1的变大,vr也变大,相对之下v

sg

变小;当空乏型pmos的关闭条件v

sg

《v

th

得以满足时,则会使主动开关单元110d关闭,从而抑制第一电流i1。

[0093]

再者,图6a的涌浪电流抑制电路10d或图6b的涌浪电流抑制电路10d1还包含单向导通单元130d,单向导通单元130d例如包含二极管。在图6a或图6b中,单向导通单元130d提供的放电电流路径,其电路运作方式与图5a的涌浪电流抑制电路10c的单向导通单元130c的实施例相似,故不再赘述。

[0094]

又上述图5a、图6a、图6b中显示基于图4的涌浪电流抑制电路11的电路架构且主动开关单元为pmos时,涌浪电流抑制电路的各种实施例。然而,本发明的实现并不受此等示例限制。

[0095]

请参考图7,其为基于图1的涌浪电流抑制电路10的一个实施例的示意框图。如图7所示,涌浪电流抑制电路10e包括开关控制单元100e、主动开关单元110e以及电流检测单元120e。图7的涌浪电流抑制电路10e与基于图1的涌浪电流抑制电路10的其他实施例(如图2a)的涌浪电流抑制电路(如10a)的差异在于,图7的涌浪电流抑制电路10e中的电流检测单元120e电性耦接至开关控制单元100e,电流检测单元120e将检测电压信号传送至开关控制单元100e,开关控制单元100e依据检测电压信号而控制主动开关单元110e的开启或关闭。在本实施例中,开关控制单元100e耦接于主动开关单元110e的控制端nc与电流检测单元120e之间。当第一电流i1自第一电源输入端in1流入并通过电流检测单元120e时,电流检测单元120e产生检测电压信号;当检测电压信号大于或等于一检测电压门槛值时,开关控制单元100e根据检测电压信号控制主动开关单元110e关闭,从而抑制第一电流i1。

[0096]

开关控制单元100e可以根据检测电压信号来控制主动开关单元110e开启或关闭。例如,可利用图7的涌浪电流抑制电路10e需要限制的最大电流来配置电流检测单元120e,使最大电流流过电流检测单元120e时产生对应的代表最大电流流过的检测电压信号,并设定此条件下的检测电压信号对应的信号值或数值为检测电压门槛值。另一方面,开关控制

单元100e可被配置为依据检测电压信号是否大于或等于检测电压门槛值来决定是否将主动开关单元110e开启或关闭。若检测电压信号小于检测电压门槛值,则开关控制单元100e将主动开关单元110e开启;若检测电压信号大于或等于检测电压门槛值,则开关控制单元100e将主动开关单元110e关闭,从而抑制第一电流i1。

[0097]

开关控制单元100e将主动开关单元110e开启或关闭的实现方式有多种,例如开关控制单元100e通过一开关元件来暂停提供控制电压信号v

set

给主动开关单元110e,或例如开关控制单元100e改变控制电压信号v

set

的位准使主动开关单元110e不能导通。开关控制单元100e可包含产生控制电压信号的电源电路及控制电路,或包含控制电路以控制外部提供的控制电压信号。开关控制单元100e可以利用模拟电路、数字电路、逻辑电路或微控制器等任何合适的控制电路来实现。

[0098]

举例而言,主动开关单元110e可以包含一个或多个晶体管,如增强型nmos的类的nmos。电流检测单元120e例如是利用霍尔效应感测器(hall effect sensor)来实现,或其他能够依据流过电流检测单元120e的电流而产生对应的电压信号作为检测电压信号以反应电流大小的元件来实现。

[0099]

再者,图7的涌浪电流抑制电路10e还包含单向导通单元130e,单向导通单元130e例如包含二极管。图7的涌浪电流抑制电路10e的单向导通单元130e提供的放电电流路径,其电路运作方式与图2a的涌浪电流抑制电路10a的单向导通单元130a的实施例相似,故不再赘述。

[0100]

借此,当图7的涌浪电流抑制电路10e应用于如图1所述的电子装置中,电子装置开启的瞬间,输入电源信号v

in

由零电位升至预定的位准时,第一电流i1自第一电源输入端in1流入对电容性装置5充电,此第一电流i

1-为图7的涌浪电流抑制电路10e所具有的充电电流的路径。反过来说,当电容性装置5放电时,与第一电流i

1-的电流方向相反的第二电流i

2-于图7的涌浪电流抑制电路10e也具有放电电流的路径。如此,图7的涌浪电流抑制电路10e能因应电容性装置5充电或放电而提供合适的电流路径,使设置涌浪电流抑制电路10e的电子装置能得以正常的运作,也能提升电子装置在输入电源信号v

in

异常时的电路安全性。

[0101]

请参考图8,其为基于图4的涌浪电流抑制电路11的一个实施例的示意框图。如图8所示,涌浪电流抑制电路10f包括开关控制单元100f、主动开关单元110f以及电流检测单元120f。图8的涌浪电流抑制电路10f与图7的涌浪电流抑制电路10e的差异在于图8的涌浪电流抑制电路10f使用增强型pmos来实现主动开关单元110f,故其他元件及运作原理可参考图7的实施例来加以实现。在本实施例中,开关控制单元100f耦接于主动开关单元110f的控制端nc与电流检测单元120f之间。当第一电流i1自第一电源输入端in1流入并通过电流检测单元120f时,电流检测单元120f产生检测电压信号;当检测电压信号大于或等于一检测电压门槛值时,开关控制单元100f根据检测电压信号控制主动开关单元110f关闭,从而抑制第一电流i1。

[0102]

图8的涌浪电流抑制电路10f亦同样能够就电容性装置5提供充电电流的路径及放电电流的路径。

[0103]

再者,图8的涌浪电流抑制电路10f还包含单向导通单元130f,单向导通单元130f例如包含二极管。图8的涌浪电流抑制电路10f的单向导通单元130f提供的放电电流路径,其电路运作方式与图5a的涌浪电流抑制电路10c的单向导通单元130c的实施例相似,故不

再赘述。

[0104]

如此,图8的涌浪电流抑制电路10f能因应电容性装置5充电或放电而提供合适的电流路径,使设置涌浪电流抑制电路10f的电子装置能得以正常的运作,也能提升电子装置在输入电源信号v

in

异常时的电路安全性。

[0105]

在上述图2a、3a~3b、5a、6a~6b、7、8或其相关示例中,虽然主动开关单元(如110a、110b、110c、110d、110e、110f)示意利用一个晶体管来实现,然而主动开关单元也可以包含多个晶体管来实现。

[0106]

此外,在上述图2a、3a~3b、5a、6a~6b或其相关示例中,虽然电流检测单元(如120a、102b、102c、102d)示意利用一个电阻来实现,然而电流检测单元也可以包含多个串联或并联的电阻来实现。

[0107]

此外,在上述图2a、3a~3b、5a、6a~6b、7、8或其相关示例中,虽然示意单向导通单元(如130a、130b、130c、130d、130e、130f)利用一个二极管来实现,然而单向导通单元也可以包含多个串联或并联的二极管来实现。

[0108]

如上所述,涌浪电流抑制电路的实施例通过主动开关单元以及电流检测单元的协同运作,例如可设计合适的检测电压门槛值的大小,从而抑制第一电流。相较于在开机启动后,上述现有的电流抑制电路因开关(如继电器)开启而不能产生抑制涌浪电流的作用的状况,本发明的涌浪电流抑制电路的实施例,不受输入电源信号v

in

异常(如直流的输入电压瞬间降低至零电位、由零电位回升至原有直流位准,或电压位准多次大幅度跳动)的影响,在初始输入电源信号输入时及输入电源信号异常时皆能产生抑制涌浪电流的作用,故能提升电子装置在输入电源信号v

in

异常时的电路安全性。且依据本发明的实施例的涌浪电流抑制电路可使用相较于现有的电流抑制电路而言(如上述继电器)体积较小的电路元件来实现,有助于减少电子装置整体的体积。

[0109]

本发明在上文中已以较佳实施例公开,然而本领域技术人员应理解的是,所述实施例仅用于描绘本发明,而不应解读为限制本发明的范围。应注意的是,举凡与所述实施例等效的变化与置换,均应设为涵盖于本发明的范畴内。因此,本发明的保护范围当以权利要求书所界定的内容为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1