一种背靠背有源中点钳位型五电平变频器控制系统

1.本发明涉及电力电子技术领域,特别涉及一种背靠背有源中点钳位型五电平变频器控制系统。

背景技术:

2.随着对电机系统高效率,高性能的不断追求,多电平变频器逐渐成为人们研究的热点。多电平变频器控制灵活,电平数输出越多,越能得到接近于正弦波的输出波形。传统的变频器受到功率器件电压等级的限制无法运用在6kv及以上的高电压领域,此外,考虑到变频器电平数越多,其结构越复杂,控制难度越大,所以选择五电平作为高压领域工业应用的对象。工业领域上应用的五电平变频器按照拓扑结构可以分为电容钳位型、h桥级联型、二极管钳位型、模块组合型、层叠式多单元型和有源中点钳位型。有源中点钳位型五电平变频器既可以在运用在高压领域又具有电压等级高、输出功率大、效率高的特点。为了进一步提高有源中点钳位型五电平变频器在工业领域的运行性能,在此基础上提出了一种背靠背有源中点钳位型五电平变频器控制系统。

技术实现要素:

3.本发明要解决的技术问题是提供了一种背靠背有源中点钳位型五电平变频控制系统,dsp和fpga架构以及基于emif总线的通信能够满足相关的控制算法的实现和高速通信的设计要求。

4.本发明解决上述技术问题采用的技术方案是:一种背靠背有源中点钳位型五电平变频器控制系统,包括cpu控制和通信子系统、辅助控制子系统、ad采样子系统、核心控制子系统、单元控制子系统和监视操作子系统。cpu控制和通信子系统采用dsp和fpga架构与单元控制子系统和监视操作子系统、核心控制子系统进行双向通信和数据传输;辅助控制子系统采用fpga架构与cpu控制和通信子系统相连,将输入信号通过光纤传输给cpu,将cpu发出的信号和ad信号进行处理后输出;ad采样子系统功能单一,ad采样芯片和fpga组合实现将采集的电压和电流信号传输给cpu;核心控制子系统包含整流器和逆变器,实现整流控制和逆变器侧的矢量控制,接收cpu控制和通信子系统的指令又反馈自身的工作状态,同时采用dsp和fpga架构与单元控制子系统相连实现pwm信号传输;单元控制子系统采用fpga架构接受核心控制子系统的pwm信号并对其解码,以电信号的形式传输给驱动板,实现各桥臂pwm信号的输出,又通过高速光纤通道协议fcip(fibre channel frame over ip)将驱动板故障传输到核心控制子系统;监视操作子系统包含显示器、操作台、plc和上位机,监视操作子系统与cpu控制和通信子系统通过高速光纤通道协议fcip(fibre channel frame over ip)进行数据传输。

5.优选地,cpu控制和通信子系统采用ti公司的tms320c6455型数字处理器dsp作为核心处理器,采用xilinx公司的xc6slx9型fpga作为协处理器搭建采样数据缓存,实现数据流采集、预处理和缓存功能。dsp内部的cpu模块通过emif模块访问外部emif总线上设备的

存储空间fpga,实现系统数据的实时性传输。同时fpga通过高速数据光纤传输协议hsd-ftp外置ad采样控制子系统、辅助控制子系统和核心控制子系统。ad采样控制子系统采集信号输入fpga进行ad信号处理和16位动态随机存储器ip核集成模块dram ip core缓存。dsp在fpga完成数据处理后通过emif接口将数据读入dsp进行控制算法运算,并将结果通过6路da输出、多路数据通信、can总线和rs485接口上传至辅助控制子系统、核心控制子系统、上位机和plc。

6.优选地,辅助控制子系统也采用xilinx公司的xc6slx9型fpga作为主处理器。fpga通过高速光纤通道协议fcip(fibre channel frame over ip)外置cpu控制和通信子系统。fpga架构负责将输入信号通过高速光纤通道协议fcip(fibre channel frame over ip)传输给cpu,同时又对cpu的输出信号和da信号进行处理。

7.优选地,ad采样子系统采用adc芯片和fpga组合的架构方式。adc芯片选用ti公司的电机控制专用模数转换芯片ads7869,该芯片全差分输入有12路,采样频率高。一片ads7869芯片即可满足有源中点钳位型五电平逆变器在直流母线电容电压、三相悬浮电容电压、调制度等模拟量采样和转换的需求。fpga仍选用xilinx公司的xc6slx9型号,通过高速光纤通道协议fcip(fibre channel frame over ip)外置cpu控制和通信子系统。该系统只负责将采样数据经过ad处理传输给cpu。

8.优选地,核心控制子系统dsp和fpga架构也采用ti公司的tms320c6455型数字处理器dsp作为核心处理器,采用xilinx公司的xc6slx9型fpga作为协处理器。dsp通信外部扩展接口emif以外部存储器的形式访问fpga,通过can总线连接上位机实现主从数据通信。fpga通过高速光纤通道协议fcip(fibre channel frame over ip)外置辅助控制子系统和cpu控制和通信子系统,此外通过高速光纤通道协议fcip(fibre channel frame over ip)外置单元控制子系统。dsp接受辅助控制子系统和cpu的信号和指令并将自身工作状态反馈给cpu,dsp通过高速光纤通道协议fcip(fibre channel frame over ip)驱动产生pwm脉冲传输给单元控制子系统同时反馈故障信号。

9.优选地,单元控制子系统采用xilinx公司的xc6slx9型fpga作为主处理器。fpga通过高速光纤通道协议fcip(fibre channel frame over ip)外置核心控制子系统。该系统解码核心控制子系统发出的pwm信号,通过电信号对驱动板驱动从而实现各桥臂pwm信号的输出,同时对igbt监控并及时将故障状态传送给核心控制子系统。

10.本发明与现有技术相比的优点在于:

11.anpc五电平变频器控制系统间需要大量数据进行实时交换,对数据通信的快速性和准确性要求高,传统通信方式不能满足anpc五电平变频器控制系统之间数据高速通信的要求。本发明选择基于emif总线的通信模式,dsp和fpga可以很方便地进行大数据量、快速的数据传输,满足anpc五电平变频器控制系统间数据高速通信需求。

附图说明

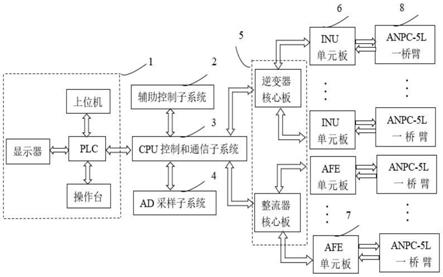

12.图1为背靠背有源中点钳位型五电平变频器控制系统结构图,其中,1为监视操作子系统,2为辅助控制子系统,3为cpu控制和通信子系统,4为ad采样子系统,5为核心控制子系统,6为单元控制子系统inu逆变单元板,7为afe整流单元板,8为anpc-5l一桥臂;

13.图2为cpu控制和通信子系统dsp+fpga架构示意图,其中,31为第一dsp芯片,32为

第一emif模块,33为第一fpga芯片;

14.图3为核心控制子系统dsp+fpga架构示意图,其中,51为第二dsp芯片,52为第二emif模块,53为第二fpga芯片;

15.图4为基于emif总线的dsp和fpga高速通信结构示意图,其中,9为第三dsp芯片,10为cpu模块,11为第三emif模块,12为emif总线,13为上行数据存储模块,14为上行数据状态模块,15为上行数据发送模块,16为下行数据存储模块,17为下行数据状态模块,18为下行数据接收模块。

16.图5为dsp与fpga之间通过emif总线通信示意图。

具体实施方式

17.本发明实施提出了一种背靠背有源中点钳位型五电平变频器控制系统,结合说明书附图对本发明实施例进行说明,应当理解,所描述的实施例仅限于说明和解释本发明,并不用于限定本发明且在不冲突的情况下,本技术中的实施例及实施例的特征可以相互组合。

18.如图1所示,本发明实施例提供了一种背靠背有源中点钳位型五电平变频器控制系统,包括cpu控制和通信子系统3、辅助控制子系统2、ad采样子系统4、核心控制子系统5、单元控制子系统inu逆变单元板6和afe整流单元板7、监视操作子系统1和anpc-5l一桥臂8。cpu控制和通信子系统3采用dsp和fpga架构与单元控制子系统和监视操作子系统1、核心控制子系统5进行双向通信和数据传输;辅助控制子系统2采用fpga架构与cpu控制和通信子系统3相连,将输入信号通过光纤传输给cpu,将cpu发出的信号和ad信号进行处理后输出;ad采样子系统4功能单一,ad采样芯片和fpga组合实现将采集的电压和电流信号传输给cpu;核心控制子系统5包含整流器和逆变器,实现整流控制和逆变器侧的矢量控制,接收cpu控制和通信子系统3的指令又反馈自身的工作状态,同时采用dsp和fpga架构与单元控制子系统相连实现pwm信号传输;单元控制子系统采用fpga架构接受核心控制子系统5的pwm信号并对其解码,以电信号的形式传输给驱动板,实现各桥臂pwm信号的输出,又通过高速光纤通道协议fcip(fibre channel frame over ip)将驱动板故障传输到核心控制子系统5;监视操作子系统1包含显示器、操作台、plc和上位机,监视操作子系统1与cpu控制和通信子系统3通过高速光纤通道协议fcip(fibre channel frame over ip)高速数据光纤传输协议经行数据传输。

19.如图2所示为cpu控制和通信子系统3的第一dsp芯片31和第一fpga芯片33的架构图,第一dsp芯片31采用ti公司的tms320c6455型数字处理器dsp芯片作为核心处理器,第一fpga芯片33采用xilinx公司的xc6slx9型fpga芯片作为协处理器搭建采样数据缓存,实现数据流采集、预处理和缓存功能。同时通过内部第一emif模块32访问外部emif总线上设备的存储空间第一fpga芯片33,实现系统数据的实时性传输。此外第一fpga芯片33通过高速光纤通道协议fcip(fibre channel frame over ip)外置ad采样子系统4、辅助控制子系统2和核心控制子系统5。ad采样控制子系统4采集信号输入第一fpga芯片33进行ad信号处理和16位动态随机存储器ip核集成模块dram ip核缓存。第一dsp芯片31在第一fpga芯片33完成数据处理后通过emif接口将数据读入第一dsp芯片31进行控制算法运算,并将结果通过6路da输出、多路数据通信、can总线和rs485接口上传至辅助控制子系统2、核心控制子系统

5、上位机和plc。

20.如图3所示为核心控制子系统dsp和fpga架构示意图,核心控制子系统中第二dsp芯片51采用ti公司的tms320c6455型数字处理器dsp芯片作为核心处理器,第二fpga芯片53采用xilinx公司的xc6slx9型fpga芯片作为协处理器。第二dsp芯片51通信外部扩展接口第二emif模块52以外部存储器的形式访问第二fpga芯片53,通过can总线连接上位机实现主从数据通信。第二fpga芯片53通过高速光纤通道协议fcip(fibre channel frame over ip)外置辅助控制子系统2和cpu控制和通信子系统3,此外通过高速光纤通道协议fcip(fibre channel frame over ip)外置单元控制子系统inu逆变单元板6和afe整流单元板7的单元控制子系统。第二dsp芯片51接受辅助控制子系统2和cpu的信号和指令并将自身工作状态反馈给cpu,第二dsp芯片51通过高速光纤通道协议fcip(fibre channel frame over ip)驱动产生pwm脉冲传输给单元控制子系统同时反馈故障信号。

21.如图4所示为基于emif总线12的dsp和fpga高速通信结构示意图,第三dsp芯片9内部的cpu模块10通过第三emif模块11访问外部emif总线12上设备的存储空间。fpga内部配置的本地总线用于将内部逻辑模块挂载到外部emif总线12上。fpga内部具有2个数据位宽32位、地址空间512的单双口ram包含一个读端口和一个写端口,分别用于实现所述上行数据存储模块的读写和下行数据存储模的读写。数据流从fpga经emif总线到第三dsp芯片9上行数据传输时,第三fpga和第三dsp芯片9同时操作,上行数据存储模块13的写数据、写地址、写使能连接上行数据发送模块15,用于写入数据,上行数据状态模块14的读数据、读地址、读使能连接本地总线,用于读取数据。上行数据存储模块13和上行数据状态模块14同时进行读写,上行数据发送模块15将要发送的并行数据流,连续不断写入上行数据存储模块13,写地址循环递增,上行数据状态模块14根据第三dsp芯片9的读取数据操作和上行数据发送模块15的写入数据操作,计算上行数据存储模块13已用存储空间大小。数据流从第三dsp芯片9经emif总线12到fpga下行数据传输时,下行数据存储模块16的写数据、写地址、写使能连接本地总线,用于写入数据,下行数据状态模块17的读数据、读地址、读使能连接下行数据接收模块18,用于读取数据。下行数据存储模块16和上行数据状态模块17同时进行读写,下行数据状态模块17根据第三dsp芯片9写入数据操作和下行数据接收模块18读取数据操作,计算下行数据存储模块剩余存储空间大小。同时,下行数据接收模块18读地址循环递增,读取下行数据存储模块16生成连续的并行数据流。

22.图5所示为dsp与fpga之间通过emif总线通信示意图,外部存储器总线(emif,external memory interface)总线主要的信号有6个,fpga侧信号包括:ace2,片选信号;aeclkout,时钟信号;asre,读使能;aswe,写使能;aed[63:0],64位数据总线;aea[19:0],20位地址总线(optional)。dsp侧包括:ce2,片选信号;eclkout,时钟信号;re,读使能;we,写使能;data[63:0],64位数据总线;addr[19:0],20位地址总线(optional)。上述dsp与fpga的六组信号一一连接。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1