用于终端设备的晶体管充电电路的制作方法

1.本实用新型涉及充电电路技术领域,具体涉及用于终端设备的晶体管充电电路。

背景技术:

2.在现有技术中由于智能电源管理和高集成度方面不断创新,目前电子产品逐渐微型化、功能性逐渐增强,使用时间延长,电子产品的小型化同时也限制了产品内的电池容量,如若充电电流过小时,产品的充电时间延长,增加的充电时间容易影响使用者对产品的体验感,当使用芯片进行开关充电时,过大的充电电流会影响电池寿命,同时过大的充电电流伴随有潜在的安全隐患。

技术实现要素:

3.为了解决上述问题,本实用新型提供了一种能够密切监测充电电流和电压,同时能够在循环充电的过程中,将充电电流和电压稳定在一个合适区间用于终端设备的晶体管充电电路。

4.为了到达上述目的,本实用新型设计的用于终端设备的晶体管充电电路,主要在于充电电路,充电电路包括vchg接口、电池b1、pnp三极管q1、nmos管q2与控制芯片u1,所述的充电电路中vchg接口与pnp三极管q1的发射极相连接,作为充电电路的输入端,pnp三极管q1的基极与nmos管q2的漏极相连接,nmos管q2的栅极作为充电电路的控制端,并与pnp三极管q1的发射极之间串联有电阻r1,nmos管q2的源极与控制芯片u1中设有的vdrive信号引脚相连接,nmos管q2的栅极与控制芯片u1中设有的vchg_d信号引脚相连接,pnp三极管q1的集电极连接有电阻r4,作为充电电路的输出端,且电阻r4与电池b1的正极相连接,电池b1的负极与控制芯片u1中设有的gnd信号引脚相连接。这种结构将nmos管q2的工作区设置在可变电阻区,pnp三极管q1的工作区设置在放大区,当vchg接口电压保持不变时,可以通过nmos管q2控制pnp三极管q1发射极电流,且pnp三极管q1集电极的电流通过pnp三极管q1发射极电流控制,从而通过nmos管q2的导通情况控制充电电路内的电流,同时通过控制芯片u1中vdrive电压值控制nmos管q2的导通程度,进而将充电电路内的充电电流和电压稳定在一个合适区间,且根据电池b1的电压值与充电电路内的充电电流,可以将充电电路分为预充电、恒流充、恒压充和涓流充多种充电模式。

5.进一步的方案是,所述的充电电路中vchg接口与控制芯片u1中设有的vchg_d信号引脚相连接,vchg接口与vchg_d信号引脚的接线中设有电阻r1,且nmos管q2的栅极与vchg_d信号引脚的接线中设有电阻r2,电阻r1与电阻r2配合构成充电电路的分压网络。这种结构通过电阻r1与电阻r2将vchg接口处的电压值分压,用于检测充电器是否插入,且电阻r2的设置同时保护了nmos管q2的栅极,防止浪涌大电流击穿q2栅极。

6.更进一步的方案是,所述的pnp三极管q1的基极与nmos管q2的漏极接线中部设有电阻r3构成保护电路。这种结构通过电阻r3的设置保护nmos管q2与控制芯片u1的vdrive引脚,电阻r3的设置同时能够衰减vchg端传导到nmos管q2的浪涌电流,从而保护nmos管q2与

控制芯片u1的vdrive引脚。

7.更进一步的方案是,所述的电阻r4两端分别与控制芯片u1中设有的vbat信号引脚与isense信号引脚连接构成充电电流检测电路。这种结构通过电流经过电阻r4时,产生的电压降落,具体为当电荷流过该小段电路释放或该小段电路吸收的电能大小,从而检测充电电流大小。

8.更进一步的方案是,所述的电池b1负极与gnd信号引脚的接线中部设有电阻r5,电阻r5的两端分别与控制芯片u1中设有的sensep信号引脚与sensen信号引脚连接,且sensep信号引脚与sensen信号引脚与充电电路的接线中分别设有电阻r6与电阻r7。这种结构通过电阻r5检测系统电路净流入或者净流出的电流大小,从而为充电电路中的电池b1电量显示提供硬件支持,并在电阻r5的两端设置电阻r6与电阻r7,进而为充电电流检测电路提供一个稳定的工作电源环境,同时能够起到消除干扰和误触发的作用。

9.更进一步的方案是,所述的电阻r1=100欧姆、电阻r2=10*1000欧姆、电阻r3=200欧姆、电阻r4=0.068欧姆、电阻r5=0.02欧姆、电阻r6=电阻r7=1000欧姆。这种结构通过在充电电路中设置的电阻,保证电路的可靠性。

10.本实用新型所设计的用于终端设备的晶体管充电电路,将pnp三极管q1的基极与nmos管q2的漏极之间电连接,同时将nmos管q2的源极与控制芯片u1的vdrive信号引脚连接,组成的电流控制回路根据nmos管q2的导通情况控制充电电路内的电流,从而将充电电路内的充电电流和电压稳定在一个合适区间,通过电流控制回路内设置的电阻r3与电阻r2保护nmos管q2与控制芯片u1的vdrive引脚,这种结构通过pnp三极管q1的集电极与电池b1之间设置的电阻r4,当充电电流经过电阻r4时,产生的电压降落,检测充电电路内的充电电流大小,同时密切监测充电电路内的充电电流和电压,能够在循环充电的过程中,将充电电流和电压稳定在一个合适区间。

附图说明

11.图1是用于终端设备的晶体管充电电路示意图。

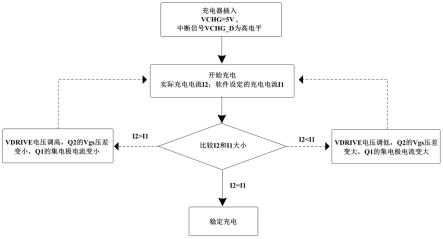

12.图2是用于终端设备的晶体管充电电路的充电流程图。

13.图3是用于终端设备的晶体管充电电路的充电测试结果图。

14.图4是不同的电压情况下,pnp三极管q1与nmos管q2的电压表。

15.图5是pnp三极管q1与nmos管q2的电压变化表。

具体实施方式

16.为更进一步阐述本实用新型为实现预定实用新型目的所采取的技术手段及功效,以下结合附图及较佳实施例,对依据本实用新型的具体实施方式、结构、特征及其功效,详细说明如后。

17.实施例1。

18.如图1所示,本实施例描述的用于终端设备的晶体管充电电路,所述的充电电路中vchg接口与pnp三极管q1的发射极相连接,作为充电电路的输入端,pnp三极管q1的基极与nmos管q2的漏极相连接,nmos管q2的栅极作为充电电路的控制端,并与pnp三极管q1的发射极之间串联有电阻r1,nmos管q2的源极与控制芯片u1中设有的vdrive信号引脚相连接,

nmos管q2的栅极与控制芯片u1中设有的vchg_d信号引脚相连接,pnp三极管q1的集电极连接有电阻r4,作为充电电路的输出端,且电阻r4与电池b1的正极相连接,电池b1的负极与控制芯片u1中设有的gnd信号引脚相连接。

19.所述的充电电路中vchg接口与控制芯片u1中设有的vchg_d信号引脚相连接,vchg接口与vchg_d信号引脚的接线中设有电阻r1,且nmos管q2的栅极与vchg_d信号引脚的接线中设有电阻r2,电阻r1与电阻r2配合构成充电电路的分压网络。

20.所述的pnp三极管q1的基极与nmos管q2的漏极接线中部设有电阻r3构成保护电路。

21.所述的电阻r4两端分别与控制芯片u1中设有的vbat信号引脚与isense信号引脚连接构成充电电流检测电路。

22.所述的电池b1负极与gnd信号引脚的接线中部设有电阻r5,电阻r5的两端分别与控制芯片u1中设有的sensep信号引脚与sensen信号引脚连接,且sensep信号引脚与sensen信号引脚与充电电路的接线中分别设有电阻r6与电阻r7。

23.所述的电阻r1=100欧姆、电阻r2=10*1000欧姆、电阻r3=200欧姆、电阻r4=0.068欧姆、电阻r5=0.02欧姆、电阻r6=电阻r7=1000欧姆。

24.所述的充电电路中充电电流可调整范围为100ma-icmax,其中icmax为q1的最大集电极电流。

25.如图2所示,用于终端设备的晶体管充电电路内的电流控制回路调整充电电流的步骤如下:

26.首先假设系统设定的充电电流值大小为i1,如果在实际充电过程中,充电电流发生波动,变为i2;

27.当实际充电电流i2大于设定充电电流i1时,则控制芯片u1调高vdrive的电压值,此时nmos管q2的栅源电压差vgs变小,nmos管q2导通程度减弱,rds变大,引起pnp三极管q1的ieb电流降低(本电路pnp三极管q1工作在放大区,ic=β*ieb),实际充电电流i2不断降低,直到调整到i2=i1为止,vdrive电压值不再变化。

28.当实际充电电流i2小于设定的充电电流i1时,则控制芯片u1调低vdrive的电压值,此时nmos管q2的栅源电压差vgs变大,nmos管q2导通程度增强,rds变小,引起pnp三极管q1的ieb电流增加,(本电路pnp三极管q1工作在放大区,ic=β*ieb),实际充电电流i2不断增加,直到调整到i2=i1为止,vdrive电压值不再变化。

29.如图3所示,当电池b1的最大电池电压为4.35v时,充电电路设置为1000ma时的充电测试结果:

30.当电池电压低于3.45v时,充电电流在400ma左右,为预充电阶段,此阶段较小的充电电流可以防止出现电池过热现象,保护电池,

31.当电池电压3.45v

‑‑

4.2v之间时,充电电流在1000ma左右,为恒流充电阶段,此阶段充电速度最快,

32.当电池电压达到4.2v时,充电过程进入恒压充电阶段,充电电流逐渐减小到零,电池充满到4.35v。此阶段充电电流逐步减小,有利于电池电压充分充满。

33.如图4和图5所示,充电电路在不同的充电电压情况下,pnp三极管q1与nmos管q2的电压值情况不同。

34.当pnp三极管q1的发射极电压为4.67v时,pnp三极管q1的集电极电压为3.82v,pnp三极管q1的基极电压为3.95v,nmos管q2的漏极电压为3.24v,nmos管q2的栅极电压为4.5v,nmos管q2的源极电压为3.25v;pnp三极管q1的集电流或充电电路内的充电电流为800ma;

35.当pnp三极管q1的发射极电压为4.96v时,pnp三极管q1的集电极电压不变,pnp三极管q1的基极电压值为4.33v,nmos管q2的漏极电压值为3.63v,nmos管q2的栅极电压为4.84v,nmos管q2的源极电压为3.61v;pnp三极管q1的集电流或充电电路内的充电电流为803ma;

36.当pnp三极管q1的发射极电压为5.2v时,pnp三极管q1的集电极电压为保持不变,pnp三极管q1的基极电压为4.56v,nmos管q2的漏极电压为3.86v,nmos管q2的栅极电压为5.03v,nmos管q2的源极电压为3.79v;pnp三极管q1的集电流或充电电路内的充电电流为810ma。

37.当pnp三极管q1的发射极电压保持5.07v不变时,pnp三极管q1的集电极电压为3.23v,pnp三极管q1的基极电压为4.56v,nmos管q2的漏极电压为4.1v,nmos管q2的栅极电压为4.92v,nmos管q2的源极电压为4.88v;pnp三极管q1的集电流或充电电路内的充电电流为800ma;

38.当pnp三极管q1的发射极电压保持5.07v不变时,pnp三极管q1的集电极电压为3.46v,pnp三极管q1的基极电压为4.5v,nmos管q2的漏极电压为3.95v,nmos管q2的栅极电压不变,nmos管q2的源极电压为3.94v;pnp三极管q1的集电流或充电电路内的充电电流为800ma保持不变。

39.以上所述,仅是本实用新型的较佳实施例而已,并非对本实用新型作任何形式上的限制,虽然本实用新型已以较佳实施例揭示如上,然而并非用以限定本实用新型,任何本领域技术人员,在不脱离本实用新型技术方案范围内,当可利用上述揭示的技术内容做出些许更动或修饰为等同变化的等效实施例,但凡是未脱离本实用新型技术方案内容,依据本实用新型的技术实质对以上实施例所作的任何简介修改、等同变化与修饰,均仍属于本实用新型技术方案的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1