一种基于开关电流积分器的纹波控制Buck变换器

一种基于开关电流积分器的纹波控制buck变换器

技术领域

1.本发明涉及集成电路领域与开关电源领域,更具体来说,涉及纹波控制恒定导通时间(ripple-based constant on-time,rb-cot)模式buck变换器电路。

背景技术:

2.基于纹波的恒定导通时间(ripple-based constant on-time,rb-cot)控制方式,需要输出电容的等效串联电阻(esr)足够大来提供足够的电流信息,以此避免出现次谐波振荡。通常情况下,输出电容与输出电容的esr的乘积要大于导通时间的一半。较大的esr会使得重负载下的效率降低,同时增加输出电压的纹波。为了提高效率以及减低输出电压纹波,商业电源管理产品通常更倾向于使用esr低、寿命长的陶瓷电容。因此,为了使rb-cot控制模式能在使用低esr输出电容时正常工作,国内外的研究团队提出了多种方法。

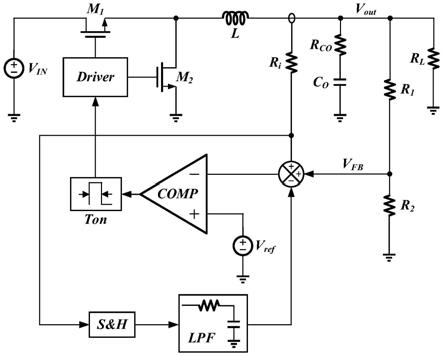

3.一种方法是采样电感电流叠加到反馈电压上,但是采样的电感电流的直流分量会引起输出电压精度降低,通常需要一个直流分量提取电路来将电感电流纹波的直流分量抵消掉。ti公司的dcap-3控制方式利用采样保持电路,在每个开关周期采样注入纹波信号的谷值电压,进而消除电感电流纹波注入带来的输出电压直流误差。该种控制方式如图1所示,采样保持得到的注入纹波谷值电压需要被低通滤波器lpf滤波之后才能用于消除注入纹波的直流分量。通常为了保证系统的稳定性,lpf的-3db带宽要远低于环路截止频率,即采样保持环路的响应速度要低于控制环路的响应。因此,当负载阶跃时,输出电压的恢复时间将由lpf决定。当控制器的开关频率可变,如果按照最高开关频率来设计lpf,那么当开关频率切换到低频时,采样保持环路的响应速度过快将引起整个控制环路的不稳定。因此,需要按照最低开关频率来设计lpf。但是当开关频率切换到高频后,用于消除直流分量的估值电压信号上升速度将被lpf限制,从而限制输出电压的恢复速度。

技术实现要素:

4.针对上述采样保持精度提升方法不能兼顾响应速度和稳定性的不足之处,本发明提出了一种基于开关电流积分器的纹波控制buck变换器。利用开关电流积分器来替代固定带宽的低通滤波器lpf,实现自适应开关频率的低通滤波的功能。有效优化了变换器在不同开关频率下的响应速度与稳定性。

5.本发明的技术方案为:

6.一种基于开关电流积分器的纹波控制buck变换器,包括cot控制主环路和直流分量提取电路。

7.所述cot控制主环路包括第一开关管、第二开关管、功率电感、采样电阻、输出电容、第一反馈电阻、第二反馈电阻、驱动模块、ton计时模块、环路比较器和第一加法器。

8.第一开关管的栅极连接到驱动模块的输出端,其漏极连接所述buck变换器的输入电压源,其源极连接第二开关管的漏极并连接到功率电感的一端;

9.功率电感的另一端连接所述buck变换器的输出端;

10.第二开关管的源极连接功率地;

11.输出电容连接到所述buck变换器的功率地和输出端之间;

12.第一反馈电阻与第二反馈电阻串联并连接到所述buck变换器的功率地和输出端之间,其串联节点连接到第一加法器的一个正输入端;

13.采样电阻采样电感电流并连接到第一加法器的一个正输入端;

14.环路比较器的负输入端连接至第一加法器的输出,正输入端连接至基准电压源,其输出端连接到ton计时模块的输入端;

15.ton计时模块的输出端连接到驱动模块的输入端。

16.所述直流分量提取电路包括第一采样保持单元、lpf模块和开关电流积分器。

17.第一采样保持单元的输入端接上述采样电阻的输出端,其输出端接开关电流积分器的输入端;

18.lpf模块的输入端接开关电流积分器的输出端,其输出端接上述第一加法器的一个负输入端;

19.具体的,开关电流积分器包括第一增益单元、第二采样保持单元、第二加法器、第三采样保持单元和第二增益单元。

20.第一增益单元的输入端连接至上述第一采样保持单元的输出端,其输出端连接到第二加法器的一个输入端和第二采样保持单元,其增益系数为aπ/(1+aπ),其中a为大于零小于一的实数;

21.第二采样保持单元的输出端连接至第二加法器的一个输入端;

22.第二加法器的输出端连接到上述lpf模块的输入端和第三采样保持单元输入端;

23.第二增益单元的输入端连接至第三采样保持单元的输出端,其输出端连接至第二加法器的一个输入端,其增益系数为(1-aπ)/(1+aπ),其中系数a与第一增益单元的增益系数中相同。

24.所述开关电流积分器及lpf模块的实施例包括第一pmos管、第二pmos管、第三pmos管、第四pmos管、第五pmos管、第六pmos管、第七pmos管、第八pmos管、第九pmos管、第十pmos管、第十一pmos管、第十二pmos管、第十三pmos管、第十四pmos管、第一nmos管、第二nmos管、第三nmos管、第四nmos管、第一电阻、第二电阻、第一电容、第二电容、第三电容、第一开关、第二开关和第一npn管。

25.具体的第一pmos管的栅极作为信号输入端,其漏极接地,其源极接第二pmos管的漏极和第一电阻的一端;

26.第一电阻的另一端接第一npn管的基极和第一电容的一端,第一电容的另一端接地;

27.第一npn管的发射极接第二电阻的一端,其集电极接第四pmos管的栅极、第四pmos管的漏极、第六pmos管的栅极和第八pmos管的栅极,第二电阻的另一端接地;

28.第三pmos管的漏极接其栅极、第四pmos的源极、第七pmos管的栅极和第一开关的一端,其源极接电源vdd;

29.第五pmos管的源极接电源vdd,其栅极接第一开关的另一端,其漏极接第六pmos管的源极,第二电容的接在电源和第五pmos管的栅极;

30.第七pmos管的源极接电源vdd,漏极接第八pmos管的源极;第八pmos管的漏极接第

六pmos管的漏极、第十pmos管的漏极、第三nmos管的栅极、第一nmos管的漏极和栅极;

31.第九pmos管的源极接电源vdd,其栅极接第二开关的一端,其漏极接第十pmos的源极;第三电容接在电源vdd和第九pmos管的栅极;

32.第十一pmos管的源极接电源vdd,其栅极和漏极接在一起并连接至第二开关的另一端、第十二pmos管的源极和第十三pmos管的栅极;

33.第十二pmos管的栅极接其漏极、第十pmos管的栅极、第十四pmos管的栅极和第三nmos管的漏极;

34.第十三pmos管的源极接电源vdd,其漏极接第十四pmos管的源极,第十四pmos管的漏极作为输出端;

35.第二nmos管栅极和漏极接第一nmos管的源极,其源极接地;第四nmos管的源极接地,其栅极接第二nmos管的栅极,其漏极接第三nmos管的源极。

36.本发明的有益效果为:本发明采用开关电流积分器替换传统架构中的固定rc滤波器,在不同开关频率下,开关电流积分器自动调节自身的带宽,其带宽与变换器的开关频率成正比。可以在不同开关频率下兼顾响应速度和稳定性,使得buck变换器在高开关频率下的响应速度不受固定rc滤波器限制,提升buck变换器的响应速度。

附图说明

37.图1传统dcap-3控制模式dc-dc buck变换器框图;

38.图2为本发明提出的一种基于开关电流积分器的纹波控制buck变换器;

39.图3为本发明中开关电流积分器在实施例中的具体电路图;

40.图4为本发明提出的buck变换器和传统dcap-3架构的buck变换器在260khz开关频率下,负载阶跃时输出电压、电感电流和负载电流的仿真波形对比图;

41.图5为本发明提出的buck变换器和传统dcap-3架构的buck变换器在1.0mhz开关频率下,负载阶跃时输出电压、电感电流和负载电流的仿真波形对比图。

具体实施方式

42.下面结合附图和具体实施例对本发明的技术方案进行详细的描述:

43.附图2为本发明所提出的一种基于开关电流积分器的纹波控制buck变换器的电路框图,本发明提出的buck变换器包括cot控制主环路和直流分量提取电路。cot控制主环路包括第一开关管m1、第二开关管m2、功率电感l、采样电阻ri、输出电容co、第一反馈电阻r1、第二反馈电阻r2、驱动模块driver、ton计时模块、环路比较器comp和第一加法器。电阻r

l

是buck变换器的负载电阻,co是buck变换器的输出电容,r

co

是co的等效串联电阻。

44.开关管m1和m2连接在电源和功率地之间,其连接处通过功率电感l连接到buck变换器的输出端v

out

。输出电容co和其等效串联电阻r

co

接在功率地和buck输出端之间。第一反馈电阻r1与第二反馈电阻r2串联,其串联节点得到与v

out

成正比的电压信息v

fb

。采样电阻ri采样电感电流,并通过第一加法器与电压信息v

fb

相叠加。环路比较器comp的负输入端接基准电压v

ref

,其正输入端接第一加法器的输出。环路比较器comp通过比较其正负输入端电压得到导通时间控制信号,进而控制ton计时模块产生导通时间ton。驱动模块driver前接ton计时模块,输出控制开关管m1和m2导通的栅极信号。

45.直流分量提取电路由第一采样保持单元、开关电流积分器和lpf模块构成。采样电阻ri采样电感电流得到电感电流纹波,经过第一采样保持单元后,得到电感电流纹波当前周期的谷值电压信息x[n]。开关电流积分器对x[n]进行滤波处理之后,得到谷值电压信息y[n]。y[n]在通过lpf模块后输入到第一加法器的负输入端,以此来消除采样电阻ri采样得到的电感电流纹波的直流值,最终提升输出电压的精度。

[0046]

开关电流积分器包括第一增益单元、第二采样保持单元、第二加法器、第三采样保持单元和第二增益单元。第一增益单元的增益系数为aπ/(1+aπ),第二增益单元的增益系数为(1-aπ)/(1+aπ),其中a为大于零小于一的实数。当前周期的谷值电压信息x[n]经过第二采样保持单元得到上一周期谷值电压信息x[n-1],第二加法器的输出端为当前周期的输出结果为y[n],y[n]经过第三采样保持单元得到上一周期的输出结果为y[n-1]。当前周期的谷值电压信息x[n]与上一周期谷值电压信息x[n-1]的和被第一增益单元缩小后,输入到第二加法器中;同样,上一周期的输出结果为y[n-1]被第二增益单元缩小后,输入到第二加法器中。第二加法器将两个输入进行叠加得到输出y[n]。开关电流积分器的作用就是实现一个低通滤波的功能。开关电流积分器电路将当前周期和前一周期的谷值电流信号累加,并引入反馈环路调控,最终使得输出信号逐次逼近输入信号。这个逐次逼近的过程所起到的效果类似于低通滤波的效果。y[n]的表达式如下:

[0047][0048]

下面结合本实施例的工作原理来进一步描述本发明的技术方案:

[0049]

附图3为开关电流积分器和lpf模块的实施例电路图。第一pmos管mp1和第二pmos管mp2构成升压电路,将采样保持得到的谷值电压信息vx[n]抬升一个栅源电压。第一电阻r1与第一电容c1构成lpf模块,其带宽设置较高,主要在高开关频率下起作用,进一步优化瞬态响应。第一npn管q1和第二电阻r2构成一个v-i转换器,vx[n]经升压后被其转换成电流x[n]。第三pmos管mp3和第四pmos管mp4都成二极管连接形式,第一开关s1和第二电容c2采样保持第三pmos管mp3的栅极电压,通过第五pmos管mp5和第六pmos管mp6镜像成信号k

·

x[n-1],k=aπ/(1+aπ)。同样,通过第七pmos管mp7和第八pmos管mp8镜像成信号k

·

x[n],k=aπ/(1+aπ)。第一nmos管mn1和第二nmos管mn2,第三nmos管mn3第四nmos管mn4构成电流镜。第二开关s2和第三电容c3采样保持第十一pmos管mp11的栅极电压,通过第九pmos管mp9和第十pmos管mp10镜像成信号(1-2k)

·

y[n-1],k=aπ/(1+aπ)。最终电流k

·

x[n-1]、k

·

x[n]和(1-2k)

·

y[n-1]在mn1的漏端叠加,并通过mn1、mn2、mn3、mn4、mp11、mp12、mp13和mp14构成的电流镜镜像到下一级。在每个第一开关管m1导通周期开启之前,开关s1和s2导通一段较短时间。开关电流y[n]的表达式如下:

[0050]

y[n]=k

·

x[n]+k

·

x[n-1]+(1-2k)

·

y[n-1]

ꢀꢀꢀꢀꢀ

(2)

[0051]

对式(2)z变换可得表达式如下:

[0052][0053]

对式(3)双线性变换可得表达式如下所示,式中f

sw

为开关频率。

[0054][0055]

可见本发明中的开关电流积分器的带宽与开关频率成正比,有效解决了传统架构中采用固定带宽的lpf限制响应速度的问题。

[0056]

利用仿真软件对本例的方法进行仿真分析,结果如下。

[0057]

附图4为本发明提出的buck变换器和传统dcap-3架构的buck变换器在260khz开关频率下,负载阶跃时输出电压、电感电流和负载电流的仿真波形对比图。仿真条件:输入电压v

in

=12v,输出电压v

out

=1.8v,电感值l=2.2uh,电容值co=120uf(等效串联电阻为0.1mω),开关频率260khz。在0.7ms处负载电流由2a阶跃变化到4a,在0.9ms处负载由4a阶跃变化到2a。从图4可以看出,两种架构都有稳定的响应波形,并且响应速度相当。

[0058]

图5为本发明提出的buck变换器和传统dcap-3架构的buck变换器在1.0mhz开关频率下,负载阶跃时输出电压、电感电流和负载电流的仿真波形对比图。仿真条件:输入电压v

in

=12v,输出电压v

out

=1.8v,电感值l=2.2uh,电容值co=29uf(等效串联电阻为0.1mω),开关频率1.0mhz。在0.7ms处负载电流由2a阶跃变化到4a,在0.9ms处负载由4a阶跃变化到2a。从图5可以看出,本发明相比于传统架构,输出电压的恢复时间缩短了约20μs。

[0059]

从上述具体实施方式可知,本发明提出的一种基于开关电流积分器的纹波控制buck变换器有效的提升了高开关频率下瞬态响应速度,并在全开关频率范围内很好的兼顾了响应速度和稳定性。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1