SIC-MOSFET并联均流电路及其控制方法与流程

mosfet的漏极连接母线电压,i个sic-mosfet的源极与所述i个寄生电感的第一端连接,i个寄生电感的第二端接地,i个sic-mosfet的栅极与所述i组驱动回路连接。

7.优选地,所述驱动回路包括驱动电阻和信号开关,该驱动电阻的第一端作为驱动回路的输入端,驱动电阻的第二端与信号开关的漏极相连,所述信号开关的源极作为驱动回路的输出端与sic-mosfet的栅极相连,所述信号开关的栅极与所述控制模块的io口相连。

8.进一步地,所述电阻网络模块还包括用于对所述控制模块的驱动信号进行功率放大的推挽电路。

9.优选地,所述推挽电路包括电源正极、n-mosfet功率管、p-mosfet功率管以及负电压,所述电源正极与n-mosfet功率管的漏极相连,n-mosfet功率管的源极与p-mosfet功率管的漏极相连并作为推挽电路的信号输出端,该信号输出端与所述i组驱动回路的输入端相连,所述p-mosfet功率管的源极与负电压相连,所述n-mosfet功率管的栅极和p-mosfet功率管的栅极的连接点作为推挽电路的信号输入端。

10.进一步地,所述电阻网络模块还包括放电回路,所述放电回路包括二极管和泄放电阻,所述二极管的正极端与所述驱动电阻的第二端和所述信号开关的漏极相连,二极管的负极端与所述泄放电阻的第一端相连,泄放电阻的第二端与所述驱动电阻的第一端和推挽电路的信号输出端相连。

11.进一步地,所述检测模块包括电阻、检测电容、比较器和基准电压,所述电阻的第一端与所述sic-mosfet的源极和所述寄生电感的第一端相连,电阻的第二端与比较器的正输入端和检测电容的正极端相连,所述检测电容的负极端接地,所述基准电压与比较器的负输入端相连,所述比较器的输出端与所述控制模块相连。

12.进一步地,所述控制模块包括pwm_driver脉冲发生模块、计数模块、判断模块和io口使能模块,所述pwm_driver脉冲发生模块在系统供电后运行,所述计数模块在接收到检

测模块输送的窄脉冲pwm-i后开始执行,所述判断模块在计数模块结束后开始执行,并根据判断模块的判断结果来执行所述io口使能模块。

13.优选地,所述i个寄生电感的动态参数为电势差。

14.本发明还提供一种sic-mosfet并联均流控制方法,该控制方法基于上述驱动电阻补偿型sic-mosfet并联均流电路所述控制方法包括以下步骤:s1、控制模块通过pwm_driver脉冲发生模块发送pwm_driver来驱动sic-mosfet并联模块中的i个sic-mosfet导通;s2、sic-mosfet并联模块中的i个寄生电感随着sic-mosfte的导通形成电势差;检测模块检测、量化i个寄生电感的动态参数,并向控制模块输送窄脉冲pwm-i,窄脉冲pwm-i的持续时间为sic-mosfet的开通时间;s3、在检测到pwm_driver的上升沿后,控制模块的计数模块开始计数,将检测模块的窄脉冲pwm-i的高电平时间进行量化,在检测到pwm_driver的下降沿后,结束计数;s4、在计数模块结束后,判断模块将i个寄生电感送来的动态参数进行排序,以最小的计数结果为标准,pwm_driver脉冲发生模块控制sic-mosfet的开通或关断,将其他sic-mosfet的驱动电阻减小以减短sic-mosfet的上升沿时间。

15.由以上技术方案可知,本发明通过检测模块对寄生电感的动态参数进行测量和量化并输出窄脉冲pwm-i,控制模块将不同寄生电感的计数结果进行排序,以最小的计数结果为标准,将计数结果越大的sic-mosfet导通更多的驱动电阻,使该sic-mosfet的驱动电阻值减小,可以减短其开通时间,向计数结果最小的sic-mosfet上升沿时间逼近,提升了流过各sic-mosfet的电流均衡度。

附图说明

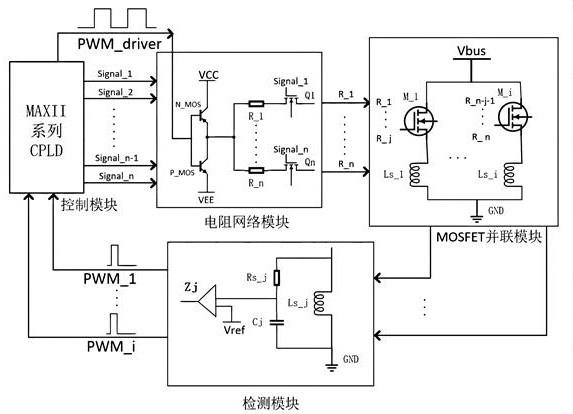

16.图1为本发明的均流电路总体结构示意图;图2为本发明的电阻网络模块电路图;图3为本发明的控制模块总体流程图;图4为本发明的控制模块中pwm_driver脉冲发生模块的流程图;图5为本发明的控制模块中计数模块的流程图;图6为本发明的控制模块中判断模块和io口使能模块的流程图;图7为本发明控制方法总体流程图。

具体实施方式

17.下面结合附图对本发明的一种优选实施方式作详细的说明。

18.如图1所示,本发明提供一种驱动电阻补偿型的sic-mosfet并联均流电路,包括

mosfet开通,电源正极的电流远远大于控制模块的输出电流,增强了驱动能力;在驱动信号pwm_driver为低电平时,即sic-mosfet关闭时,n-mosfet功率管关闭,p-mosfet功率管导通,加快抽走sic-mosfet的栅极寄生电容电荷,从而减小了关断时间,减小了交叉损耗。

26.放电回路包括二极管和泄放电阻,二极管的正极端与驱动电阻的第二端和信号开关的漏极相连,二极管的负极端与泄放电阻的第一端相连,泄放电阻的第二端与驱动电阻的第一端和推挽电路的信号输出端相连。

27.由于二极管的负极端指向远离sic-mosfet的一端,且泄放电阻小于驱动电阻,于是在sic-mosfet关断时,相较于开通阶段,电阻更小,可以更快速关断功率管;而在功率管开通阶段,驱动回路的电流不足以击穿二极管,于是在此阶段,泄放电阻不发挥作用。

28.如图1所示,检测模块包括电阻、检测电容、比较器和基准电压,电阻的第一端与sic-mosfet的源极和寄生电感的第一端相连,电阻的第二端与比较器的正输入端和检测电容的正极端相连,检测电容的负极端接地,基准电压与比较器的负输入端相连,比较器的输出端与控制模块相连。

29.sic-mosfet开通时刻,其源极连接的寄生电感会感应出电势差,电势差大小随电流变化率成正比,该电势差持续的时间代表了电流变化的时间,即代表了sic-mosfet开通时间;该电势差与基准电压通过比较器进行比较,比较器的输出结果是一个稳定的脉冲;sic-mosfet并联模块的每个sic-mosfet都对应有一个检测模块,每个检测模块输出脉冲宽度的不同,即代表了每个功率管开通时间的不同。

30.如图3所示,本发明的控制模块采用maxii系列的cpld,其包括pwm_driver脉冲发生模块、计数模块、判断模块和io口使能模块,pwm_driver脉冲发生模块在系统供电后运行,计数模块在接收到检测模块输送的窄脉冲pwm-i后开始执行,所述判断模块在计数模块结束后开始执行,并根据判断模块的判断结果来执行io口使能模块。

31.在功率管关断时刻也会有检测模块送来的脉冲信号,设计一个固定时间的使能信号,可以避免计数紊乱,故按照此时序进行设计才可以保证计数模块的输出结果为功率管开通时间内的动态参数,保证了该控制系统的准确性。

32.如图4所示,本优选实施例中,pwm_driver脉冲发生模块包括系统时钟clk、全局复

位rst_n、累加器counter和标志位en。系统时钟clk由100mhz晶振提供,全局复位rst_n为按键复位,累加器counter在每个时钟上升沿进行自加1,随着累加器counter数值的变化,标志位en也随之翻转,最终输出pwm_driver。

33.当需要输出pwm_driver的频率为yhz时,每个pwm_driver周期需要系统晶振clk循环100m/y次,于是可以根据需要的占空比来分割100m/y,即若需要50%占空比,设置当累加器counter等于100m/(2y)时,标志位en进行翻转,在累加器counter等于100m/y后置零,以上可以实现输出频率为yhz,占空比为50%的pwm波。

34.如图5所示,计数模块包括系统时钟clk、全局复位rst_n、驱动波形pwm_driver、检测模块形成的窄脉冲pulse、计数器cnt和计数使能标志位enable。pwm_driver脉冲发生模块发出pwm_driver波形后,计数模块检测到pwm_driver波形上升沿,之后将计数使能标志位enable置1;在计数使能标志位enable置1期间,当接收到检测模块送来的窄脉冲pulse后,计数器cnt的值在系统时钟clk一个周期内递增加1;在检测到计数使能标志位enable的下降沿后,结束计数。

35.如此,在检测pwm_driver波形上升为高电平时刻,认为驱动回路在往sic-mosfet栅极充电,在超过功率管阈值电压后,功率管开始导通,此时之前介绍的检测模块开始输出波形,在计数模块内部通过分频产生计数使能标志位enable,该标志位在检测到pwm_driver上升沿pose_pwm_driver后置1,在pose_pwm_driver置1的时间内计数器cnt进行计数,该时间大于功率管上升沿时间,小于半个pwm_driver周期时间,这样可以保证计数器cnt的最终值只量化单个上升沿时间。

36.如图6所示,判断模块和io口使能模块包括i个检测模块形成的窄脉冲计数结果和n个io口,n个io口分别对应连接n个信号mos,从而控制n个驱动电阻。

37.每个sic-mosfet开通的时间都会被计数、量化,最终得到的数值都会在判断模块中被排序,以最短的开通时间为标准,即以最小的计数值为标准,将越大数值对应的一组电阻网络模块开通更多的信号mos,即将对应的io口由低电平变成高电平;由于在电阻网络模块中,各驱动回路为并联设计,故开通越多的信号mos会使某个sic-mosfet的驱动电阻越小,这样会加快该sic-mosfet的开通速度,使电流不均衡度减小,且降低了交叉损耗。

38.如图7所示,本发明还提供一种sic-mosfet并联均流控制方法,该控制方法基于上述驱动电阻补偿型sic-mosfet并联均流电路,控制方法包括以下步骤:s1、系统通电后,首先控制模块中的pwm_driver脉冲发生模块开始驱动推挽电路,使sic-mosfet并联模块导通;s2、sic-mosfet并联模块中的i个寄生电感随着sic-mosfte的导通形成电势差;检测模块检测、量化i个寄生电感的动态参数,并向控制模块的io口输送窄脉冲pwm-i,窄脉冲pwm-i的持续时间为sic-mosfet的开通时间;s3、在检测到pwm_driver的上升沿后,计数模块设置的计数使能标志位enable置1,开始计数,将检测模块的窄脉冲pwm-i的高电平时间进行量化,在检测到pwm_driver的下降沿后,结束计数;

s4、在计数模块结束后,判断模块将i个寄生电感送来的动态参数进行排序,以最小的计数结果为标准,pwm_driver脉冲发生模块控制sic-mosfet的开通或关断,将其他sic-mosfet的驱动电阻减小以减短sic-mosfet的上升沿时间。

39.如此,以上步骤共同组成了一个完整的控制过程,外部只需给系统供电,系统便可以自主完成调节sic-mosfet并联模块在开启时的电流不均衡问题。

40.以上所述实施方式仅仅是对本发明的优选实施方式进行描述,并非对本发明的范围进行限定,在不脱离本发明设计精神的前提下,本领域普通技术人员对本发明的技术方案作出的各种变形和改进,均应落入本发明的权利要求书确定的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1