主站控制器控制方法、装置、设备及存储介质与流程

1.本发明涉及电机控制技术领域,尤其涉及一种主站控制器控制方法、装置、设备及存储介质。

背景技术:

2.随着电子技术的发展,当前plc和运动控制器都在慢慢进入总线时代,ethercat(以太网控制自动化技术)总线是目前发展最好,配套最齐全的现场总线。自动化对通讯一般会要求较短的资料更新时间(或称为周期时间)、资料同步时的通讯抖动量低,而且硬件的成本要低,ethercat开发的目的就是让以太网可以运用在自动化应用中。

3.现有的方案中可以将ethercat总线应用于对电机的控制中,通过ethercat总线主站对总线电机进行控制,但由于脉冲控制的电机有很大的成本优势,因此也需要实现对脉冲电机的控制,然而为保证实时性脉冲控制一般由主站fpga芯片发出,而ethercat总线时钟必须基于从站实时调整,所以对于不使用操作系统的主站来说,脉冲电机控制和总线控制就必须基于两个不同基准时钟,一个基于fpga本地时钟,一个基于从站的本地时钟,因此无法实现对脉冲电机和总线电机的同时控制。

4.上述内容仅用于辅助理解本发明的技术方案,并不代表承认上述内容是现有技术。

技术实现要素:

5.本发明的主要目的在于提供了一种主站控制器控制方法、装置、设备及存储介质,旨在解决现有技术中无法实现对脉冲电机和总线电机进行同时控制的技术问题。

6.为实现上述目的,本发明提供了一种主站控制器控制方法,所述方法应用于主站控制器,所述主站控制器包括fpga芯片和cpu单元,所述fpga芯片和所述cpu单元之间通过内部并行数据总线连接,所述cpu单元通过以太网接口连接ethercat总线,所述方法包括:

7.所述fpga芯片生成总线周期中断和脉冲输出完成中断,并将所述总线周期中断和所述脉冲输出完成中断发送至所述cpu单元;

8.所述cpu单元在所述总线周期中断中获取主站系统时钟和从站系统时钟之间的时间差;

9.所述cpu单元在所述脉冲输出完成中断中获取周期规划数据,并将所述时间差和所述周期规划数据写入所述fpga芯片;

10.所述fpga芯片根据所述时间差和所述周期规划数据同时对总线和脉冲进行输出控制。

11.可选地,所述fpga芯片生成总线周期中断和脉冲输出完成中断,并将所述总线周期中断和所述脉冲输出完成中断发送至所述cpu单元的步骤之前,还包括:

12.所述fpga芯片生成系统时钟,并将所述系统时钟发送至cpu单元;

13.所述cpu单元在接收到所述系统时钟时,控制从站基于所述系统时钟将从站系统

时钟调整至主站系统时钟的目标范围内。

14.可选地,所述cpu单元在接收到所述系统时钟时,控制从站基于所述系统时钟将从站系统时钟调整至主站系统时钟的目标范围内的步骤,包括:

15.所述cpu单元接收到所述系统时钟时,基于所述系统时钟获取主站和从站之间的时钟偏移;

16.所述cpu单元将所述时钟偏移写入所述从站的时钟偏移寄存器,以使所述从站基于所述时钟偏移寄存器中存储的时钟偏移将从站系统时钟调整至主站系统时钟的目标范围内。

17.可选地,所述fpga芯片生成系统时钟,并将所述系统时钟发送至cpu单元的步骤之前,还包括:

18.所述fpga芯片接收晶振输入的时钟源,并通过锁相环将所述时钟源输出为目标时钟;

19.所述fpga芯片基于所述目标时钟和计数器生成目标时钟信号,并基于所述目标时钟信号生成总线周期中断。

20.可选地,所述fpga芯片基于所述目标时钟和计数器生成目标时钟信号,并基于所述目标时钟信号生成总线周期中断的步骤之后,还包括:

21.所述fpga芯片基于所述目标时钟信号生成总线定时器;

22.相应的,所述cpu单元在所述总线周期中断中获取主站系统时钟和从站系统时钟之间的时间差的步骤,包括:

23.所述cpu单元在所述总线周期中断中清除所述总线定时器的中断标志位以关闭所述总线定时器;

24.所述cpu单元在所述总线定时器关闭时,获取目标从站的从站本地时间和主站的主站本地时间;

25.所述cpu单元基于所述从站本地时间和所述主站本地时间获取主站系统时钟和从站系统时钟之间的时间差。

26.可选地,所述cpu单元基于所述从站本地时间和所述主站本地时间获取主站系统时钟和从站系统时钟之间的时间差的步骤之后,还包括:

27.所述cpu单元读取下一总线周期中断的中断触发时间,并基于所述中断触发时间、所述从站本地时间和所述主站本地时间确定所述总线定时器的重载计数值;

28.所述cpu单元将所述重载计数值写入所述总线定时器的周期计数器。

29.可选地,所述fpga芯片基于所述目标时钟和计数器生成目标时钟信号,并基于所述目标时钟信号生成总线周期中断的步骤之后,还包括:

30.所述fpga芯片基于所述目标时钟信号生成脉冲定时器;

31.相应的,所述fpga芯片根据所述时间差和所述周期规划数据同时对总线和脉冲进行输出控制的步骤之后,还包括:

32.所述fpga在所述脉冲定时器溢出时,基于所述周期规划数据发送当前周期的脉冲数据;

33.所述fpga在所述脉冲数据发送完成时,生成新的脉冲输出完成中断;

34.所述cpu单元在所述新的脉冲输出完成中断中获取下一周期规划数据,并将所述

下一周期规划数据写入所述fpga芯片。

35.此外,为实现上述目的,本发明还提出一种主站控制器控制装置,所述装置包括:

36.中断生成模块,用于生成总线周期中断和脉冲输出完成中断,并将所述总线周期中断和所述脉冲输出完成中断发送至所述cpu单元;

37.时间差获取模块,用于在所述总线周期中断中获取主站系统时钟和从站系统时钟之间的时间差;

38.数据写入模块,用于在所述脉冲输出完成中断中获取周期规划数据,并将所述时间差和所述周期规划数据写入所述fpga芯片;

39.输出控制模块,用于根据所述时间差和所述周期规划数据同时对总线和脉冲进行输出控制。

40.此外,为实现上述目的,本发明还提出一种主站控制器控制设备,所述设备包括:存储器、处理器及存储在所述存储器上并可在所述处理器上运行的主站控制器控制程序,所述主站控制器控制程序配置为实现如上文所述的主站控制器控制方法的步骤。

41.此外,为实现上述目的,本发明还提出一种存储介质,所述存储介质上存储有主站控制器控制程序,所述主站控制器控制程序被处理器执行时实现如上文所述的主站控制器控制方法的步骤。

42.在本发明中,公开了fpga芯片生成总线周期中断和脉冲输出完成中断,并将总线周期中断和脉冲输出完成中断发送至cpu单元;cpu单元在总线周期中断中获取主站系统时钟和从站系统时钟之间的时间差;在脉冲输出完成中断中获取周期规划数据,并将时间差和周期规划数据写入fpga芯片;fpga芯片根据时间差和周期规划数据同时对总线和脉冲进行输出控制;相较于现有技术中基于两个不同基准的时钟对脉冲电机和总线电机进行控制,导致无法进行同时控制,由于本发明的主站控制器包括fpga芯片和cpu单元,通过fpga芯片将生成的总线周期中断和脉冲输出完成中断发送至cpu单元,cpu单元将在总线周期中断中获取的主站系统时钟和从站系统时钟之间的时间差,以及在脉冲输出完成中断中获取的周期规划数据写入fpga芯片,使得fpga芯片根据时间差和周期规划数据同时对总线和脉冲进行输出控制,从而解决了现有技术中无法实现对脉冲电机和总线电机进行同时控制的技术问题。

附图说明

43.图1是本发明实施例方案涉及的硬件运行环境的主站控制器控制设备的结构示意图;

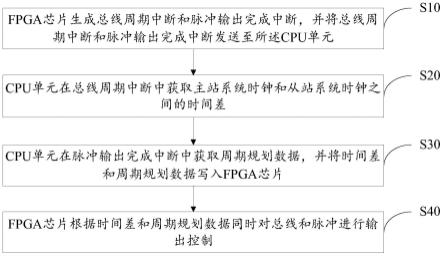

44.图2为本发明主站控制器控制方法第一实施例的流程示意图;

45.图3为本发明主站控制器控制方法第二实施例的流程示意图;

46.图4为本发明主站控制器控制方法第三实施例的流程示意图;

47.图5为本发明主站控制器控制方法第三实施例中脉冲输出完成中断的流程示意图;

48.图6为本发明主站控制器控制装置第一实施例的结构框图。

49.本发明目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

具体实施方式

50.应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

51.参照图1,图1为本发明实施例方案涉及的硬件运行环境的主站控制器控制设备结构示意图。

52.如图1所示,该主站控制器控制设备可以包括:处理器1001,例如中央处理器(central processing unit,cpu),通信总线1002、用户接口1003,网络接口1004,存储器1005。其中,通信总线1002用于实现这些组件之间的连接通信。用户接口1003可以包括显示屏(display)、输入单元比如键盘(keyboard),可选用户接口1003还可以包括标准的有线接口、无线接口。网络接口1004可选的可以包括标准的有线接口、无线接口(如无线保真(wireless-fidelity,wi-fi)接口)。存储器1005可以是高速的随机存取存储器(random access memory,ram),也可以是稳定的非易失性存储器(non-volatile memory,nvm),例如磁盘存储器。存储器1005可选的还可以是独立于前述处理器1001的存储装置。

53.本领域技术人员可以理解,图1中示出的结构并不构成对主站控制器控制设备的限定,可以包括比图示更多或更少的部件,或者组合某些部件,或者不同的部件布置。

54.如图1所示,作为一种存储介质的存储器1005中可以包括操作系统、网络通信模块、用户接口模块以及主站控制器控制程序。

55.在图1所示的主站控制器控制设备中,网络接口1004主要用于与网络服务器进行数据通信;用户接口1003主要用于与用户进行数据交互;本发明主站控制器控制设备中的处理器1001、存储器1005可以设置在主站控制器控制设备中,所述主站控制器控制设备通过处理器1001调用存储器1005中存储的主站控制器控制程序,并执行本发明实施例提供的主站控制器控制方法。

56.本发明实施例提供了一种主站控制器控制方法,参照图2,图2为本发明主站控制器控制方法第一实施例的流程示意图。

57.本实施例中,所述主站控制器控制方法应用于主站控制器,所述主站控制器包括fpga芯片和cpu单元,所述fpga芯片和所述cpu单元之间通过内部并行数据总线连接,所述cpu单元通过以太网接口连接ethercat总线,包括以下步骤:

58.步骤s10:所述fpga芯片生成总线周期中断和脉冲输出完成中断,并将所述总线周期中断和所述脉冲输出完成中断发送至所述cpu单元。

59.需要说明的是,本实施例中将ethercat总线通过以太网接口连接至cpu单元,且由于脉冲控制一般由主站fpga芯片发出,再将fpga芯片和cpu单元之间通过内部并行数据总线连接,从而可以集成ethercat总线和脉冲控制在一个控制器主站上,主站既可以包含脉冲输出用于控制电机(以脉冲信号控制的驱动器如步进电机、伺服等),也可以包含ethercat总线控制。

60.应当理解的是,上述fpga芯片中fpga的全称为field-programmable gate array,fpga芯片是一种万能数字芯片,具有模拟绝大部分数字逻辑芯片的功能。

61.可以理解的是,上述总线周期中断可以为用于修正主站和从站的dc同步信号,防止同步信号丢失的中断,其中,dc同步信号可以为在主站上自定义的一个时间同步触发事件信号,用以给需要同步处理信息的机器设备提供相同时间参考。

62.需要说明的是,上述脉冲输出完成中断可以为用于规划脉冲输出频率和个数等数

据的中断。

63.在具体实现中,fpga芯片可以通过生成定时器,并在生成定时器后定时生成总线周期中断和脉冲输出完成中断,fpga芯片再通过io信号线将总线周期中断和脉冲输出完成中断分发给cpu,cpu通过外部中断响应对应的中断线。

64.步骤s20:所述cpu单元在所述总线周期中断中获取主站系统时钟和从站系统时钟之间的时间差。

65.需要说明的是,上述主站系统时钟可以为主站的时钟,上述从站系统时钟可以为从站的时钟。实际应用中,ethercat总线实时性主要使用分布时钟来保证,每个从站有自己的本地时钟,主站也有自己的本地时钟。

66.应当理解的是,上述时间差可以为主站本地时钟和从站本地时钟之间的差值。

67.在具体实现中,cpu单元可以通过外部中断响应总线周期中断,在中线周期中断中与所有从站交互rxpdo和txpdo等总线周期数据,并计算主站本地时钟和从站本地时钟之间的时间差。

68.步骤s30:所述cpu单元在所述脉冲输出完成中断中获取周期规划数据,并将所述时间差和所述周期规划数据写入所述fpga芯片。

69.可以理解的是,上述周期规划数据可以为cpu计算的fpga芯片下一周期需要发送的脉冲频率和脉冲个数等数据。实际应用中,cpu在接收到脉冲输出完成中断信号后,计算fpga芯片下一个周期的规划数据,如速度和加速度等,然后写入下一个周期需要发送的脉冲频率和脉冲个数至fpga芯片的寄存器中。

70.步骤s40:所述fpga芯片根据所述时间差和所述周期规划数据同时对总线和脉冲进行输出控制。

71.需要说明的是,由于本实施例将ethercat总线和脉冲控制集成在主站控制器中,并通过fpga芯片产生两路中断,在解决脉冲控制同步性要求的同时,也满足ethercat总线控制时钟要求,从而可以同时对总线和脉冲进行输出控制。

72.在具体实现中,首先可以将fpga芯片和cpu通过cpu自带的并行数据总线连接,并将cpu和ethercat总线通过以太网接口连接,fpga芯片生成总线周期中断和脉冲输出完成中断后可以通过io信号线分发给cpu,cpu再通过外部中断响应对应的总线周期中断和脉冲输出完成中断,在总线周期中断中和所有从站交互rxpdo和txpdo等总线周期数据,并计算主站本地时钟和从站本地时钟之间的时间差;在脉冲输出完成中断中,规划下一次脉冲输出频率和脉冲输出个数等周期规划数据,并将时间差、脉冲输出频率和脉冲输出个数等数据写入到fpga芯片中,以通过时间差修正下一次总线周期中断触发时间,通过脉冲输出频率和脉冲输出个数等周期规划数据控制脉冲输出,从而实现同时对总线和脉冲进行输出控制。

73.本实施例公开了fpga芯片生成总线周期中断和脉冲输出完成中断,并将总线周期中断和脉冲输出完成中断发送至cpu单元;cpu单元在总线周期中断中获取主站系统时钟和从站系统时钟之间的时间差;在脉冲输出完成中断中获取周期规划数据,并将时间差和周期规划数据写入fpga芯片;fpga芯片根据时间差和周期规划数据同时对总线和脉冲进行输出控制;相较于现有技术中基于两个不同基准的时钟对脉冲电机和总线电机进行控制,导致无法进行同时控制,由于本实施例的主站控制器包括fpga芯片和cpu单元,通过fpga芯片

将生成的总线周期中断和脉冲输出完成中断发送至cpu单元,cpu单元将在总线周期中断中获取的主站系统时钟和从站系统时钟之间的时间差,以及在脉冲输出完成中断中获取的周期规划数据写入fpga芯片,使得fpga芯片根据时间差和周期规划数据同时对总线和脉冲进行输出控制,从而解决了现有技术中无法实现对脉冲电机和总线电机进行同时控制的技术问题,此外,ethercat总线基于从站时钟进行同步,主站调整自己的时钟同步到从站时钟,从而可以在不使用操作系统的情况下,产生ethercat总线系统时钟。

74.参考图3,图3为本发明主站控制器控制方法第二实施例的流程示意图。

75.基于上述第一实施例,为了对主站系统时钟进行修正,本实施例中,所述步骤s10之前,所述方法还包括:

76.步骤s01:fpga芯片生成系统时钟,并将所述系统时钟发送至cpu单元。

77.需要说明的是,上述系统时钟可以为用于对ethercat总线进行时钟同步、修正从站系统时钟到主站系统时钟上的时钟。其中,系统时钟为48位时间,低16位表示微秒时间,范围为0-99999微秒,高16位表示秒为单位,从而可以实现最大超过136年的计时单位。

78.步骤s02:cpu单元在接收到所述系统时钟时,控制从站基于所述系统时钟将从站系统时钟调整至主站系统时钟的目标范围内。

79.应当理解的是,上述目标范围内可以为从站系统时钟与主站系统时钟较为接近的范围,具体的范围大小本实施例不加以限制。

80.可以理解的是,上述系统时钟可以用于主站在dc(distributed clock,分布式时钟)配置时,计算主站和dc从站(即支持分布式时钟的从站)的时钟偏移,从而将所有dc从站同步到该主站系统时钟范围内,其中,分布式时钟可以使所有的ethercat总线设备使用相同的系统时间,从而控制各设备任务的同时执行。

81.需要说明的是,为了将从站系统时钟调整至主站系统时钟的目标范围内,上述步骤s02包括:cpu单元接收到所述系统时钟时,基于所述系统时钟获取主站和从站之间的时钟偏移;cpu单元将所述时钟偏移写入所述从站的时钟偏移寄存器,以使所述从站基于所述时钟偏移寄存器中存储的时钟偏移将从站系统时钟调整至主站系统时钟的目标范围内。

82.应当理解的是,上述时钟偏移寄存器可以为从站中用于保存本地时钟和总线时钟的差值的寄存器。

83.在具体实现中,从站会存在一个时间偏移,若从站在出厂时写入的时间为2000年01月01日17时23分06秒,但此时主站的时间可能为2022年11月20日11时48分52秒,则需要针对这两个时间对主站和从站进行对表,获得主站和从站之间的时钟偏移,并将这个时钟偏移写入从站的时钟偏移寄存器中,然后从站中的寄存器基于原来的时间再加上这个时钟偏移后就形成了现在的时间,即将从站系统时钟调整至主站系统时钟的目标范围内。

84.本实施例通过cpu单元在接收到fpga芯片生成的系统时钟时,基于系统时钟获取主站和从站之间的时钟偏移,并将时钟偏移写入从站的时钟偏移寄存器,以使从站基于时钟偏移寄存器存储的时钟偏移将从站系统时钟调整至主站系统时钟的目标范围内,从而可以对ethercat总线进行时钟同步、修正从站系统时钟到主站系统时钟上,实现了主站和从站的初步同步。

85.参考图4,图4为本发明主站控制器控制方法第三实施例的流程示意图。

86.基于上述各实施例,为了使fpga芯片生成总线周期中断,本实施例中,所述步骤

s10之后,所述方法还包括:

87.步骤s011:fpga芯片接收晶振输入的时钟源,并通过锁相环将所述时钟源输出为目标时钟。

88.需要说明的是,上述锁相环(phase locked loop,pll)为辅助产生时钟信号的器件,将时钟信号输入锁相环后,锁相环可以将这个时钟信号的频率按照指定倍率提高之后再输出。

89.应当理解的是,上述目标时钟可以为由晶振提供的时钟源经过锁相环后输出的时钟,例如25m晶振经过锁相环后输出100m时钟。

90.步骤s012:fpga芯片基于所述目标时钟和计数器生成目标时钟信号,并基于所述目标时钟信号生成总线周期中断。

91.可以理解的是,上述目标时钟信号可以为fpga锁相环输出时钟后由计数器产生的时钟信号。

92.应当理解的是,在生成目标时钟信号后,fpga可以通过计数器生成定时器,生成定时器后可以定时给中断,即可以生成总线周期中断。

93.在具体实现中,若fpga芯片接收25m晶振输入的时钟源,经过锁相环后输出100m时钟,则计数器可以为100m时钟进行计算,例如对100m时钟计数一百次,从而产生1m时钟源,即1us时钟信号(上述目标时钟信号)。

94.进一步地,为了获取主站系统时钟和从站系统时钟之间的时间差,上述步骤s012之后还包括:fpga芯片基于所述目标时钟信号生成总线定时器;相应的,上述步骤s20包括:cpu单元在所述总线周期中断中清除所述总线定时器的中断标志位以关闭所述总线定时器;cpu单元在所述总线定时器关闭时,获取目标从站的从站本地时间和主站的主站本地时间;cpu单元基于所述从站本地时间和所述主站本地时间获取主站系统时钟和从站系统时钟之间的时间差。

95.需要说明的是,上述总线定时器可以为ethercat总线对应的定时器。

96.应当理解的是,fpga芯片可以通过计数器生成总线定时器,并通过总线定时器输出总线周期中断至cpu,cpu可以在总线周期中断中实现主站周期刷新数据和从站系统时钟的同步。

97.在具体实现中,由于主站时钟的精度没有从站时钟的精度高,因此在将从站系统时钟调整至主站系统时钟的目标范围内后,要以从站时间为基准对主站时间进行调整,因此需要获取主站系统时钟和从站系统时钟之间的时间差,从而基于时间差对主站时间进行调整,此时可以进入总线定时器中断中,清除总线定时器的中断标志位以停止定时器,并获取主站系统时钟和从站系统时钟之间的时间差。

98.可以理解的是,上述步骤s20之后还包括:cpu单元读取下一总线周期中断的中断触发时间,并基于所述中断触发时间、所述从站本地时间和所述主站本地时间确定所述总线定时器的重载计数值;cpu单元将所述重载计数值写入所述总线定时器的周期计数器。

99.需要说明的是,上述中断触发时间可以为总线周期中断下一次触发的时间。

100.应当理解的是,上述重载计数值可以为总线定时器下一次触发中断的时间。通过将重载计数值写入总线定时器的周期计数器可以修正主站和从站的同步信号。

101.在具体实现中,若通过主站系统时钟和从站系统时钟发现此时主站时间比从站时

间快1ms,则可以将fpga芯片的总线定时器停下来,等待1ms后再继续工作,若主站时间比从站时间慢,则可以将总线定时器的时间加一点,通过不停地调整定时器的周期可以使主站和从站的时间维持在一个精度范围内,在将重载计数值写入定时器的周期计数器后可以启动定时器中断,并刷新rxpdo和txpdo等总线周期数据。

102.进一步地,为了在脉冲定时器溢出时获取fpga芯片的下一个周期的周期规划数据,上述步骤s012之后还包括:fpga芯片基于所述目标时钟信号生成脉冲定时器;相应的,上述步骤s40之后,还包括:fpga在所述脉冲定时器溢出时,基于所述周期规划数据发送当前周期的脉冲数据;fpga在所述脉冲数据发送完成时,生成新的脉冲输出完成中断;cpu单元在所述新的脉冲输出完成中断中获取下一周期规划数据,并将所述下一周期规划数据写入所述fpga芯片。

103.需要说明的是,脉冲输出主要由fpga芯片进行,脉冲精度越高对电机控制越精准,脉冲衔接越平滑,电机运行越平稳,这就要求脉冲控制中断周期的精度越高越好,因此需要对fpga芯片输出的脉冲频率和脉冲个数等数据进行规划。

104.在具体实现中,如图5所示,图5为本发明主站控制器控制方法第三实施例中脉冲输出完成中断的流程示意图,fpga芯片在脉冲定时寄存器溢出时,会先将cpu写入的脉冲缓冲区数据压入脉冲输出寄存器,并开始发送当前周期指定频率和个数的脉冲数据,防止造成脉冲不连续的问题,然后产生定时中断信号(即脉冲输出完成中断)给cpu,cpu收到该中断信号后,计算下一个周期的规划数据,如速度、加速度等,然后写入下一周期需要发送的脉冲频率和脉冲个数至fpga脉冲缓存寄存器,最后等待下一次中断的到来。

105.本实施例中fpga芯片通过锁相环将接收的晶振输入的时钟源输出为目标时钟,并基于目标时钟和计数器生成的目标时钟信号生成总线周期中断,同时,fpga芯片基于目标时钟信号生成总线定时器,cpu单元再基于下一总线周期中断的中断触发时间、从站本地时间和主站本地时间确定总线定时器的重载计数值,并将重载计数值写入总线定时器的周期计数器,从而可以通过总线定时器修正主站和从站的dc同步信号,提高同步精度,防止同步信号丢失。

106.此外,本发明实施例还提出一种存储介质,所述存储介质上存储有主站控制器控制程序,所述主站控制器控制程序被处理器执行时实现如上文所述的主站控制器控制方法的步骤。

107.参照图6,图6为本发明主站控制器控制装置第一实施例的结构框图。

108.如图6所示,本发明实施例提出的主站控制器控制装置包括:

109.中断生成模块601,用于生成总线周期中断和脉冲输出完成中断,并将所述总线周期中断和所述脉冲输出完成中断发送至所述cpu单元;

110.时间差获取模块602,用于在所述总线周期中断中获取主站系统时钟和从站系统时钟之间的时间差;

111.数据写入模块603,用于在所述脉冲输出完成中断中获取周期规划数据,并将所述时间差和所述周期规划数据写入所述fpga芯片;

112.输出控制模块604,用于根据所述时间差和所述周期规划数据同时对总线和脉冲进行输出控制。

113.本实施例的主站控制器控制装置公开了fpga芯片生成总线周期中断和脉冲输出

完成中断,并将总线周期中断和脉冲输出完成中断发送至cpu单元;cpu单元在总线周期中断中获取主站系统时钟和从站系统时钟之间的时间差;在脉冲输出完成中断中获取周期规划数据,并将时间差和周期规划数据写入fpga芯片;fpga芯片根据时间差和周期规划数据同时对总线和脉冲进行输出控制;相较于现有技术中基于两个不同基准的时钟对脉冲电机和总线电机进行控制,导致无法进行同时控制,由于本实施例的主站控制器包括fpga芯片和cpu单元,通过fpga芯片将生成的总线周期中断和脉冲输出完成中断发送至cpu单元,cpu单元将在总线周期中断中获取的主站系统时钟和从站系统时钟之间的时间差,以及在脉冲输出完成中断中获取的周期规划数据写入fpga芯片,使得fpga芯片根据时间差和周期规划数据同时对总线和脉冲进行输出控制,从而解决了现有技术中无法实现对脉冲电机和总线电机进行同时控制的技术问题,此外,ethercat总线基于从站时钟进行同步,主站调整自己的时钟同步到从站时钟,从而可以在不使用操作系统的情况下,产生ethercat总线系统时钟。

114.本发明主站控制器控制装置的其他实施例或具体实现方式可参照上述各方法实施例,此处不再赘述。

115.需要说明的是,在本文中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者系统不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者系统所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该要素的过程、方法、物品或者系统中还存在另外的相同要素。

116.上述本发明实施例序号仅仅为了描述,不代表实施例的优劣。

117.通过以上的实施方式的描述,本领域的技术人员可以清楚地了解到上述实施例方法可借助软件加必需的通用硬件平台的方式来实现,当然也可以通过硬件,但很多情况下前者是更佳的实施方式。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质(如只读存储器/随机存取存储器、磁碟、光盘)中,包括若干指令用以使得一台终端设备(可以是手机,计算机,服务器,或者网络设备等)执行本发明各个实施例所述的方法。

118.以上仅为本发明的优选实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1