一种低待机能耗的电源电路及电视机的制作方法

本发明涉及开关电源术领域,更加具体来说,本发明涉及一种低待机能耗的电源电路及电视机。

背景技术:

1、根据gb/t8170相关条款规定,电视机整机待机功耗要求≤0.5w,电视机在待机状态下,主要耗能模块包括主板5vdcdc电路,主板mcu,电源模块(处于低功耗状态),由于主板的5vdcdc电路是mcu的供电电路,所以不能在待机时切断该电路,主板mcu在待机状态下需要保持唤醒功能,否则无法开机,所以待机时mcu也必须处于工作状态,以上两个模块无法从中降低整机待机功耗。一般情况下,待机状态下主板消耗功率大概0.19w左右,因此,需要考虑如何降低电源模块待机状态下耗以满足待机能耗需求。

2、现有技术中解决待机能耗的方法通常有加大vcc启动电阻阻值或者采用burstmode的电源芯片等方法,但是,加大vcc启动电阻阻值会导致开机时间过长,而采用burstmode的电源芯片,容易在待机时变压器有响声,且待机时给电视主板供电的电压纹波较大。可见上述两种方式的降低待机功耗的效果并不理想。

技术实现思路

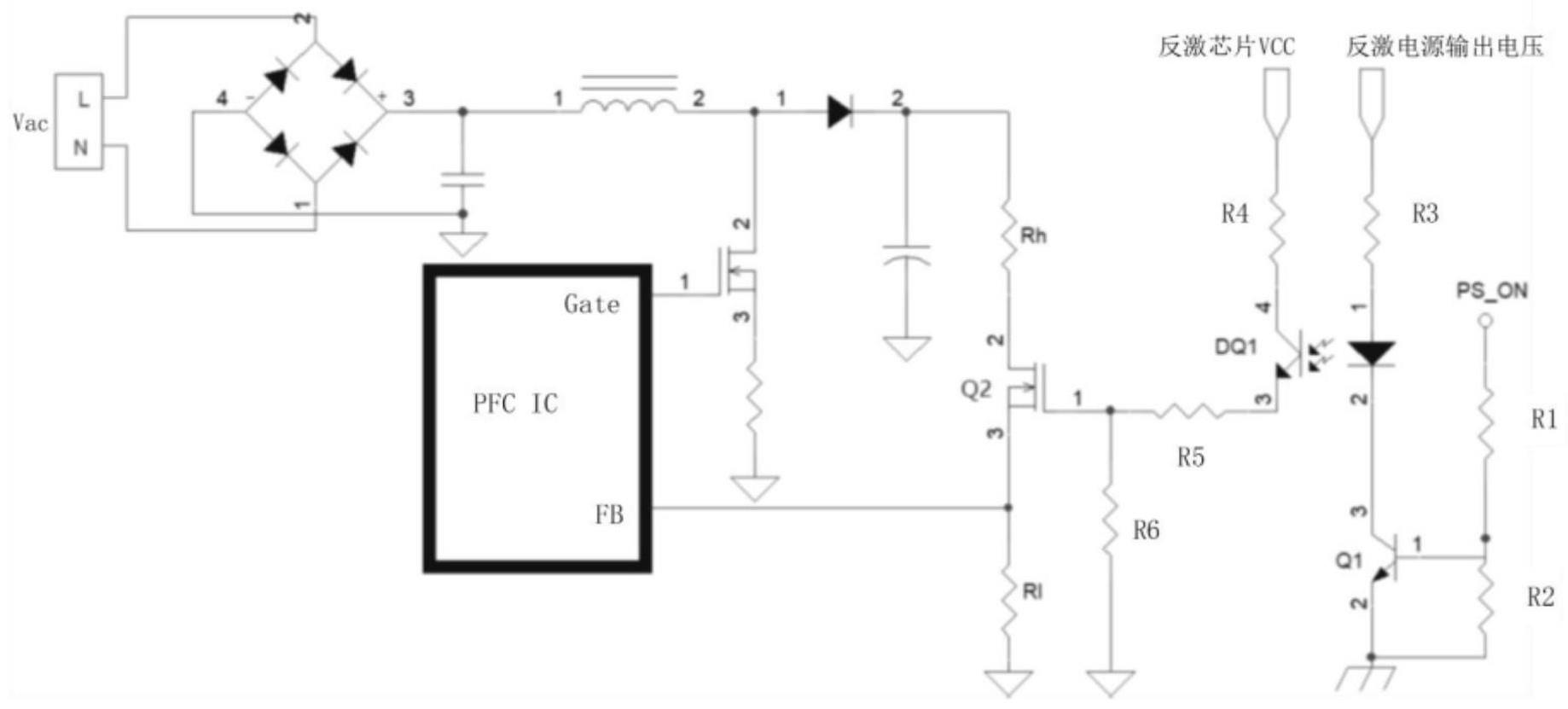

1、针对现有技术的不足,本发明创新地提供了一种低待机能耗的电源电路及电视机,能够解决现有技术中在待机状态时pfc的取样电阻耗能导致的待机能耗高的技术问题。

2、为实现上述的技术目的,本发明第一方面公开了一种低待机能耗的电源电路,包括:

3、pfc电路,用于输出pfc输出电压;

4、pfc输出电压的取样电路;

5、控制电路,用于控制所述取样电路的通断,其中,所述控制电路用于接收待机信号,在接收到开机信号时将所述取样电路连通,在接收到待机信号时将所述取样电路断开。

6、进一步地,所述取样电路包括:上拉电阻rh和下拉电阻rl,所述上拉电阻rh和下拉电阻rl串联,所述控制电路连接在所述上拉电阻rh和下拉电阻rl之间。

7、进一步地,所述控制电路与反激电路连接,由所述反激电路为所述控制电路供电。

8、进一步地,所述控制电路与开机电源连接并接收所述开机电源的待机信号,当接收到高电平信号时为开机信号,当接收到低电平信号时为待机信号。

9、进一步地,所述控制电路包括:

10、第一开关,连接于所述上拉电阻rh与所述下拉电阻rl之间;

11、光耦,所述光耦的输出端与所述第一开关的控制端连接,用于在所述光耦导通时,将所述第一开关导通,在所述光耦关断时,将所述第一开关关断;

12、第二开关,与所述光耦的输入端连接,用于接收待机信号,在接收到开机信号时,将所述光耦与光耦电源导通,在接收到待机信号时,将所述光耦与光耦电源关断。

13、进一步地,

14、所述第一开关为mos管,所述第二开为三极管,其中,

15、所述mos管的漏极与所述上拉电阻rh连接,所述mos管的源极与所述下拉电阻rl连接,所述光耦的内部受光三极管的发射极与所述mos管的栅极连接;

16、所述光耦的内部发光二极管的阴极与所述三极管的集电极连接,所述三极管的基极与开机电源连接,所述三极管的发射极接地。

17、进一步地,所述三极管的基极与所述开机电源之间串联有第一电阻r1,

18、所述三极管的基极还连接有与所述第一电阻r1并联的第二电阻r2,所述第二电阻r2接地。

19、进一步地,所述光耦的内部的发光二极管的阳极连接有第三电阻r3,

20、所述光耦的内部受光三极管的集电极连接有第四电阻r4。

21、进一步地,所述光耦的内部受光三极管的发射极与所述mos管的栅极之间串联有第五电阻r5,

22、所述第五电阻r5和所述mos管的栅极之间并联有第六电阻r6,所述第六电阻r6接地。

23、本发明第二方面公开了一种电视机,包括上述低待机能耗的电源电路。

24、本发明的有益效果为:

25、本发明提供的低待机能耗的电源电路通过电视机的待机信号控制pfc取样电路的通断,既不会影响电视机开机时电源的正常工作,又能够达到降低电视机待机能耗的效果。并且,本发明电路简单,便于推广实施。

技术特征:

1.一种低待机能耗的电源电路,其特征在于,包括:

2.根据权利要求1所述的低待机能耗的电源电路,其特征在于,所述取样电路包括:上拉电阻rh和下拉电阻rl,所述上拉电阻rh和下拉电阻rl串联,所述控制电路连接在所述上拉电阻rh和下拉电阻rl之间。

3.根据权利要求1或2所述的低待机能耗的电源电路,其特征在于,所述控制电路与反激电路连接,由所述反激电路为所述控制电路供电。

4.根据权利要求1或2所述的低待机能耗的电源电路,其特征在于,所述控制电路与开机电源连接并接收所述开机电源的待机信号,当接收到高电平信号时为开机信号,当接收到低电平信号时为待机信号。

5.根据权利要求2所述的低待机能耗的电源电路,其特征在于,所述控制电路包括:

6.根据权利要求5所述的低待机能耗的电源电路,其特征在于,

7.根据权利要求6所述的低待机能耗的电源电路,其特征在于,所述三极管的基极与所述开机电源之间串联有第一电阻r1,

8.根据权利要求7所述的低待机能耗的电源电路,其特征在于,所述光耦的内部的发光二极管的阳极连接有第三电阻r3,

9.根据权利要求8所述的低待机能耗的电源电路,其特征在于,所述光耦的内部受光三极管的发射极与所述mos管的栅极之间串联有第五电阻r5,

10.一种电视机,其特征在于,包括权利要求1-9任一项所述的低待机能耗的电源电路。

技术总结

本发明公开了一种低待机能耗的电源电路及电视机。低待机能耗的电源电路包括:PFC电路,用于输出PFC输出电压;PFC输出电压的取样电路;控制电路,用于控制所述取样电路的通断,其中,所述控制电路用于接收待机信号,在接收到开机信号时将所述取样电路连通,在接收到待机信号时将所述取样电路断开。本发明提供的低待机能耗的电源电路通过电视机的待机信号控制PFC取样电路的通断,既不会影响电视机开机时电源的正常工作,又能够达到降低电视机待机能耗的效果。并且,本发明电路简单,便于推广实施。

技术研发人员:卢洪权

受保护的技术使用者:康佳集团股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!